一,ECL邏輯電平

由于TTL電路的晶體管(BJT)在電壓轉換過程中分別工作在“飽和狀態”和“截止狀態”,使得切換速度受到了很大的限制(PN結大電流模式下,存在較大的擴散電容,導致反向恢復時間較長,具體參考《關于PN結的那些事》和《三極管基礎》相關章節內容);雖然STTL電路采用了肖特基鉗位晶體管和新工藝,抑制了晶體管的過飽和及寄生電容,使得電路的速度進一步得到了提升,但仍然沒有完全擺脫“飽和”這一工作狀態。

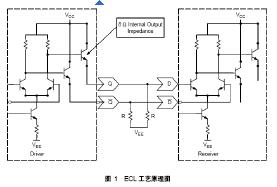

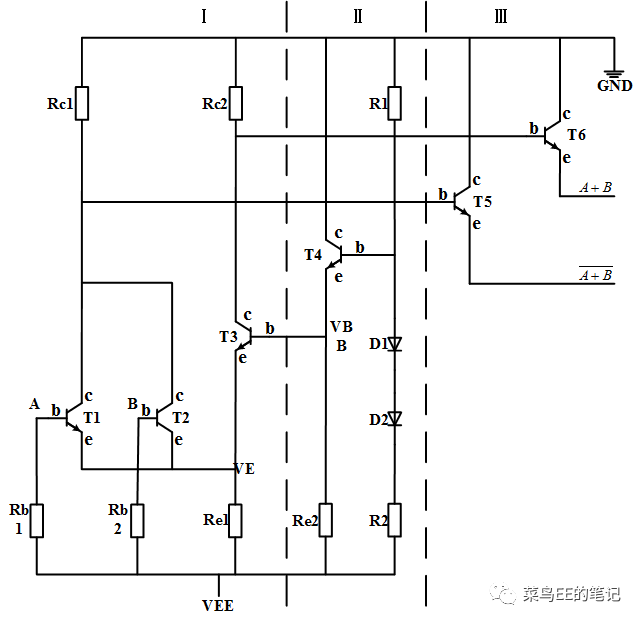

ECL結構輸出的工作原理,我們已在《邏輯門電路高速特性》中做了部分介紹;ECL電路(Emitter Coupled Logic):發射極耦合邏輯電路與TTL/CMOS不同,是一種非飽和型的數字邏輯電路。如下圖所示,其電路內部的晶體管(BJT)工作在線性區(非飽和區)或截止區,從根本上消除了限制速度提高的少數載流子的存儲時間(無擴散電容,反向恢復時間短)。因此,它是現有各種邏輯電路中速度最快的電路形式,電路平均延時可以做到亞ns級別。

1,ECL基本電路結構

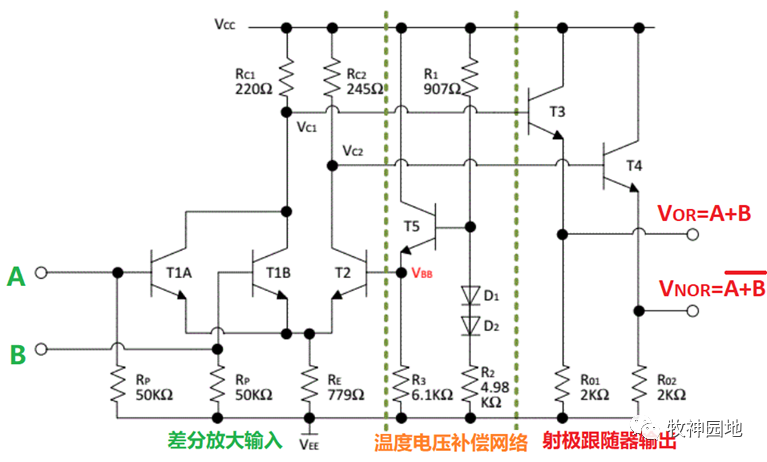

典型的基本ECL門電路(單端)的輸出結構由三部分組成:差分放大器輸入電路,溫度-電壓補償偏壓網絡以及射極跟隨器輸出電路;具體結構如下圖所示。

- 差分放大器輸入電路(射極耦合電流開關):由T1A、T1B、T2管、Rc1、Rc2和RE組成了射極耦合電流開關,這是ECL電路的核心部分,其中T2管為定偏管,從Vc1和Vc2獲得或/或非輸出;

1, 關于VNOR管腳輸出電平的分析:

(1)A或B為高電平時:Vc1為低電平,T3被關斷, T3輸出輸出端下拉至VEE;

(2)A和B都為低電平時:Vc1為低電平, T3導通,T3輸出端上拉至Vcc;

(3)可得T3端管腳輸出電平邏輯關系:VNOR = /(A+B)。

2, 關于VOR管腳輸出電平的分析:

(1)A或B為高電平, T1A或T1B被打開,其電流通過電阻RE至VEE,此時T2的E極與VEE之間產生一個壓降(即VE >VEE),T2管的VBE (VBB和VE電壓)不足以將T2打開,Vc2為高電平,T4導通,T4輸出端上拉至Vcc;

(2)A和B都為低電平時,T4輸出端才為低電平,T2的E極電壓為VEE,T2管導通,Vc2為低電平,T4關斷,T4輸出端下拉至VEE;

(3)得T4端管腳輸出電平邏輯關系:VOR = A+B。

——根據輸入T1導通或T2導通,構成電流開關。

- 溫度-電壓補償偏壓網絡(參考電壓源):由T5、D1、D2、R1~R3構成參考電壓源,為T2提供固定的基極偏置電壓VBB;

——VBB電壓是判斷T2是否能打開的關鍵,需要在不同電壓以及溫度下實現一個穩定的偏置。

- 射極跟隨器輸出電路(射極開路輸出):T3、T4為射極開路的射極輸出器,作為電路的輸出級,解決輸入與輸出電平匹配問題;射極跟隨器的作用如下:

——不論是T3或則T4導通,所形成的發射極電流IE都很接近,該電流受Vc1和Vc2控制,就像一個電流開關。

1, 保持輸出相位不變,邏輯關系不變;

2, 實現輸出電平的位移,防止輸入晶體管飽和,使輸入、輸出電平匹配;

3, 射極跟隨器輸出阻抗低,提高了負載能力。

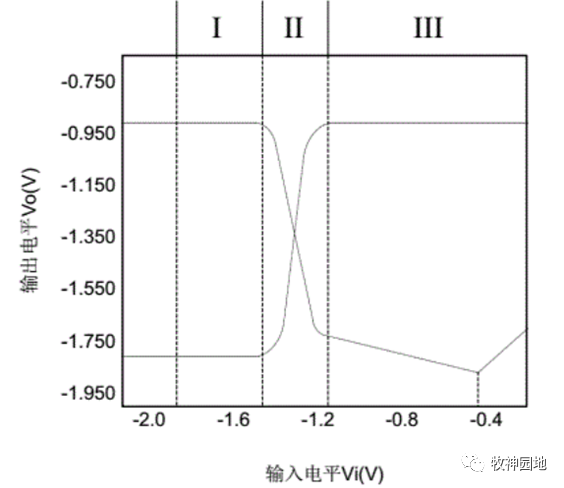

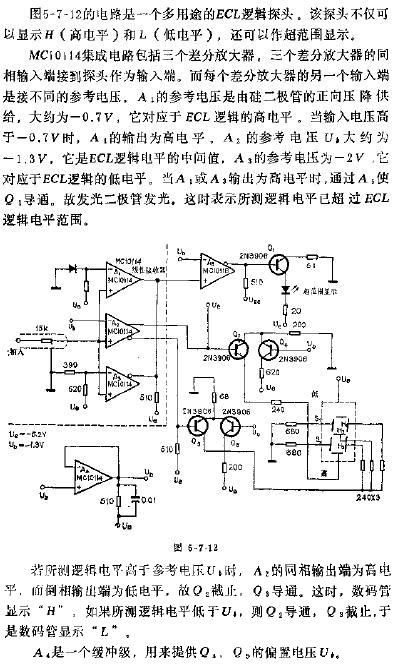

2,ECL電平分析

如之前章節所述,一般情況下ECL電路的負電源為-5.2V,而Vcc為GND(0V);其典型邏輯低電平VOL ≈ -1.72V,邏輯高電平VOH ≈ -0.88V,而VBB ≈ -1.30V為邏輯電平的中間值;VIH ≈ -1.24V,VIL ≈ -1.36V。

當輸入端從-1.72V跳變為-0.88V(由0變為1),Vc1由0V變為-0.88V,而此時Vc2由-0.88V變為0V(由0變為1),即定偏管T2同相輸出;如下圖所示。

——T1和T2起到了反相器的作用。

隨著技術的發展,又出現了LVECL邏輯電平器件,它是將電源由VEE = -5.2V調整為 -3.3V 或者是 -2.5V,這樣做的目的是降低器件的功耗,利于電路設計的器件的互連。由于Vcc電平為地電平(0V)未變,而其它的電平是相對于此電平的,所以其他的電平值(VBB、VOH、VOL、VIH、VIL)也都沒有改變。

3,ECL電路特性

ECL 電路是根據高速噪聲數字的應用要求設計的,它具有以下獨特的優點:

- 速度快:這是高速數字系統設計者廣泛采用ECL電路的一個重要原因,ECL基本門電路的典型傳輸延遲時間已達到亞ns量級;

——ECL系統與等效的TTL系統相比,其工作速度至少快一倍以上。

- 邏輯功能強:ECL電路能提供互補邏輯輸出,這樣不僅可以節省系統所用的組件數,減小系統功耗,而且由于互補邏輯輸出具有相同的傳輸延遲時間,因此可以消除一般邏輯電路中為產生互補邏輯功能而設置反相器所增加的時間延遲,進而提高了系統的速度;

- 驅動能力很強,扇出能力高:ECL電路是射極跟隨器輸出,驅動能力很強;

——其輸入阻抗高(約10KΩ),輸出阻抗低(約7Ω),允許電路有很高的扇出能力。

- 噪聲低:系統噪聲的大小直接與噪聲源的能量、邏輯的消噪性能和互連線的阻抗等有關。就噪聲的產生來說,ECL電路的內部噪聲較小;

- 便于數據傳輸:ECL電路具有互補、大電流驅動能力輸出,特別適合于以差分方式驅動和接收傳輸線上的信號;ECL電路的差分線接收器具有1V或者更大的共態噪聲抑制能力;

——相比于單端信號,串擾耦合到差分線(緊耦合)上的噪聲一般都是等同地出現在該差分線的每條線上(具體原理參考:《特殊的串擾-差分信號》相關章節),而接收器只響應兩條線上的電壓差,所以可大大抑制引線串擾的影響,從而易于實現遠距離的數據傳輸。

——驅動同軸電纜時,其距離只受電纜頻帶寬度的限制,而且可以改善系統的性能,驅動雙絞線的長度可以在約 300m( 1000f t) 以上,并且較同軸電纜經濟。

但ECL邏輯門電路在工作過程中:1,晶體管(BJT)工作在線性區;2,每對開關管是輪流導通的,對整個電路結構來說沒有“截止”狀態;ECL電路結構相對TTL來說損耗更大(傳輸功耗更高)。從某種意義上來說,ECL電路開關速度的提高是以犧牲功耗換取來的。

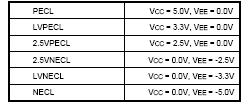

二,PECL/LVPECL 邏輯電平

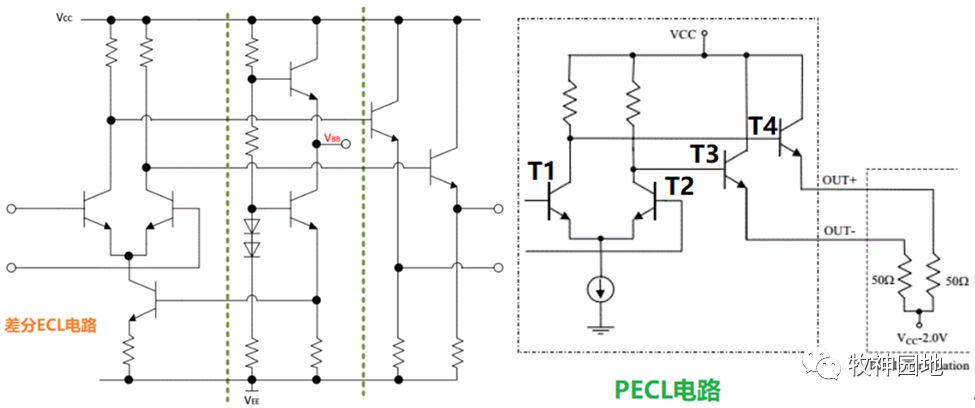

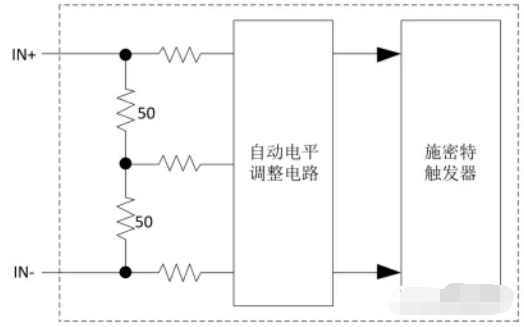

ECL電路中采用了負電源(-5.2V),顯然這與我們現在的一般硬件電源系統不匹配。所以如果去掉ECL電路中的負電源,采用正電源系統(+5V),那么我們就可以將Vcc接至+5V,而VEE接至GND;這樣的電平被稱為PECL:Positive Emitter Coupled Logic。那如果將Vcc改為+3.3V,那么就稱為LVPECL。當然,此時的高、低電平的定義是不同的。

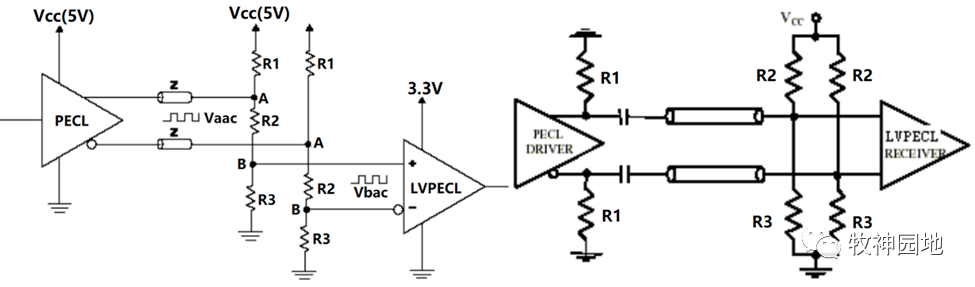

如下圖所示,左側為差分ECL電路,右側為PECL電路;雖然只是將負電源改為了正電源,但其結構發生了很大的變化。

- 輸入端:PECL電路直接是差分輸入的形式與差分ECL電路類似;而非ECL電路的取或非和或的結構;

——可能源于ECL的優勢在于差分信號上,所以PECL直接定位為差分而無單端應用場景。

- PECL電路取消了溫度-電壓補償網絡,增加了50Ω端接至Vcc-2V電壓。

——如下右圖所示,當T1端輸入為高(VIHmax = Vcc-1.16),為使得T1不進入飽和區,則T1的集電極(C極)電壓最小為VCC-1.3V(VBB = Vcc– 1.3V),為了使輸出的三極管T4不進入截止區,則其偏置電壓不應大于VCC-2V(T4的VBE = 0.7V),偏置電壓取VCC-2V是為了避免器件功耗過大。

——PECL輸出電平平均值VBB ≈ 3.7V(即Vcc – 1.3V),所以端接50Ω至Vcc-2V時輸出的直流約14mA。

1,PECL/LVPECL電平特點

PECL由于采用了單正電源系統,所以應用比ECL更加廣泛,而LVPECL使用3.3V或更低電壓電源供電,相比更具有低功耗的優勢。PECL電平電壓參數如下圖所示。

- 對于PECL電平,其各電壓參數如下:

1, Vcc = 5V,VEE = 0V,VBB ≈ 3.7V;

2, VOH ≈ 4.12V,VOL ≈ 3.28V;

3, VIH ≈ 3.76V,VIL ≈ 3.64V。

- 對于LVPECL 電平,其各電壓參數如下:

1, Vcc = 3.3V,VEE = 0V,VBB ≈ 2.0V;

2, VOH ≈ 2.42V,VOL ≈ 1.58V;

3, VIH ≈ 2.06V,VIL ≈ 1.94V。

2,ECL/PECL/LVPECL電路匹配

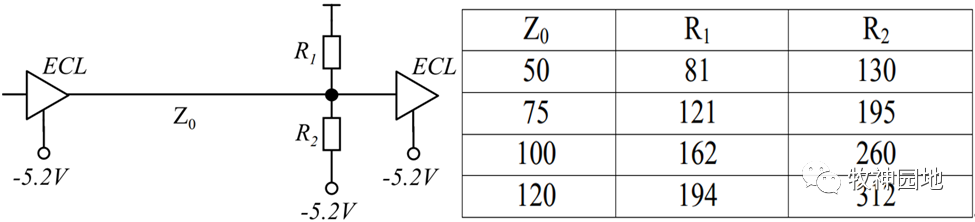

2.1 ECL電路匹配

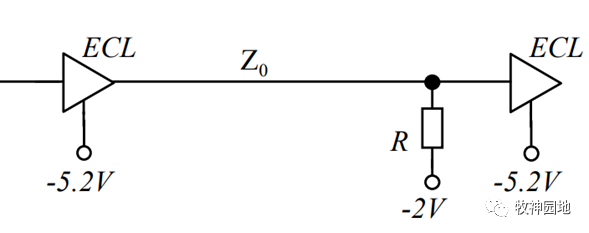

ECL/PECL/LVPECL電路是發射極耦合電路,需要在外部線路上提供一個電流通路(終端并聯匹配);ECL采用的是負電源電壓供電,有兩種匹配方案:

- 如下左圖所示,采用R1//R2的戴維南匹配的方案:

1, 分壓電平:R2/(R1+R2) *(-5.2V) = -2.0V;

2, 為了傳輸線阻抗匹配,必須使得Z0 = R1//R2,如下右圖所示。

- 如下圖所示,將R1//R2的方式改為單個電阻R;

1, 直接將R連接至-2.0V;

——需要由單獨的-2.0V供電電源。

2, 同樣為了保持傳輸線的阻抗匹配,必須使得R = Z0。

- 上面兩種匹配方式,從功能上來分析是完全等價的,只是第二種匹配方式需要額外的-2.0V電源,所以這種方式并不常用;

——對于第二種匹配方式,大家是否有種熟悉的感覺?在DDR總線的地址和控制線上,我們會上拉到VTT電源上,但有時又會采用分立上下拉電阻的方式;這是什么原因呢?

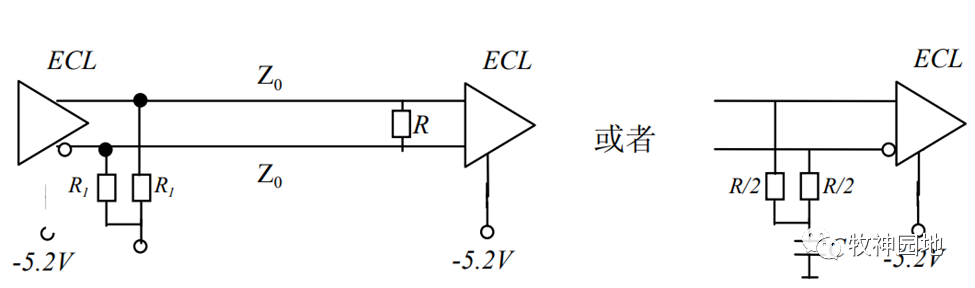

對于ECL差分信號的匹配,如下圖所示;對于松耦合的差分線(即Zdiff = 2Z0)來說,取R = 2Z0,保證差分線的阻抗匹配(忘記了的胖友們哪,你是忘了金斧頭還是銀斧頭哪?撿金斧頭的請回翻《特殊的串擾-差分信號》相關章節;多回顧才能有更深的理解和收獲,才能將所有的知識內容串起來);R1則需要保證ECL電路輸出的偏置電流。

2.2 PECL/LVPECL電路匹配

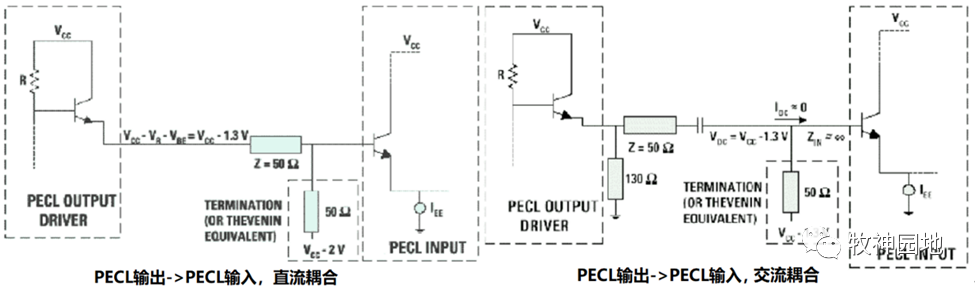

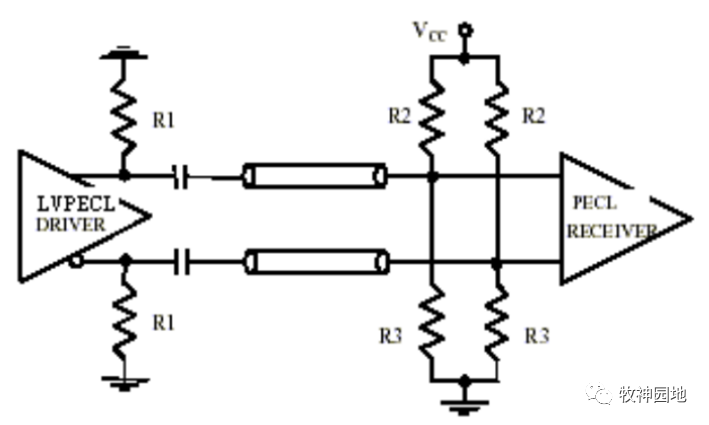

PECL/LVPECL電路的電路匹配方式如下圖所示,總共有兩種匹配方式:直流耦合和交流耦合;圖中只畫了差分對中的一條。

- 兩種耦合方式(直流和交流)的終端戴維南匹配電阻盡量與理想50Ω匹配(單端,如果是差分對之間就需要是Zdiff),以消除反射;

1, 該50Ω終端電阻盡量靠近PECL輸入端;

2, 直流偏置電平為Vcc -1.3V。

- 如果收發端的PECL電平中有存在非標準電平的情況,那么最好采用交流耦合的方式,以隔離直流電流;

——非標準PECL的直流偏置電平可能不是Vcc-1.3V。

- 如上左圖所示,PECL直流耦合方式中終端匹配接至Vcc-2V電壓,這主要是由兩個原因:

1, 如上所述Vcc-2V和VEE(直流偏置電平:Vcc-1.3V)之間相差0.7V(剛好維持導通狀態),可以盡量減小發送端器件的功率消耗;

2, 即使最壞情況下,也盡量保證輸出驅動電路不進入截止模式。

- 如上右圖所示,采用交流耦合方式,輸出電路與輸入電路之間增加了一個交流耦合電容,這改變了直流耦合的戴維南等效電路;

1, PECL輸出端,發射極開路晶體管(BJT)需要一條到地的直流通路,于是增加了130Ω的電阻(LVPECL,對于PECL來說需要240Ω),其電流大約為15mA;

2, PECL輸入端,沒有直流電流從輸出端流過交流耦合電容并進入PECL輸入端,終端匹配電壓:Vcc-1.3V成為了耦合電容右側電路的偏置電壓。

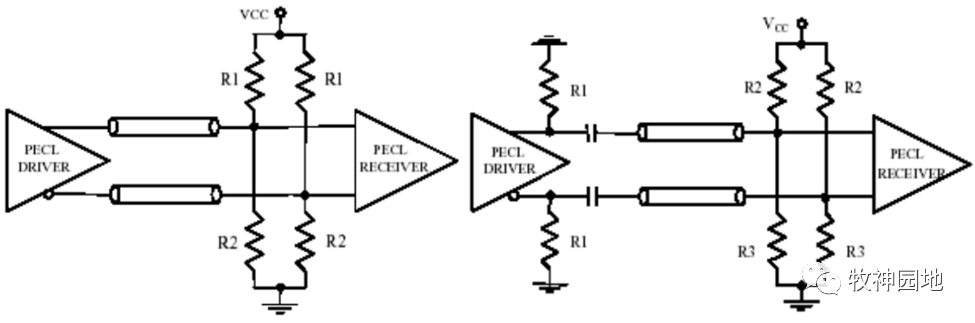

接下來我們看下完整的PECL/LVPECL差分對的匹配電路;

- 如下左圖所示為直流匹配,根據上述分析,必須要滿足兩個條件:VccR2/(R1+R2) = Vcc -2V,R1//R2 = R1R2/(R1+R2) = 50Ω;

1, 對于PECL電路Vcc = 5V,我們可以計算得到:R1 = 83Ω,R2 = 125Ω;

2, 對于LVPECL電路Vcc = 3.3V,我們可以計算得到:R1 = 125Ω,R2 =83Ω。

- 如下右圖所示為交流匹配,根據上述分析,同樣需滿足兩個條件:VccR3/(R3+R2) = Vcc -1.3V,R3//R2 = R3R2/(R3+R2) = 50Ω。

1, 對于PECL電路Vcc = 5V,我們可以計算得到:R2 = 68Ω,R3 = 193Ω;

——R1為PECL射極輸出電路提供輸出到地的通路,如上所述PECL(+5V)時取R1 = 240Ω,流過R1的電流約為15mA。

2, 對于LVPECL電路Vcc = 3.3V,我們可以計算得到:R2 = 83Ω,R3 = 125Ω。

——R1為LVPECL射極輸出電路提供輸出到地的通路,如上所述LVPECL(+3.3V)時取R1 = 130Ω,流過R1的電流約為15mA。

2.3 PECL-LVPECL之間的電路匹配

PECL到LVPECL的電路匹配也可以分為直流耦合和交流耦合兩種。

- 如下左圖所示為直流匹配電路圖;

1, 在A點需要滿足PECL輸出要求:R1//(R2+R3) = 50Ω,5*(R2+R3)/(R1+R2+R3) = 3V;計算可得,R1 = 83Ω,R2+R3 = 125Ω;

2, 在B點其交流擺幅需滿足:Vbac = Vaac*R3/(R2+R3),其中0.575

——將R2和R3代入Vbac和Vaac的轉換公式,可得到Vbacmax = 0.522V,Vbacmin = 0.3128V,滿足LVPECL的規格要求。

- 如上右圖為交流匹配電路圖,采用AC耦合就將輸出與輸入端的直流進行了隔離;

1, R2和R3需滿足:R2//R3 = 50Ω,3.3V*R3/(R2+R3) = 2.0V;可得R2 = 83Ω,R3 = 130Ω;

2, R1同樣是作為PECL的輸出對地通路,我們已經知道PECL時R1 = 240Ω。

那么從LVPECL到PECL的電路匹配呢?我們一般采用交流(AC)耦合方式(直流耦合方式的電平不夠高)。如下圖所示;

- R2和R3需滿足:R2//R3 = 50Ω,5V*R3/(R2+R3) = 3.7V;可得R2 = 68Ω,R3 = 193Ω;

- R1作為LVPECL的輸出對地通路, R1 =130Ω。

3,ECL系列邏輯電平特點

- ECL電平邏輯的輸出阻抗低(6~8Ω)輸入阻抗高,所以驅動能力特別強;可以支持遠距離的傳輸,背板以及長線纜傳輸基本上使用的ECL電平;

——可以驅動50Ω~130Ω特征阻抗的傳輸線而交流特性沒有明顯的改變;

- ECL器件相比于TTL/COM器件對溫度和電壓的變化更不敏感,所以ECL時鐘驅動器的各路時鐘并發性更好,Skew更小(Skew是指不同路時鐘互相之間的抖動);

- 相比于LVDS,ECL可以支持更高速率;LVDS一般用在1.5GHz以下的場合,而ECL可以支持高于10GHz的應用,在所有數字電路中,ECL的工作速率最高,延時小于1ns;

——在高于5GHz的應用中,基本上就是CML和ECL電平。

- ECL對傳輸阻抗的適應性更好(可以根據傳輸線阻抗進行不同分壓設計),LVDS屬于電流型驅動,其終端100Ω電阻兼有產生電壓的作用;所以為了不改變信號擺幅,終端電阻必須選擇100Ω,而為了保證良好的信號完整性,LVDS的傳輸線阻抗必須設計為50Ω;否則容易產生不必要的反射;

- ECL電路的缺點也很明顯:

1, 功耗大;

2, 噪聲容限小,抗干擾能力弱;

——邏輯擺幅800mV,噪聲容限200mV;ECL的高性能是用高功耗、低噪聲容限為代價換來的。

4,ECL系列器件使用原則

- 使 TTL 信號和 ECL 信號線相距一定距離(A > 8*h(信號線與回流平面間距)),減小直接串擾;

——ECL信號噪聲容限較低,比較容易受到串擾的影響。

- 若使用+5V TTL和-5.2V ECL,必須增加一個地平面做隔離,可以減小 TTL 噪聲泄漏到 ECL 系統;

- 對 ECL/PECL 信號和其它信號比如 TTL 信號,最好能使用不同的走線層,如果因為設計限制必須使用同一層走線,ECL/PECL 信號和 TTL 信號的距離應該足夠遠,應該大于5 倍差分線間距。

- 若使用+5V 的TTL 和 ECL,最好將+5V 平面(非地平面)一分為二,使 PCB 分割為 TTL 和 ECL 的不同區域;

——注意不要有長線穿越兩個+5V 區域的邊界,同時在兩個+5V 平面用電流量足夠大的 1μH 電感串接,可以減小 TTL 噪聲進入 ECL 系統。

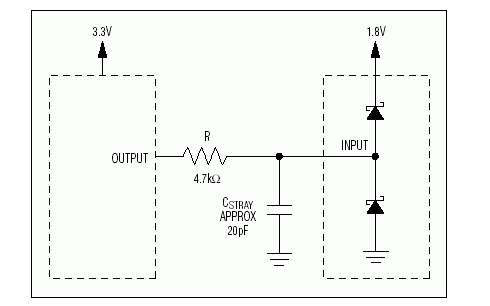

——若要接為高電平,不能直接接到 VCC(除非器件資料特別說明),必需通過電阻網絡分壓或通過二極管壓降來滿足輸入不超過 VIHmax,或通過別的無用輸出來實現。

- ECL單端輸出:無用輸出腳應懸空;若對于ECL互補輸出:如果兩者都未用,兩者都應懸空,如果其中之一被用,另一腳應該被端接;

- 終端匹配元件一定要放在最靠近傳輸線末端的地方;

- 集總參數電路,增加阻尼、降低 Q 值可防止振蕩;

- 對于2.5V LVPECL,3.3V LVPECL 和 5V PECL 電平之間的連接,最好通過 0.1uf /0.01uf 的電容交流耦合,否則有可能擊穿LVPECL 接口。

寫在最后

LVPECL是我們在高速信號傳輸中最常用的電平;由于其驅動能力強、傳輸距離遠,抖動小等優點,一般要求較高的高頻時鐘信號(>100MHz)采用LVPECL電平比較多。

-

TTL電路

+關注

關注

2文章

65瀏覽量

15285 -

差分放大器

+關注

關注

8文章

498瀏覽量

52722 -

晶體管

+關注

關注

77文章

9907瀏覽量

140139 -

射極跟隨器

+關注

關注

1文章

54瀏覽量

15333 -

ECL電平

+關注

關注

0文章

3瀏覽量

1535

發布評論請先 登錄

相關推薦

邏輯電平設計規范(一)

【轉】電子從業者必看 運算放大器為什么不能用作比較器

交流信號電平移位電路資料分享

高速ECL邏輯入門

邏輯電平詳細介紹

常用邏輯電平有哪些詳細資料介紹

信號邏輯電平標準的詳細說明

常用的差分邏輯電平詳細介紹

詳解信號邏輯電平標準:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML資料下載

評論