3DIC設(shè)計(jì)的重要性日益凸顯。當(dāng)今市場(chǎng)對(duì)AI應(yīng)用的需求在不斷增加,而摩爾定律的步伐卻在放緩,這使得芯片開發(fā)者不得不尋求其他類型的芯片架構(gòu),以滿足消費(fèi)者和領(lǐng)先服務(wù)提供商的預(yù)期。3DIC設(shè)計(jì)并不是簡(jiǎn)單地將多個(gè)裸片相鄰連接,而是通過硅晶圓或裸片的垂直堆疊來大幅提高性能和功耗表現(xiàn),并讓尺寸變得更小。

為此,新思科技和力晶積成電子制造股份有限公司(簡(jiǎn)稱“力積電”)攜手合作,共同推出新的晶圓堆棧晶圓(WoW)和晶圓堆棧芯片(CoW)解決方案。這是一種特殊的3DIC設(shè)計(jì),它借助新思科技的3DIC Compiler平臺(tái)和力積電的先進(jìn)制程技術(shù),創(chuàng)造出一種新的聯(lián)合解決方案,讓開發(fā)者能夠?qū)?a href="http://www.xsypw.cn/tags/dram/" target="_blank">DRAM存儲(chǔ)器直接堆疊和鍵合在芯片上,從而以更低的成本創(chuàng)建出先進(jìn)的電路。

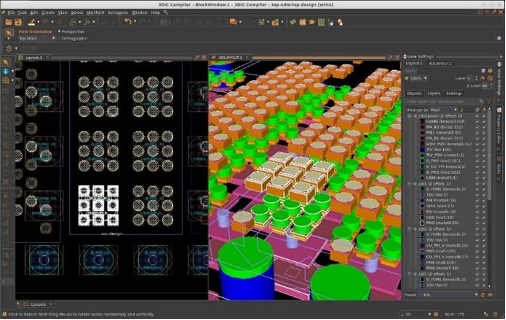

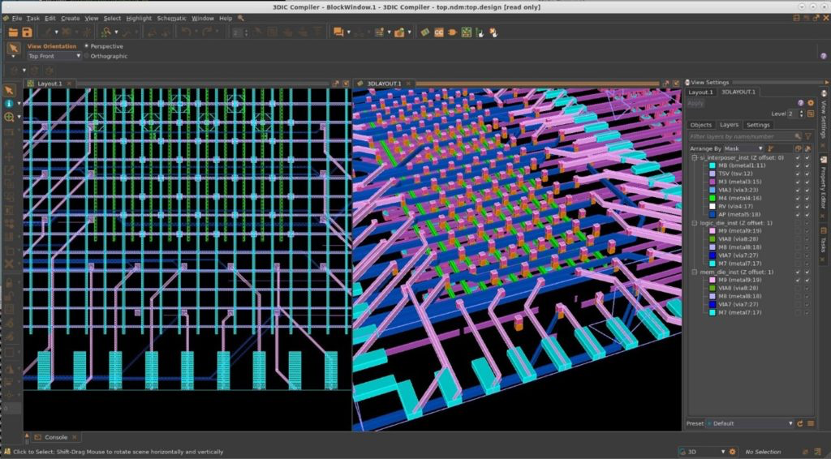

新思科技3DIC Compiler直觀地顯示了3D堆疊裸片中的芯片凸塊、TSV和混合鍵合

力晶積成電子制造股份有限公司副總裁兼首席技術(shù)官S.Z. Chang表示:“3DIC設(shè)計(jì)非常復(fù)雜,尤其是在堆疊內(nèi)存和邏輯裸片方面,需要依賴半導(dǎo)體生態(tài)系統(tǒng)中眾多參與者的專業(yè)知識(shí)。我們很高興能與新思科技密切合作,帶來這一出色的解決方案。有了該解決方案,開發(fā)者在將多個(gè)半導(dǎo)體晶圓融合成一個(gè)3D設(shè)計(jì)時(shí),所需的時(shí)間會(huì)減少1-2個(gè)月,同時(shí)堆疊兩個(gè)裸片所需的迭代次數(shù)也會(huì)相應(yīng)減少。”

本文將詳細(xì)介紹WoW、混合鍵合及其主要優(yōu)勢(shì),并探討為什么DRAM邏輯堆疊有利于打造創(chuàng)新性的AI應(yīng)用,以及新思科技與力積電聯(lián)合打造的這一新解決方案如何幫助提高開發(fā)效率并帶來量產(chǎn)時(shí)效優(yōu)勢(shì)。

什么是WoW混合鍵合和CoW混合鍵合?

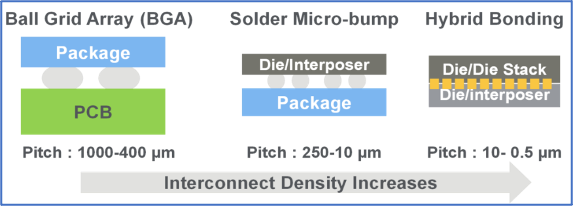

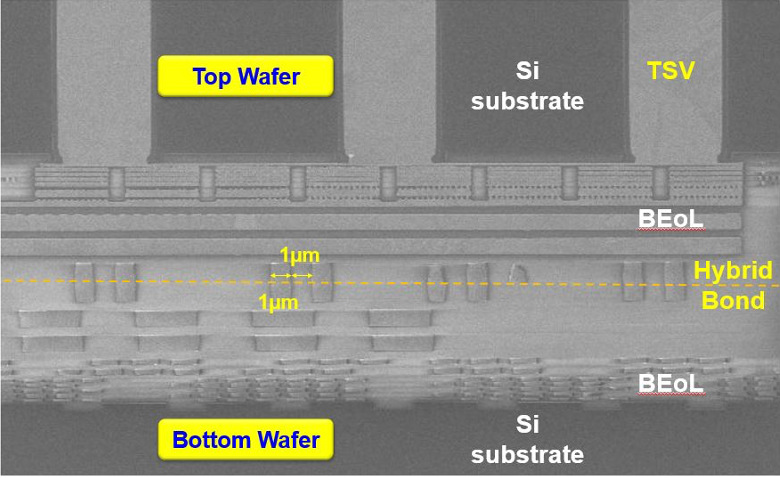

WoW混合鍵合堆疊是一種3D設(shè)計(jì)技術(shù),它通過以電氣方式連接不同的晶圓,打造單個(gè)集成器件。在該技術(shù)中,每個(gè)晶圓上都存在微小的銅焊盤,這些焊盤被永久地鍵合在一起,形成數(shù)以萬計(jì)甚至百萬計(jì)的電路互連。CoW混合鍵合與此相似,當(dāng)設(shè)計(jì)中用到多種不同尺寸的芯片時(shí),這可能是更實(shí)用的方法。通過WoW和CoW 3D堆疊,混合鍵合在沒有增加功耗的情況下縮短了信號(hào)傳輸距離,并提供了比任何其他3D集成方案更高的互連和帶寬密度。該技術(shù)可以微縮到亞微米級(jí)互連,有助于實(shí)現(xiàn)廣泛的芯片分解和小芯片架構(gòu)創(chuàng)新。

力積電專注于利用現(xiàn)有的芯片供應(yīng)鏈,開發(fā)間距小于3um的WoW堆疊技術(shù)。此外,力積電還與新思科技通力合作,通過采用堅(jiān)固的銅-銅混合鍵合技術(shù)和硅通孔(TSV)工藝,成功展現(xiàn)了晶圓級(jí)多堆疊結(jié)構(gòu)的優(yōu)勢(shì)。

細(xì)間距互連微縮(圖源:L.Jiang等,ECTC 2022)

不過,與其他方法相比,混合鍵合要復(fù)雜得多,隨之而來的就是成本問題。但對(duì)于AI訓(xùn)練引擎等高級(jí)應(yīng)用來說,這一成本還是非常值得的,因?yàn)樗@著提高了內(nèi)存帶寬密度并降低了延遲。使用混合鍵合在邏輯器件上堆疊內(nèi)存帶來了AI所需的高性能和低延遲,并且與傳統(tǒng)的2D甚至2.5D設(shè)計(jì)相比,還存在許多額外的改進(jìn)。

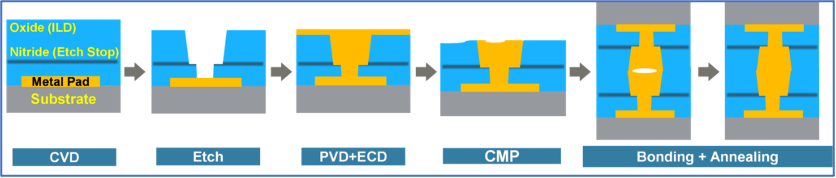

混合鍵合工藝流程(圖源:Albert Lan等,2021年第17屆國際器件封裝大會(huì))

在邏輯器件上堆疊DRAM所面臨的挑戰(zhàn)

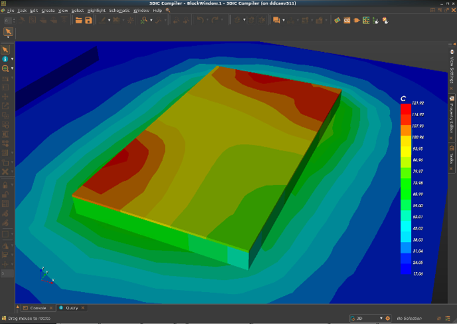

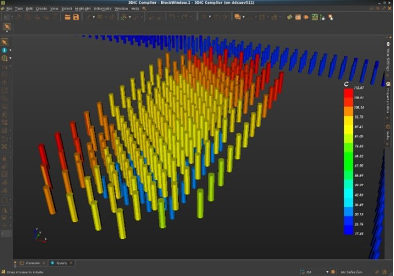

新思科技3DIC Compiler直觀地顯示了處理器芯片上DRAM堆疊的發(fā)熱情況

長(zhǎng)期以來,芯片開發(fā)者一直在思考如何更好地堆疊處理器和內(nèi)存。其中有許多因素需要考慮:選擇異構(gòu)還是同構(gòu)集成,如何更好地為裸片堆疊供電,熱管理,棧內(nèi)PVT傳感器,壓力引起的性能和可靠性問題等等。

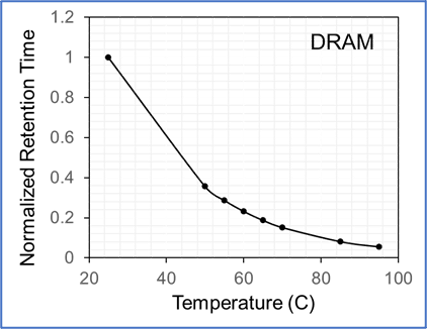

新思科技產(chǎn)品總監(jiān)Kenneth Larsen指出:“在堆疊動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(DRAM)而非靜態(tài)隨機(jī)存取存儲(chǔ)器(SRAM)時(shí),這些因素會(huì)變得更加復(fù)雜,因?yàn)镈RAM的數(shù)據(jù)保留能力對(duì)溫度較為敏感。在3D堆疊結(jié)構(gòu)中,處理器和DRAM的工作溫度可能達(dá)到110攝氏度--120攝氏度,而在2D DRAM結(jié)構(gòu)中則為55攝氏度。”

較高的溫度將會(huì)導(dǎo)致DRAM由于電荷泄漏而更快地丟失數(shù)據(jù)。因此,在給定的時(shí)間段內(nèi)需要更多的自刷新,才能確保數(shù)據(jù)處于健康狀態(tài)。芯片開發(fā)者需要探究溫度會(huì)對(duì)整個(gè)系統(tǒng)的性能產(chǎn)生怎樣的影響。

DRAM的數(shù)據(jù)保留時(shí)間對(duì)溫度較為敏感

在邏輯器件上堆疊DRAM時(shí),底部計(jì)算邏輯裸片所產(chǎn)生的熱量會(huì)向上散發(fā)而影響內(nèi)存,因而有必要通過設(shè)計(jì)來解決發(fā)熱和散熱問題。

再者,內(nèi)存和邏輯設(shè)計(jì)由不同的供應(yīng)商或設(shè)計(jì)團(tuán)隊(duì)負(fù)責(zé),由于團(tuán)隊(duì)之間沒有共同的溝通渠道來展開討論或交換設(shè)計(jì),因此可能會(huì)導(dǎo)致在堆疊這兩者時(shí)出現(xiàn)流程脫節(jié)。此外,幾何結(jié)構(gòu)及采用的縮小工藝也不同;例如,一個(gè)是100% GDS,而另一個(gè)則是90% GDS。面對(duì)這些挑戰(zhàn),需要一種創(chuàng)新的EDA解決方案,幫助開發(fā)者從設(shè)計(jì)階段順利進(jìn)入制造階段。

高效的Multi-Die系統(tǒng)集成

力積電與新思科技在這一新解決方案上的合作主要依賴于新思科技的3DIC Compiler平臺(tái)。該平臺(tái)是一個(gè)完整的端到端解決方案,可實(shí)現(xiàn)高效的3D Multi-Die系統(tǒng)集成。3DIC Compiler基于新思科技數(shù)字設(shè)計(jì)系列的通用融合數(shù)據(jù)模型基礎(chǔ)結(jié)構(gòu),它融合眾多變革性的Multi-Die設(shè)計(jì)功能,提供了一個(gè)完整的3D平臺(tái),涵蓋從架構(gòu)設(shè)計(jì)到芯片簽核的整個(gè)過程。該解決方案包括沉浸式2D和3D直觀顯示、跨層次結(jié)構(gòu)探索和規(guī)劃、設(shè)計(jì)和實(shí)現(xiàn)、DFx、系統(tǒng)級(jí)驗(yàn)證和簽核分析。

DRAM處理器的中介層

系統(tǒng)的全連接模型可以在3DIC Compiler中建模,也可以通過標(biāo)準(zhǔn)網(wǎng)表和各種文本格式導(dǎo)入。3DIC Compiler提供了在底部和頂部裸片之間創(chuàng)建連接的功能,與手動(dòng)方法相比,這可為芯片開發(fā)者節(jié)省多達(dá)兩個(gè)月的時(shí)間。在概念、設(shè)計(jì)、實(shí)現(xiàn)和制造階段,優(yōu)化芯片涉及多個(gè)步驟和多項(xiàng)檢查。

新思科技3DIC Compiler中直觀地顯示了TSV熱圖

其中一個(gè)步驟是3D系統(tǒng)連接檢查,用于驗(yàn)證半導(dǎo)體裸片、裸片堆疊、中介層、嵌入式橋接和封裝基板之間的電氣、邏輯和物理連接。這項(xiàng)檢查可以在設(shè)計(jì)中檢查從裸片上的邏輯裸片焊盤到主IO(鍵合和凸塊之間的物理連接)的電氣連接,并可以明確指出網(wǎng)狀結(jié)構(gòu)不完整或短路等問題。3D設(shè)計(jì)規(guī)則檢查、裸片鏡像堆疊、鍵合協(xié)調(diào)以及功耗和DFT檢查等也在此范圍內(nèi)。

新思科技的3DIC Compiler軟件會(huì)檢查信號(hào)和供電是否借由TSV從底部裸片正確到達(dá)了頂部裸片。此外,它還可以進(jìn)行必要的熱仿真,從而對(duì)兩個(gè)裸片間的相互作用(包括功耗和隨后的產(chǎn)生熱量)進(jìn)行建模。兩個(gè)裸片之間的熱量需要散掉,而3DIC Compiler可以幫助開發(fā)者利用多種不同的方法來實(shí)現(xiàn)這一點(diǎn)。

WoW解決方案(圖源:力積電)

在使用力積電和新思科技合作打造的全新3D WoW和CoW解決方案時(shí),經(jīng)認(rèn)證的新思科技數(shù)字設(shè)計(jì)系列解決方案會(huì)在從流片開始的整個(gè)流程中為客戶提供協(xié)助,而3DIC Compiler正是構(gòu)建在該數(shù)字設(shè)計(jì)系列的基礎(chǔ)之上。這一新的解決方案在內(nèi)存和邏輯裸片之間提供了高帶寬,從而可以提高AI推理的性能和速度。

隨著AI技術(shù)日漸融入人們的日常生活,我們期望它變得更加智能,因此對(duì)內(nèi)存帶寬、IO和算力的總體需求會(huì)隨著時(shí)間的推移而不斷增長(zhǎng)。然而,摩爾定律已在放緩,因此先進(jìn)的封裝將會(huì)是芯片開發(fā)者今后所要尋求的答案。3DIC Compiler等產(chǎn)品正在協(xié)助開發(fā)者快速、有效地滿足這些新的應(yīng)用需求,推動(dòng)人工智能及更多領(lǐng)域向前發(fā)展。

原文標(biāo)題:新思科技攜手力積電,以3DIC解決方案將AI推向新高

文章出處:【微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

新思科技

+關(guān)注

關(guān)注

5文章

798瀏覽量

50348 -

力積電

+關(guān)注

關(guān)注

0文章

35瀏覽量

76

原文標(biāo)題:新思科技攜手力積電,以3DIC解決方案將AI推向新高

文章出處:【微信號(hào):Synopsys_CN,微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

臺(tái)積電2025年將全球建十座廠,資本支出創(chuàng)歷史新高

聯(lián)發(fā)科攜手臺(tái)積電、新思科技邁向2nm芯片時(shí)代

軟銀攜手臺(tái)積電共筑AI芯片新篇章

新思科技7月份行業(yè)事件

新思科技攜手英特爾推出可量產(chǎn)Multi-Die芯片設(shè)計(jì)解決方案

臺(tái)積電上調(diào)代工費(fèi)以確保穩(wěn)定供應(yīng)

新思科技面向英特爾代工推出可量產(chǎn)的多裸晶芯片設(shè)計(jì)參考流程,加速芯片創(chuàng)新

新思科技推出業(yè)界首款PCIe 7.0 IP解決方案

新思科技與臺(tái)積公司深度合作,推動(dòng)芯片設(shè)計(jì)創(chuàng)新

新思科技面向臺(tái)積公司先進(jìn)工藝加速下一代芯片創(chuàng)新

臺(tái)積電股價(jià)刷新歷史新高,臺(tái)積電上漲2.19%

臺(tái)積電股價(jià)刷新歷史新高

新思科技與英特爾深化合作,以新思科技IP和經(jīng)Intel 18A工藝認(rèn)證的EDA流程加速先進(jìn)芯片設(shè)計(jì)

臺(tái)積電漲超5%創(chuàng)歷史新高 AI需求旺盛可望逐年高速增長(zhǎng)50%

新思科技攜手臺(tái)積公司推出“從架構(gòu)探索到簽核” 統(tǒng)一設(shè)計(jì)平臺(tái)

新思科技攜手力積電,以3DIC解決方案將AI推向新高

新思科技攜手力積電,以3DIC解決方案將AI推向新高

評(píng)論