1涉及的數字電路基礎知識

模擬信號:在時間和幅值上是連續變化的電信號。

圖1

數字信號:在時間和幅值上是離散的電信號。

圖2

數字電路的基本工作信號是二進制的數字信號,而二進制數只有“0”和“1”兩個基本數字,對應在電路上只需要兩種不同的工作狀態,即高電平和低電平。0和1表示兩種對立的工作狀態,并不表示數量的大小在數字電路中,通常用電位的高低去控制門電路,規定用1表示高電平,用0表示低電平,為正邏輯,若用0表示高電平,用1表示低電平,為負邏輯。

1.2數字電路的表示方法

1.2.1邏輯函數表達式

用邏輯函數表示輸入信號與輸出信號的關系。邏輯表達式中的運算一般為布爾運算,與普通代數不同,布爾代數中的變量是二元值的邏輯變量。

圖3

1.2.2真值表

用表格表示門電路輸入信號與輸出信號對應的邏輯關系。

圖4

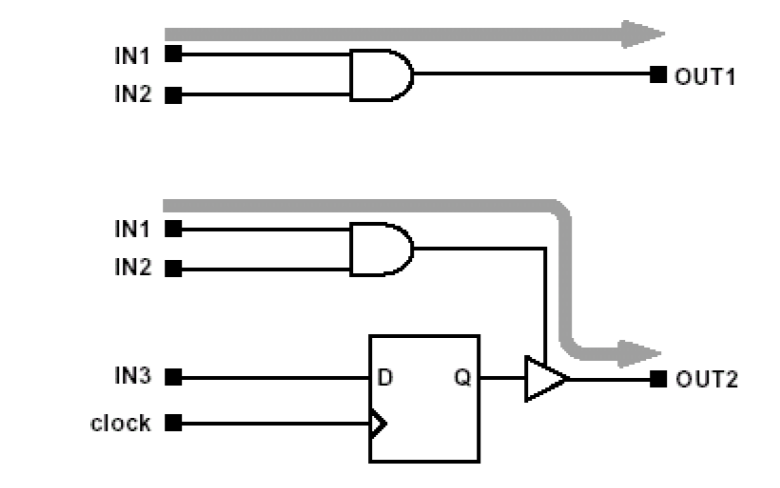

1.2.3邏輯電路圖

圖5

1.2.4波形圖

以波的形式表示門電路輸入與輸出的邏輯關系。

圖6

其他表達方法還有:卡諾圖法(一種幾何圖形,可以用來表示和簡化邏輯函數表達式);點陣圖法(是早期可編程邏輯器件中直觀描述邏輯函數的一種方法);硬件設計語言法(是采用計算機高級語言來描述邏輯函數并進行邏輯設計的一種方法,它應用于可編程邏輯器件中,目前采用最廣泛的硬件設計語言有HDL、VHHDL等)。

1.3數字電路中的邏輯關系

數字電路中往往用輸入信號表示“條件”,用輸出信號表示“結果”,條件與結果之間的因果關系稱為邏輯關系。基本的邏輯關系:與邏輯、或邏輯、非邏輯。能實現某種邏輯關系的電路稱為邏輯門電路。基本邏輯門電路:與門、或門、非門。

1.3.1與門電路

與邏輯關系:只有決定某事件的全部條件同時具備時,該事件才發生,邏輯與,或稱邏輯乘。表達式:Y=A·B或Y=AB。邏輯功能:有 0 出 0 ,全 1 出 1 。說明與門定義的電路(圖7)、邏輯符號(圖8)、真值表(圖9)。

圖7

圖8

圖9

1.3.2或門電路

或邏輯關系:決定某事件的幾個條件中,至少有一個條件具備,該事件都會發生,或稱邏輯加。表達式:Y=A+B。邏輯功能:有 1 出 1,全 0 出 0 。說明或門定義的電路(圖10)、邏輯符號(圖11)、真值表(圖12)。

圖10

圖11

圖12

1.3.3非門電路

非邏輯關系:當條件具備時,該事件不發生;而當條件不具備時,該事件反而發生,條件和結果總是呈相反狀態。稱為邏輯非,也稱為邏輯反。表達式: 。邏輯功能:入 0 出 1 ,入 1 出 0 。說明非門定義的電路(圖13)、邏輯符號(圖14)、真值表(圖15)。

圖13

圖14

圖15

1.4脈沖波形和脈沖波形的一些特性參數

獲得脈沖的方法:(1)自激振蕩電路直接產生矩形脈沖。由多諧振蕩器來實現。(2)將已有波形(正弦波、鋸齒波等)整形為矩形脈沖。由施密特觸發器和單穩態觸發器來實現555 定時器是構成多諧振蕩器、施密特觸發器和單穩態觸發器的既經濟又簡單實用的器件。

圖16

矩形脈沖的一些特性參數:

脈沖周期T:周期性重復的脈沖序列中,兩個相鄰脈沖之間的時間間隔。有時也使用頻率(f=1/T)表示單位時間內脈沖重復的次數。

脈沖幅度Vm :脈沖電壓的最大變化幅度。

脈沖寬度tW:從脈沖前沿到達0.5Vm起,到脈沖后沿到達0.5Vm為止的一段時間。

上升時間tr:脈沖上升沿從0.1Vm上升到0.9Vm所需要的時間。

下降時間tf:脈沖下降時間從0.9Vm下降到0.1Vm所需要的時間。

占空比q:脈沖寬度與脈沖周期的比值,亦即q=tW/T。

此外,在將脈沖波形或者產生電路用于具體的數字系統時,有時還可能有一些特殊的要求,例如脈沖周期和幅度的穩定性等。這時還需要增加一些相應的性能參數來說明。

1.5半導體存儲電路基礎

各種門電路雖然都有兩種不同的輸出狀態(高、低電平,亦即1、0),但是都不能自行保持。在各種復雜的數字電路中不但需要對二值信號進行數值運算和邏輯運算,還經常需要將運算結果保存下來。為此,需要使用具有記憶功能的基本邏輯單元。能夠存儲1位二值信號的基本單元電路統稱為觸發器。

鎖存器和觸發器:鎖存器---不需要觸發信號,由輸入信號直接完成置0或置1操作。

觸發器---需要一個觸發信號(稱為時鐘信號clock),只有觸發信號有效時,才按輸入信號完成置0或置1操作。鎖存器是靜態電路,觸發器是動態電路。

觸發器具有如下特點:有兩個穩定狀態(簡稱穩態),用來表示邏輯 0 和 1。在輸入信號作用下,觸發器的兩個穩定狀態可相互轉換(稱為狀態的翻轉)。 輸入信號消失后,新狀態可長期保持下來,具有記憶功能。

觸發器的分類如下。按觸發方式分:電平觸發、脈沖觸發、邊沿觸發。按邏輯功能分:SR 觸發器、D 觸發器、JK 觸發器、T 觸發器。

下文大致介紹一下SR鎖存器和SR觸發器,其它有興趣的內容可以自行去學習。

1.5.1SR鎖存器

SR鎖存器(兩個Set-Reset Latch)是靜態存儲中當中最基本、也是電路結構最簡單的一種。通常它由兩個或非門或者與非門組成。下文以或非門組成的鎖存器為例說明。

圖17為SR鎖存器電路結構。

圖17

Q和Q′為互補輸出端,正常工作時,它們的輸出狀態相反(規定,兩個端口的輸入狀態一定相反)。通常用Q的狀態表示觸發器的狀態,即: Q = 0,Q′ = 1時,稱為觸發器的“0”態;Q = 1,Q′ = 0時,稱為觸發器的“1”態。SR鎖存器輸出特性表如圖18所示,圖19是其邏輯符號。

圖18

圖19

1.5.2電平觸發的SR觸發器

在數字系統中,為協調各部分的動作,常常要求某些觸發器在同一時刻動作(即改變狀態,也稱為翻轉),這就要求有一個同步信號來控制,這個控制信號叫做時鐘信號(Clock),簡稱時鐘,用CLK表示。具有時鐘脈沖控制的觸發器統稱為時鐘觸發器,又稱鐘控觸發器。 電平觸發器(也稱同步觸發器)是其中最簡單最常見的一種。

圖20是SR觸發器的電路結構和工作原理,圖21是其功能表,圖22是其邏輯符號。

圖20

圖21

圖22

1.6組合邏輯和時序邏輯

組合邏輯的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原本的狀態無關,邏輯中不牽涉跳變沿信號的處理。

時序邏輯是其特點為任意時刻的輸出不僅取決于該時刻的輸入,而且還和電路原來的狀態有關。電路里面有存儲元件用于記憶信息,從電路行為上講,不管輸入如何變化,僅當時鐘的沿(上升沿或下降沿)到達時,才有可能使輸出發生變化。

2時序分析基礎概念

2.1 STA(靜態時序分析)

簡介:靜態時序分析是檢查IC系統時序是否滿足要求的主要手段。以往時序的驗證依賴于仿真,采用仿真的方法,覆蓋率跟所施加的激勵有關,有些時序違例會被忽略。此外,仿真方法效率非常的低,會大大延長產品的開發周期。靜態時序分析工具很好地解決了這兩個問題。它不需要激勵向量,可以報出芯片中所有的時序違例,并且速度很快。STA在設計中的位置如下(不止一個環節哦)。

圖23

作用:通過靜態時序分析,可以檢查設計中的關鍵路徑分布;檢查電路中的路徑延時是否會導致setup違例;檢查電路中是否由于時鐘偏移過大導致hold違例;檢查時鐘樹的偏移和延時等情況。此外靜態時序分析工具還可以與信號完整性工具結合在一起分析串擾問題。

常用的靜態時序工具是SYNOPSYS公司的PrimeTime。

圖24

2.2 Timing Arc(時序弧)

簡介:如果兩個pin之間在timing上存在因果關系,我們就把這種時序關系稱為Timing arc,主要分為定義時序延遲,和定義時序檢查兩種。為什么叫它時序弧?因為時序圖中經常用一條弧形線段來表示它。

如圖25所示,圖中弧線部分都可以表示為時序弧。

圖25

2.2.1時序延遲的Timing Arc

Combinational Timing Arc:最基本的TimingArc。TimingArc 如果不特別指明的話,就是屬于此類。定義了從特定輸入到特定輸出(A到Z)的延遲時間。

Edge Timing Arc:定義時序組件ClockActive Edge 到數據輸出的延遲時間,依據Clock上升或下降分為2類。

Edge Timing Arc:定義時序組件ClockActive Edge 到數據輸出的延遲時間,依據Clock上升或下降分為2類。

Preset and Clear Timing Arc:定義時序組件清除信號(Preset或Clear發生后,數據被清除的速度,依據清除信號上升或下降及是Preset或Clear分為4類。這個TimingArc 通常會被取消掉,因為它會造成信號路徑產生回路,這對STA而言是不允許的。

Three State Enable & Disable Timing Arc:定義 Tri-State 組件致能信號(Enable)到輸出的延遲時間,依據Enable或Disable分為2類。

2.2.2時序檢查的Timing Arc

Setup Timing Arc:定義時序組件(Sequential Cell,如Flip-Flop、Latch 等)所需的Setup Time。

Hold Timing Arc:定義時序組件所需的 Hold Time,依據Clock 上升或下降分為2類。

Recovery Timing Arc:定義時序組件ClockActive Edge 之前,清除信號不準啟動的時間,依據Clock上升或下降分為2類。

Removal Timing Arc:定義序向組件ClockActive Edge 之后,清除信號不準啟動的時間,依據Clock上升或下降分為2類。

Width Timing Arc:定義信號需維持穩定的最短時間,依據信號維持在0或1的位準分為2類。

2.3 Timing Path(時序路徑)

由startponit和endpoint組成。Startpoint:設計中數據被時鐘沿載入的那個時間點,包括時序單元的input pin、design的input port。Endpoint:數據通過了組合邏輯被另一個時鐘沿載入的時間點,時序元件的數據輸入pin、設計的output port。

Timing Path大致分為以下幾類:IO2REG、REG2REG、REG2IO、IO2IO(“2”表示“to”)。IO2REG:開始于一個input port 且結束于時序元件的數據輸入端。REG2REG:開始于時序元件的時鐘pin且結束于時序元件的數據輸入端。REG2IO:開始于時序元件的時鐘pin且結束在一個output port。IO2IO:開始于input port 且結束于 output port。

2.4 Slack

余量,就是signal的arrive time和require time的差值(或require time和arrive time的差值);每一個path都有專屬的slack,slack值可以是正,0或者負。

2.5margin

裕量,當時序要求滿足,slack為正時,這個值就是margin。

2.6Critical Path

某一個path擁有最壞的slack的話則稱之為 critical path,若是所有的path都沒有時序違規,則slack都是正數,此時最小的那個slack則是critical path。

2.7group path

路徑可以被分組(group)來得到各自的時序分析,時序報告和優化。

2.8發送時鐘

兩級寄存器中觸發第一級寄存器的時鐘。

2.9捕獲時鐘

兩級寄存器中觸發第二級寄存器的時鐘。

2.10clock skew(時鐘偏移)

同一時鐘源到達不同的寄存器的延時不同。

2.11clock jitter(時鐘抖動)

時鐘頻率和相位會不斷變化,脈沖寬度會發生變化。

2.112clock latency(時鐘延時)

簡介:時鐘從時鐘源(比如說晶振)出發到達觸發器時鐘端口的延時,稱為時鐘的延時,包含時鐘源延遲(source latency)和時鐘網絡的延遲(network latency)。

分類。clock source latency(時鐘源延遲):也稱為插入延遲(insertion delay),是時鐘信號從其實際時鐘原點到設計中時鐘定義點(時鐘的輸入引腳)的傳輸時間。clock network latency(時鐘網絡的延遲):是時鐘信號從其定義的點(端口或引腳)到寄存器時鐘引腳的傳輸,經過緩沖器和連線產生的延遲(latency) 。

2.13transition(時鐘轉換時間)

時鐘的上升沿跳變到下降沿或者時鐘下降沿跳變到上升沿的時間。時鐘的轉換時間與與單元的延時時間(也就是器件特性)還有電容負載有關。

2.14 capacitance

負載電容。

2.15fanout

時鐘扇出。

2.16driving cell

驅動單元。

2.17最快路徑和最慢路徑

簡介。最快路徑:指在信號傳播延時計算中調用最快工藝參數的路徑;根據信號的分類可以分為最快時鐘路徑和最快數據路徑。最慢路徑:指在信號傳播延附計算中調用最慢工藝參數的路徑;分為最慢時鐘路徑和最慢數據路徑。

為什么存在最快和最慢路徑:在一個庫中,盡管電路器件單元已經被綜合映射,但是工具可以通過改變周圍的環境來得到不同的單元延時,所以即使是同一個庫,調用工藝參數不一樣的情況下,:其單元延時是不同的,因此就有了最快路徑和最慢路徑。

2.18uncertainty

uncertainty,簡稱時鐘不確定性。主要用來定義Clock信號到時序器件的Clock端可能早到或晚到的時間,降低了時鐘抖動jitter對有效時鐘周期的影響。值得注意的是,在setup check中,clock uncertainty是代表著降低了時鐘的有效周期;而在hold check中,clock uncertainty是代表著hold check所需要滿足的額外margin。

2.19SDC(Synopsys design constraints)

簡介:即時序分析的設計約束文件,對電路的時序,面積,功耗進行約束,它是設計的命脈,決定了芯片是否滿足設計要求的規范。

分類。描述芯片的工作速度,即時鐘的頻率:create_clock,create_generated_clock等。描述芯片的邊界約束:set_input_delay, set_output_delay等。描述芯片的一些設計違反rule(DRV):set_max_fanout,set_max_capacitance, set_max_transition等。描述設計中一些特殊的路徑:set_false_path,set_multicycle_path等。描述設計中一些需要禁止的timing arc:set_disable_timing等。

3時序分析的常用概念

3.1 launch edge

時序分析起點,第一級寄存器數據變化的時鐘邊沿,也是靜態時序分析的起點。

3.2 latch edge

時序分析終點,數據鎖存的時鐘邊沿,也是靜態時序分析的終點。

3.3Setup Time (Tsu)

簡介:建立時間,是指在時鐘沿到來之前數據從不穩定到穩定所需的時間,假設建立的時間不滿足要求那么數據將不能在這個時鐘上升沿被穩定的打入觸發器。

圖26

3.4 Hold Time (Th)

保持時間,是指數據穩定后保持的時間。假設保持時間不滿足要求那么數據相同也不能被穩定的打入觸發器。

圖27

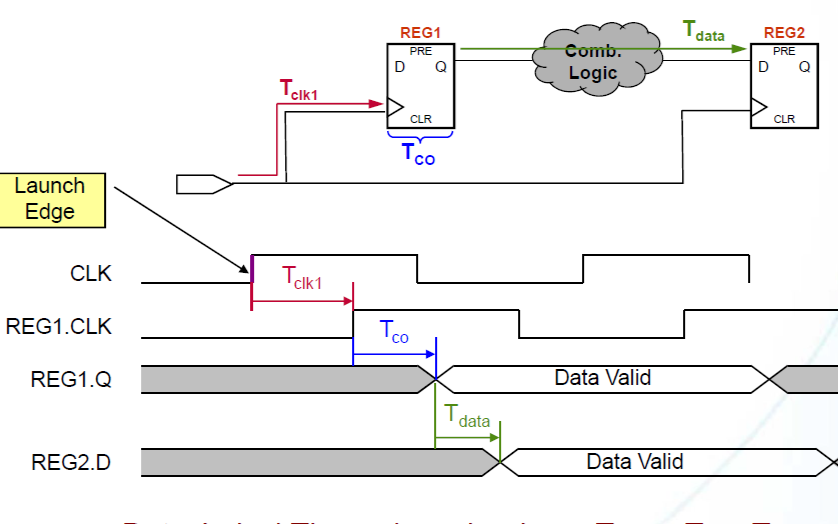

3.5 Clock-to-Output Delay(Tco)

數據輸出延時,這個時間指的是當時鐘有效沿變化后,數據從輸入端到輸出端的最小時間間隔。

3.6 Clock skew

時鐘偏斜,是指一個時鐘源到達兩個不同寄存器時鐘端的時間偏移。計算公式:Tskew = Tclk2 - Tclk1。

圖28

3.7Data Arrival Time

輸入數據在有效時鐘沿后到達所須要的時間。主要分為三部分:時鐘到達寄存器時間(Tclk1),寄存器輸出延時(Tco)和傳輸數據延時(Tdata)。計算公式:Data Arrival Time = Launch edge + Tclk1 +Tco + Tdata。

圖29

3.8Clock Arrival Time

時鐘到達時間,時鐘從latch邊沿到達鎖存寄存器時鐘輸入端所消耗的時間為時鐘到達時間。計算公式:Clock Arrival Time = Lacth edge + Tclk2。

圖30

3.9 Data Required Time(setup/hold)

簡介:數據需求時間,在時鐘鎖存的建立時間和保持時間之間數據必須穩定,從源時鐘起點達到這樣的穩定狀態須要的時間即為數據需求時間。(建立時間)數據需求時間:Data Required Time = Clock Arrival Time – Tsu。(保持時間)數據需求時間:Data Required Time = Clock Arrival Time + Th。

圖31

3.10Setup Slack和Hold Slack

建立時間余量,當數據需求時間大于數據到達時間時,就說時間有余量,Slack是表示設計是否滿足時序的一個稱謂。計算公式:Setup slack = Data Required Time - Data Arrival Time。由公式可知。正的slack表示數據需求時間大于數據到達時間,滿足時序(時序的余量)。負的slack表示數據需求時間小于數據到達時間,不滿足時序(時序的欠缺量)。

圖32

Hold slack可根據定義類比。

3.11時鐘最小周期

簡介。系統時鐘能執行的最高頻率。最小時鐘的要求:(1)當數據需求時間大于數據到達時間時,時鐘具有余量。(2)當數據需求時間小于數據到達時間時,不滿足時序要求,寄存器經歷亞穩態或者不能正確獲得數據。(3)當數據需求時間等于數據到達時間時。這是最小時鐘執行頻率。剛好滿足時序。

計算過程。滿足要求:Data Required Time = Data Arrival Time(滿足建立時間要求)。即:Tmin + Latch edge + Tclk2 - Tsu = Launch edge + Tclk1 + Tco + Tdata。得到:Tmin = Tco + Tdata + Tsu – Tskew。

4時序分析的三種模式

4.1單一模式

簡介:在該模式下,工具只會在指定的一種工作條件下檢查建立時間和保持時間,該工作條件可能是最好的、典型的、最壞的中的一種,但只能是單一的一種。

建立時間分析。特征:捕獲時鐘選擇最快路徑,發射時鐘選擇最慢路徑,數據路徑選擇最慢路徑。公式:發送時鐘最慢路徑延時+最慢數據路徑延時≤捕獲時鐘最快路徑延時+時鐘周期-終止點時序單元建立時間。如圖33所示。

圖33

保持時間分析。捕獲時鐘選擇最慢路徑,發射時鐘選擇最快路徑,數據路徑選擇最快路徑。計算公式:發射時鐘最快路徑延時 + 最快數據路徑延時≥捕獲時鐘最慢路徑延時 + 終止點時序單元保持時間。

4.2最好最壞模式

對于最好-最壞分析模式,靜態時序分析工具會同時在PVT環境中的最好的和最壞的工作環境下檢查建立時間和保持時間。也就是說,使用這個方式的時候,至少需要讀入兩個庫(環境),一個用來設置最好的工作環境(或者說延時最小),一個用來設置最壞的工作環境(或者說延時最大)。

建立時間分析。最好-最壞分析模式中建立時間的基本計算公式與單一分析模式下建立時間的基本計算公式一致,不同點在于計算建立時間所使用的工作環境不同,在計算建立時間過程中靜態時序分析工具調用邏輯單元的最大(max)延時時序庫,并用來檢查時序路徑最大延時是否滿足觸發器建立時間。如圖34.

圖34

保持時間分析。同樣,最好-最壞路徑分析模式中保持時間的基本計算公式與單一分析模式下保持時間的基本計算公式一致。不同點在于計算保持時間所使用的工作環境不同。在計算保持時間過程中,靜態時序分析工具調用邏輯單元的最小(min)延時時序庫,并用來檢查時序路徑最小延時是否滿足觸發器保持時間的約束。 即進行保持時間檢查時,始發點觸發器的發射時鐘延時、終止點觸發器捕獲時鐘延時和從始發點到終止點的數據路徑延時都是基于最好工作條件下所計算的路徑延延時。如圖35.

圖35

4.3OCV模式

OCV(on-chip variation)即片上誤差,在芯片變化相關工作模式下,與最好-最壞分析模式一樣,靜態時序分析工具也會同時在PVT境中的最好的和最壞的工作環境下檢查建立時間和保持時間,也就是要讀入兩個庫。

建立時間分析。OCV分析模式中建立時間的基本計算公式與其他分析模式下建立時間的基本計算公式一致,不同點在于計算最快路徑和最慢路徑所使用的工作環境不同,在計算建立時聞過程中靜態時序分析工具調用時序單元的最大延時時序庫來計算最慢路徑的延時,同時調用邏輯單元的最小延時時序庫來計算最快路徑的延時,只檢查時序路徑的延時是否滿足觸發器建立時間的約束。進行建立時間檢查時。始發點觸發器的發射時鐘采用的是最壞條件下最慢時鐘路徑,終止點觸發器的捕獲時鐘采用的是最好條件下最快時鐘路徑,而從始發點到終止點的數據路徑的延時則是在最壞條件下最慢數據路徑延時。如圖36所示。

圖36

保持時間分析。選用的路徑延遲的好壞與建立時間分析相反。

4.4考慮時序減免的OCV模式

考慮時序減免(timing derate)的OCV模式。時序減免(timing derate)的作用是很據減免(derating)系數,靜態時序分析工具會在時序路徑的每級邏輯門、連線和端口上都加上或減去一個原來延時值乘以減免系數值的延時作為最終的延時結果。設置時序減免值的目的是使時序分析結果更加符合實際情況。使用這種方式需要設置derating系數,系數值需要通過實際工程經驗總結出來。

4.5考慮時鐘路徑悲觀移除的OCV模式

考慮時鐘路徑悲觀移除(CPPR)的OCV模式。可以分為不考慮時序減免和考慮時序減免情況。

4.6 PT guide中關于三種模式的描述

建立時間分析如圖37所示。保持時間如圖38所示。

圖37

圖38

4.7其他分析模式

其他先進的分析模式如AOVC、SOCV、POCV等,后面有空再給大家介紹。

5時序分析步驟

5.1準備工作

5.1.1時鐘的非理想性

時鐘對于時序電路至關重要。在進行RTL設計時,可以認為時鐘是理想的,但在靜態時序分析的時候,必須考慮到實際的時鐘情形。時鐘模型的精度直接影響了靜態時序分析的精度。時鐘的非理想性包括:時鐘偏移(clock skew)、時鐘抖動(clock jitter)。實際情況中,振蕩器、互連、電源、負載都會影響到時鐘,導致時鐘出現偏移、抖動。

5.1.2對實際的時鐘進行建模

這些定義都是加在SDC中,先以圖39來為例說明。

圖39

考慮圖中的電路,電路中時鐘源位于芯片外部。我們將時鐘定義在芯片端口上,從時鐘源到達端口需要經過3ns左右的延時(板級走線的延時),從時鐘端口到寄存器要經過1ns左右的延時(時鐘樹的延時),對時鐘樹的延時進行建模可以采取下面的辦法。

先在端口上定義時鐘:create_clock per8.0 [get_ports clk]。

設置從時鐘源到時鐘端口的板級延時:set_clock_latency source 3 clk。

設置時鐘樹本身的延時。在布局布線之前可以采取下面的方法:set_clock_latency 1 clk。在布局布線之后,可以得到時鐘樹延時的確定值,采用如下的命令:set_propagated_clock clk。

知道時鐘不確定性(例如0.2)時建模,如圖40,此時可以:set_clock_latency 2.8 source early [get_ports clk];set_clock_latency 3.2 source late [get_ports clk]。

圖40

分頻時鐘的建模。以圖41為例(此例為2分頻時鐘)。在設計中,往往存在分頻時鐘,如果進行靜態時序分析時,直接援用create_clock來設置,則PT會將分頻后的時鐘看做是一個與源時鐘毫無關系的時鐘。這樣在分析源時鐘域與分頻時鐘域之間的信號時,可能會出現問題。正確設置分頻時鐘方法:create_generated_clock -name divide -source [get -pins U4/clk] -divide-by 2 [get -pins U4/Q]。

圖41

5.2主要流程

數據讀入:靜態時序分析工具讀入門級網表、時序約束等信息。

將電路分解為時序路徑:即將電路轉換為時序路徑的集合。時序路徑是一個點到點的數據通路,數據沿著時序路徑進行傳遞。它的起點是輸入端口或者寄存器的時鐘,終點是輸出端口或者一個寄存器的輸入引腳,每個路徑最多只能穿過一個寄存器。這樣時序路徑就可以劃分為:輸入端口到寄存器、寄存器到寄存器、寄存器到輸出端口、輸入端口到輸出端口。如下圖所示,分析其時序路徑。

計算每個路徑上面的延時:在一個路徑上,可能包含這幾類延時:連線延時(布局布線前后的延時計算方法不一樣)、組合邏輯的單位延時(影響因子有輸入信號的轉換時間,該值也決定輸入晶體管的翻轉速度、負載、單元本身的固有延時、制程、電壓、溫度等)、寄存器從clk端到Q端的延時。一個路徑上的延時是該路徑上所有連線的延時與單位延時的綜合。延時一般定義為從輸入跳變的50%時刻到輸出跳變的50%之間的時間。

檢查路徑時序約束是否滿足:路徑約束主要指的是建立時間約束和保持時間約束。在寄存器的綜合庫描述中對寄存器的D端定義了建立時間和保持時間的約束。所謂建立時間約束是指在采樣時鐘到達之前,數據應該穩定的時間;保持時間是指在時鐘到達之后,數據應該保持的時間,這樣才能保證寄存器正確地鎖存數據。對于純組合邏輯,時序分析主要檢查最大延時約束和最小延時路徑。這種情況比較簡單。

5.3構建時序分析腳本的過程、常用命令和腳本實例

5.3.1構建腳本

圖42

如圖42所示。大致過程為:(1)讀入設計的相關信息(鏈接庫、網表,如果是PR之后的靜態時序分析還需要讀入寄生參數信息);(2)設置驅動及負載。(3)定義時鐘;(4)設置建立時間和保持時間;(5)設置約束(max_load、max_trsition、max_capacitance、max_latency等);(6)分析時序(用report_timing 等檢查時序,用report_constraint 檢查是否有違例)。

5.3.2常用命令

圖43

5.3.3腳本實例

圖44

6總結

本文是一個全面的STA入門文章,STA涉及到的大部分概念都涉及到,當然比較淺顯,但是構建了一個系統的認識。后面筆者有空會陸續介紹:RC網絡、PVT、RC corner、delay的計算模型、OCV、AOCV、SOCV、POVC、PT軟件使用等知識。

-

鎖存器

+關注

關注

8文章

906瀏覽量

41508 -

門電路

+關注

關注

7文章

199瀏覽量

40167 -

施密特觸發器

+關注

關注

3文章

235瀏覽量

25878 -

555定時器

+關注

關注

37文章

317瀏覽量

67958 -

靜態時序

+關注

關注

0文章

20瀏覽量

6947

發布評論請先 登錄

相關推薦

詳解靜態時序分析的方法和流程

詳解靜態時序分析的方法和流程

評論