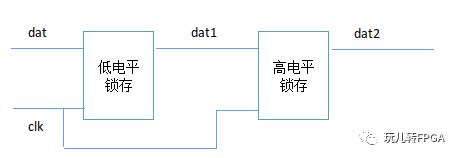

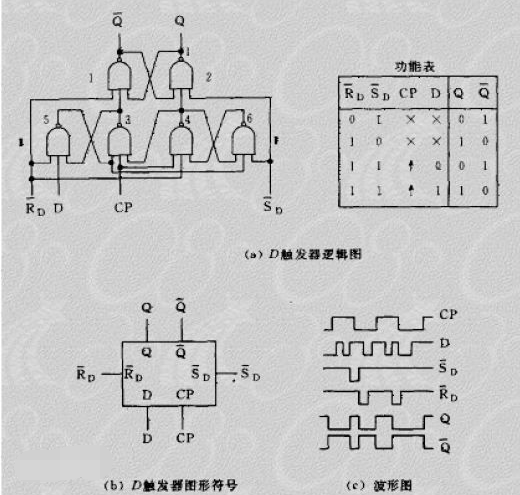

簡單的說觸發器實現邊沿出發是通過兩級鎖存器實現的,比如上升沿觸發其實是,前一級是低電平鎖存,后一級是高電平鎖存。

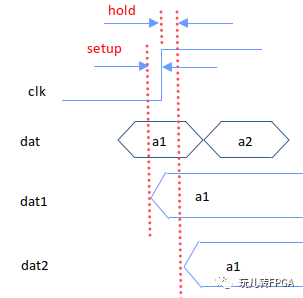

參考上圖,clk為0時,dat1 <= dat;clk為1時,dat1不變,也就是被鎖存了,同時dat2 <= dat1。下圖反映了整個過程。

參考上圖,低電平鎖存的時間叫做setup時間,高電平鎖存的時間是hold時間,如果是下降沿觸發則是倒過來。總之,前一級的鎖存就是setup時間,作用是讓數據從輸入鎖存到中間級,后一級是hold時間,作用是你讓數據從中間級輸出。setup和hold過程都需要時間,所以如果其中任何一個不滿足時序那都會輸出出錯,這也是為什么要檢查時序的原因之一。

觸發器的原理講了,但是鎖存器是如何實現的呢?

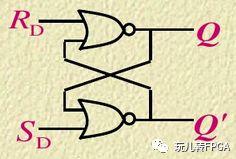

下圖是RS鎖存器的電路結構和真值表,其中SR同時為1的狀態是不允許出現的。Q是當前狀態,Q*是下一個狀態,也就是次態。

從真值表可以看出,SR狀態其中有一個為1且,互反的時候Q 是可以直接操作的Q =S;兩個都為0的時候Q*=Q,也就是保持。

如果用RS實現對輸入數據鎖存怎么操作呢?

1.輸入數據D=1,則令S=1,R=0,這時Q* = 1

2.令S=0,R=0,則D無論為多少,Q*依然不會改變

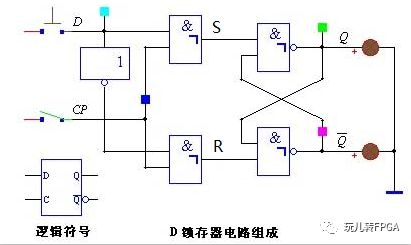

以上2步也就幫你實現了電平鎖存,具體電路如下,被稱為D鎖存器的電路:

CP就是輸入時鐘,D也就是輸入數據,與非門保證R和S不會同時為1。當CP = 1 時,輸出端的狀態隨輸入端的狀態而改變。S = D,所以Q* = D ,存入新的數據;當CP = 0 時,無論 D 如何變化,輸出端的狀態保持不變。Q * = Q n,存入的數據不變。為了觸發器可靠的工作,要求 D 輸入信號先于CP = 1 的信號,稱為建立時間 t set。

此電路為高電平鎖存,在CP前面加個反相器就成了低電平鎖存器,兩個級聯就可以實現邊沿觸發功能。

-

反相器

+關注

關注

6文章

311瀏覽量

43320 -

鎖存器

+關注

關注

8文章

906瀏覽量

41509 -

觸發器

+關注

關注

14文章

2000瀏覽量

61158 -

狀態機

+關注

關注

2文章

492瀏覽量

27541 -

CLK

+關注

關注

0文章

127瀏覽量

17171

發布評論請先 登錄

相關推薦

CMOS觸發器在CP邊沿的工作特性研究

什么是邊沿觸發器_邊沿D觸發器介紹

常用邊沿觸發器電路結構和工作原理

脈沖和邊沿觸發器區別

觸發器實現邊沿出發是如何實現的?

觸發器實現邊沿出發是如何實現的?

評論