什么是觸發器?

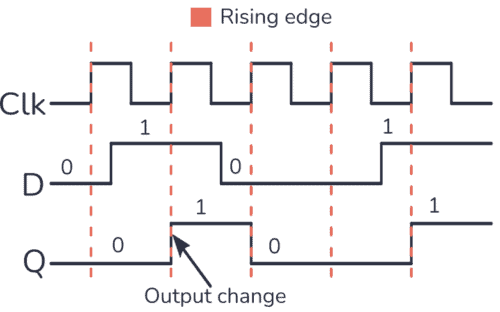

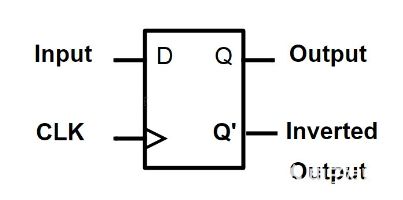

鎖存器和觸發器有時組合在一起,因為它們都可以在其輸出上存儲一位(1或0)。與鎖存器相比,觸發器是需要時鐘信號(Clk)的同步電路。D 觸發器僅在時鐘從

0 到 1(上升沿)或 1 到 0(下降沿)時存儲來自 D 輸入的新值。

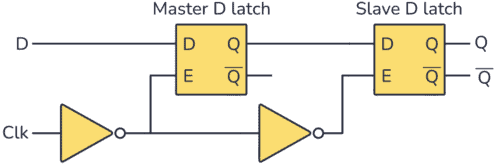

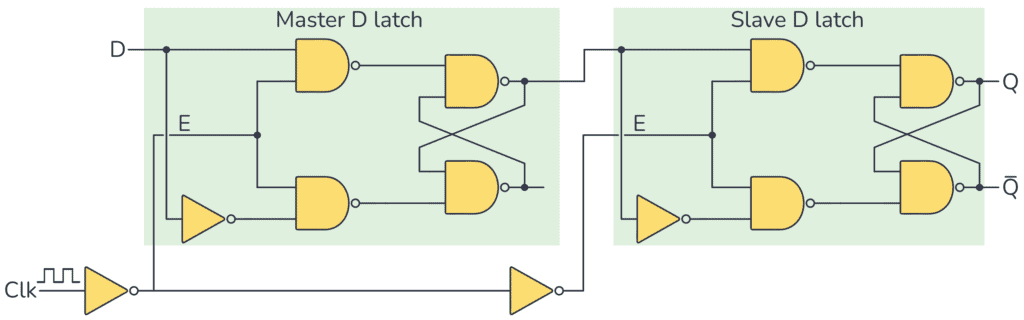

D 觸發器由兩個 D 閂鎖構成。您可以看到一個 D 觸發器,它在下面的上升沿更新:

D 觸發器主從電路

D 觸發器主從電路

該電路的時序圖如下所示。它顯示了上升沿觸發的 D 觸發器的行為。輸出Q僅在時鐘從0變為1時變為D輸入的值。

D觸發器的時序圖

D觸發器如何工作?

由于輸出 Q 僅在時鐘輸入從 0 變為 1 時發生變化,因此您將獲得以下真值表:

時鐘DQ描述

0XQ內存

(無變化)

0→1 (↑)00將 Q 重置為 0

0→1 (↑)11將 Q 設置為 1

1XQ內存

(無變化)

在真值表的第一行和最后一行中,時鐘輸入為 0 和

1。它們都不是上升沿信號,因此不會發生任何事情。Q輸出保留其具有的任何值。在這種情況下,無論D輸入具有什么值,Q輸出都不會改變,它將保持其值不變。這就是這個電路“記住”一點的方式。

看看中間的兩排。這里的時鐘輸入從0到1,所以你有一個上升沿。這意味著如果D輸入為0,Q輸出將復位為0。如果 D 輸入為 1,則 Q 輸出將設置為

1。

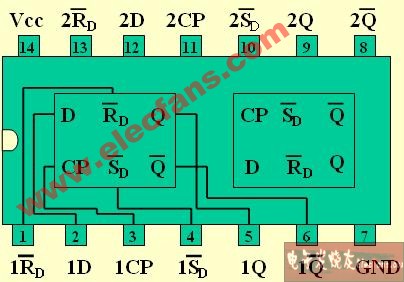

預 置

您在準備使用的芯片(例如 CD4013)中找到的 D 觸發器通常還具有設置和重置輸入,您可以使用這些輸入強制 D 觸發器在輸出上以 1 或 0

開頭。使用這些引腳有時稱為“預設”D觸發器。

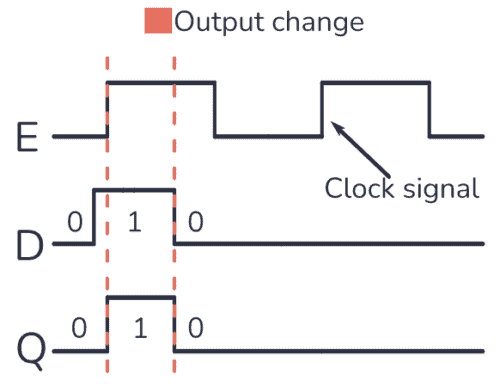

D 觸發器與鎖存器的優勢

D 鎖存電路

D鎖存器的缺點之一是,當其使能引腳為1時,其輸出可以隨時改變。因此,如果將時鐘信號應用于 D 鎖存器,則在正脈沖持續期間,Q

輸出也可能發生變化。

在上面的時序圖中,您可以看到在一個時鐘周期內,輸出既是1又是0,因為D輸入在時鐘脈沖期間發生變化。這是你不希望在時鐘數字系統中發生的事情。

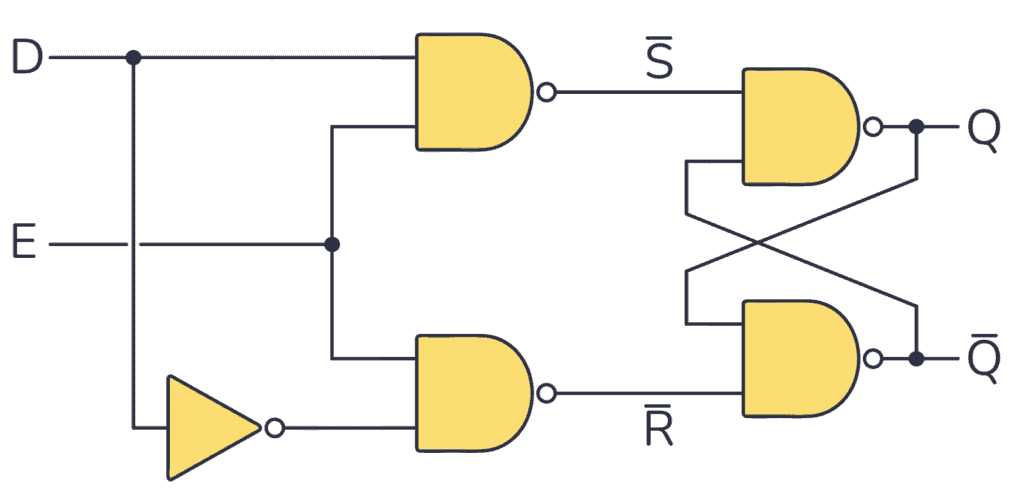

要使該觸發器僅在時鐘信號的上升沿上改變其輸出,您可以構建一個主從D觸發器電路,該電路需要兩個D鎖存器的組合,如下所示:

D 人字拖的工作原理

當Clk輸入為0時,主鎖存器的輸出將更改為D輸入的輸出。

如果Clk為0,則表示從鎖存器的使能輸入也為0。因此,此鎖存器的輸出不會發生任何事情。

但在Clk從0變為1(上升沿)的那一刻,從鎖存器的使能輸入設置為1。這意味著當Clk從0變為1時,主鎖存器輸出端的任何內容都將保存到從鎖存器的輸出中。

如果用 NAND 門構建的 D 鎖存器替換符號,您將獲得:

-

鎖存器

+關注

關注

8文章

906瀏覽量

41509 -

D觸發器

+關注

關注

3文章

164瀏覽量

47917 -

觸發器

+關注

關注

14文章

2000瀏覽量

61158

發布評論請先 登錄

相關推薦

什么是D觸發器,D觸發器如何工作的?

什么是D觸發器,D觸發器如何工作的?

評論