D 鎖存器是最常用于在數字系統中存儲數據的邏輯電路。它基于 S-R鎖存器,但沒有“未定義”或“無效”狀態問題。在本教程中,您將了解它的工作原理、其真值表以及如何使用邏輯門構建一個。

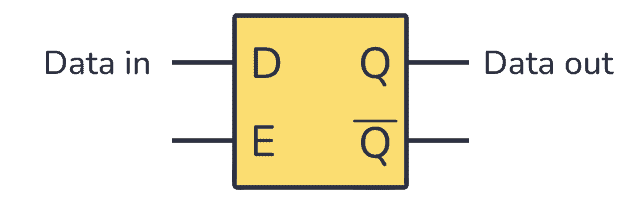

D 閂鎖符號

D 閂鎖符號

什么是 D 鎖存器?

D 鎖存器可以存儲位值,即 1 或 0。當其使能引腳為高電平時,D引腳上的值將存儲在Q輸出上。它以 S-R

鎖存器的設計為基礎,增加了一些邏輯門。您可以在下面看到一個基于 S-R 鎖存器的 D 鎖存器電路,該鎖存器采用 NAND 門構建:

D 鎖存電路

D 鎖存電路

輸入端的逆變器確保S和R輸入始終相反,以避免兩者為1的無效狀態。兩個NAND門創建一個新的輸入E(使能),允許您控制何時要將輸出更改為D輸入上的任何輸出。

這意味著輸出Q只有在使能信號為1時才能改變。如果為 0,則輸出不受 D 上任何更改的影響。

您還可以構建帶有 AND 和 NOR 門的 D 鎖存器,如下所示:

D 鎖存器還可用于在定時電路中引入延遲、緩沖器或以特定間隔采樣數據。

閂鎖和翻轉有什么區別?

術語鎖存和觸發器有時會被錯誤地用作同義詞,因為兩者都可以在其輸出中存儲位(1 或 0)。

雖然鎖存器只要啟用即可隨時更改其輸出,但觸發器是一種邊緣觸發設備,需要時鐘轉換來更改其輸出。

要構建 D 翻轉翻轉,您需要兩個 D 閂鎖,如下所示:

D 閂鎖如何工作?

由于輸出 Q 僅在 E 輸入為 1 時發生變化,因此您將獲得以下真值表:

在真值表的第一行中,E 輸入為

0。這意味著閂鎖未啟用,因此沒有任何反應。Q輸出保留其具有的任何值。無論D輸入具有什么值,Q輸出都不會改變,它將保持其值不變。這就是這個電路“記住”一點的方式。

看看接下來的兩行。此處 E 輸入為 1,因此鎖存器已啟用。這意味著如果D輸入為0,Q輸出將復位為0。如果 D 輸入為 1,則 Q 輸出將設置為

1。

分析電路

您可以通過向 S-R 鎖存電路添加三個邏輯門來構建 D 鎖存電路。在下圖中,您可以看到 D 鎖存電路在啟用時的位路徑,并且在 D 輸入上為0。

要分析上述電路,您需要記住,NAND門僅在其兩個輸入均為0時才產生1。在所有其他情況下,它給出 1。

首先,第一個NAND門的輸入為1和0,因此,其輸出為1。第二個 NAND 門的兩個輸入均為 1,因此返回 2。

第一和第二 NAND 門的輸出是代表基本 S-R 鎖存器的電路部分的輸入。考慮到這一點,您可以將位分為兩組:S-R 鎖存器之前的位(紅色)和 S-R

鎖存器產生的位(綠色)。

最后,如果你看一下第 4 個 NAND 門。您可以看到,由于第二個 NAND 門,其輸入之一為

0。該信息足以告訴您,無論其其他輸入的值如何,它都會給出 2。該位是對第三個NAND門輸入之一的反饋。由于第一個NAND門,另一個是1,因此Q輸出的結果為3 –

與輸入D相同。

當 D 為 1 時嘗試執行此操作,您將看到輸出變為 1。

從此位路徑可以得出結論,只要 E 輸入為 1,D 鎖存器就會將輸出 Q 更新為 D 輸入上的 Q。

實驗:構建自己的D鎖存電路

舉一個實際示例,您可以使用邏輯門構建基本的D鎖存電路,并使用按鈕進行測試。R1和R2是下拉電阻,以確保在未按下按鈕時輸入為0:

正如您在圖像的第 1 部分中看到的,Q 為 0(LED L1 熄滅),并且 PB1 和 PB2 均未按下。

接下來,查看推送 PB2 的第 2 部分。現在,D 輸入上有一個 1,但輸出 Q 仍為 0,因為 E 輸入尚未收到使能信號。

第 3 節顯示了如何按下 PB1,因此在 E 輸入端出現一個 1,并將位 1 從 D 放置到 Q。當 Q 為 1 時,它打開 LED L1。

當 PB1 和 PB2 恢復到第 4 節中的原始狀態時,LED L1 保持亮起,表示 Q 輸出未改變。

要更改輸出 Q,您需要再次推送 PB1。

要組裝上述電路,您需要:

四個 NAND 門(例如 CD4011)

一個非門(例如 CD4049 或 CD4069)

2x 按鈕

1x 指示燈

2x 10 kΩ電阻(R1和R2)

1x 330 Ω電阻 (R3)

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42625 -

鎖存器

+關注

關注

8文章

906瀏覽量

41509 -

D鎖存器

+關注

關注

0文章

13瀏覽量

3706

發布評論請先 登錄

相關推薦

D鎖存器快速入門教程

D鎖存器快速入門教程

評論