門控時鐘技術可以用來降低電路的動態功耗,且在一定程度上能減小電路的面積。

門控時鐘有分離門控時鐘和集成門控時鐘,現在的大多數標準單元庫中都提供了集成門控時鐘單元(ICG),且它的性能更好,應用更加簡單,因此設計中基本都采用ICG來實現門控時鐘。

之前也講述了在邏輯綜合階段如何實現門控時鐘技術,那么在物理布局階段又有什么值得注意的地方或者有什么技巧可以提升設計的性能呢?

布局階段:

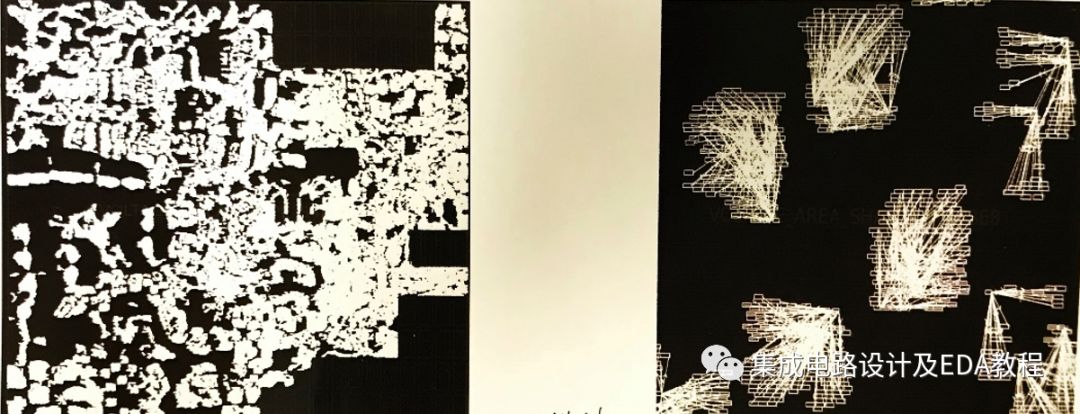

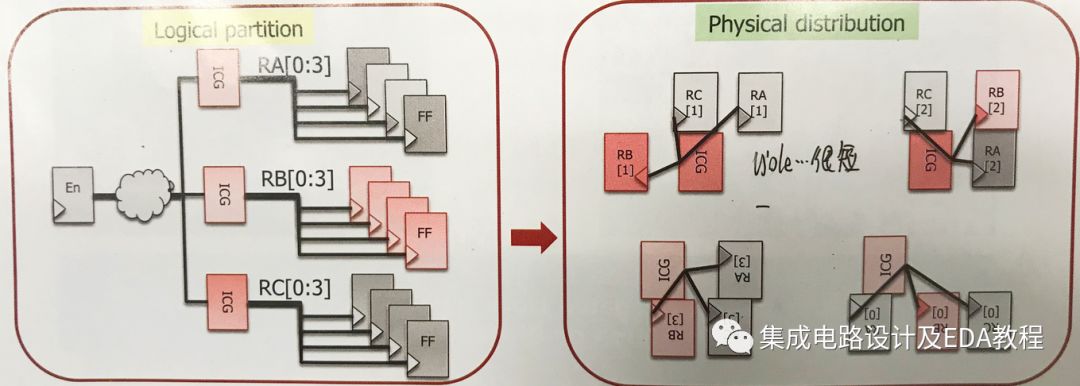

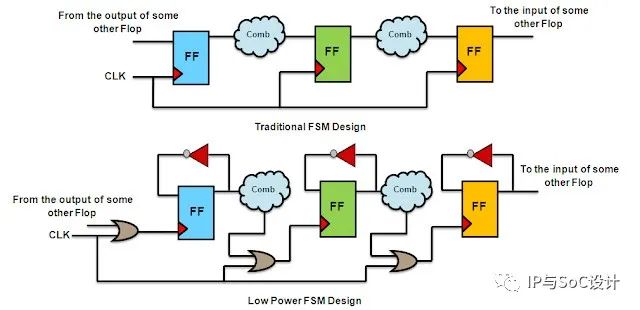

在用ICC進行布局時,需要對ICG單元和它控制的寄存器組(Register Bank, RB)進行特殊的處理。如果在布局之前不對PR工具進行任何的設置,那么布局完畢之后,所有ICG和它驅動的RB的擺放如左圖所示。

這種自由隨意的擺放方式質量很不怎么樣,制約了設計的性能。

我們預期的是右邊的物理布局,所有的ICG和它驅動的RB靠近放置,Bound到一個區域內。

右邊這種物理布局的優點:

1、RB內的所有Flop被Bound到一起,彼此間距小,因此Clock Skew小;

2、OCV的影響小,Timing更好,因為此時所有寄存器的Common Path非常長,因此OCV對Flop的影響小,體現在時序報告里面就是CRPR值更大;

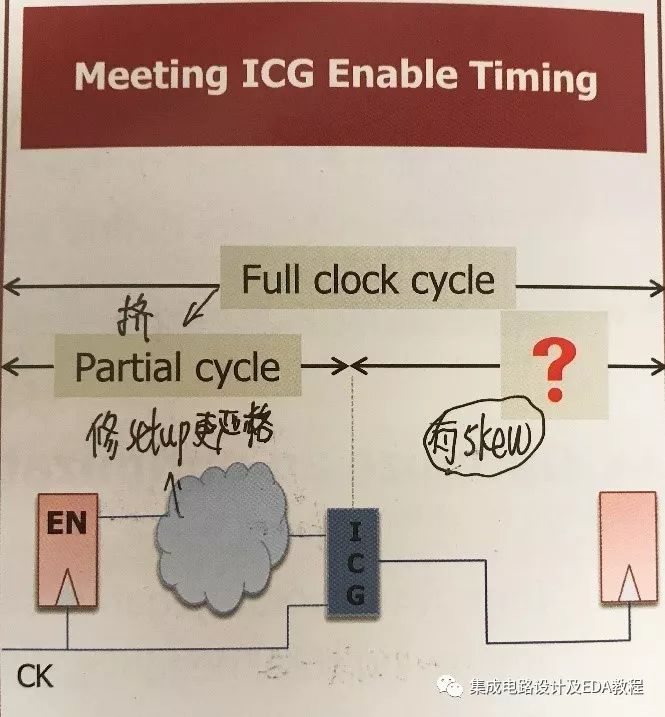

3、有利于ICG的Setup,因為此時ICG離它控制的Flop更近,latency小,所以ICG的D Pin前面的partial cycle就更長,setup相對有利。

如何在Placement中實現?

要想實現右邊的這種物理布局,在Placement之前需要對ICG單元驅動的RB設置Auto bound,也就是將它們放置在ICG單元附近一定面積范圍內,設置腳本如下:

set placer_disable_auto_bound_for_gated_clock false; #默認值為true;

set placer_gated_register_area_multiplier 5; #設置ICG單元驅動的所有寄存器全部放置在總面積5倍面積范圍內,默認值為20。

高級應用:

前面右邊的Placement方案就是最優的么?

不!!

其實最優的方案是ICG在它控制的RB中間。

那么如何實現呢?

這就需要用到Physical Aware Clock Gating技術

1、Rebuild門控時鐘結構,將那些有相同使能控制邏輯的門控時鐘單元Merge到一起;

2、之后根據ICG驅動的Register或者RB的物理位置,將ICG Split成多個ICG(如下圖所示),根據后邊控制的單元數目來選擇合適的Drive Strength的ICG。在物理布局階段,功能能根據物理信息,自動將ICG放置在與它有連接的RB中間。

DCG:

set power_cg_physically_aware_cg true

compile_ultra -gate_clock -scan -spg

ICC:

place_opt -optimize_icgs -spg

實現效果:

左圖是常規方法實現的ICG和它控制的RB的物理布局,后邊是采用Physical Aware的Clock Gating技術之后的物理布局。根據以上分析可知,這種方案的效果更好。

-

寄存器

+關注

關注

31文章

5357瀏覽量

120685 -

OCV

+關注

關注

0文章

25瀏覽量

12552 -

門控時鐘

+關注

關注

0文章

27瀏覽量

8961

發布評論請先 登錄

相關推薦

門控時鐘低功耗在Placement階段有什么技巧?

門控時鐘低功耗在Placement階段有什么技巧?

評論