我們似乎已經花了很長的路來討論與ADC相關的噪聲的各個方面。很明顯,現在是開始研究通過以下不同端口與ADC接口的好時機:電源、接地、模擬輸入、時鐘輸入和數字I/O。這顯然會與我們討論過的一些噪音交織在一起,但要考慮到更多的實際應用。我們將首先了解ADC的電源輸入,我們通常用于為ADC供電的內容,以及不同方法的一些權衡。

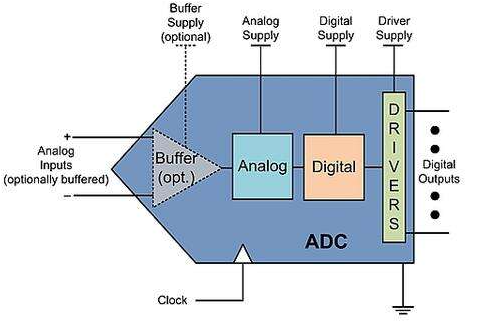

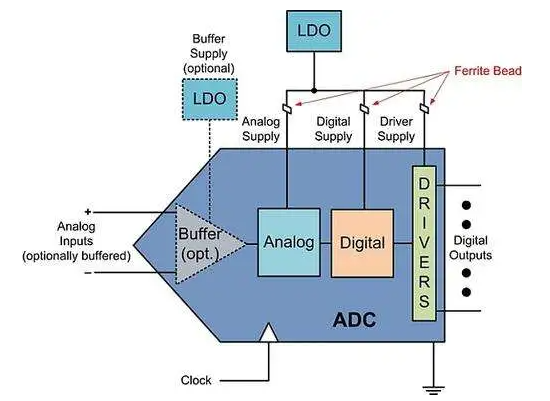

在討論如何驅動各種電源域之前,讓我們回顧一下高速ADC上通常可以找到的電源輸入。有一個可選的輸入緩沖電源域(并非在所有ADC上)、一個模擬電源域、一個數字電源域和一個驅動器電源域。

圖1

高速ADC的典型電源域

根據ADC的不同,ADC內核的ADC模擬輸入前面可以使用模擬輸入緩沖器。在某些應用中,使用輸入緩沖器可能是有益的,因為大多數高速ADC都具有開關電容輸入級。我們不會深入討論這個主題,除了關于存在緩沖區時的電源要求。

通常,數據轉換(模擬部分)和數字處理(數字部分)保持在不同的電源輸入上。模擬部分包括放大器、比較器和其他模擬電路的多級,用于執行大部分模數轉換。有人可以肯定地說,這一部分并不是真正的純粹模擬,而且是正確的。如今,許多高速轉換器都有數字輔助模擬部分。但話又說回來,人們也可以爭辯說,沒有數字電路這樣的東西,因為它最終都是由模擬電路制成的,但我跑題了......回到模擬電源。

通常,出于隔離原因,模擬電源有自己的輸入。這同樣適用于數字部分。每個模塊中都有不同部分的電路以不同的頻率工作,保持電源域獨立有助于防止這些頻率在兩個部分之間來回移動。這些部分之間的串擾會導致性能下降,這可能表現為ADC的SNR(噪聲性能)或SFDR(雜散性能)。

以類似的方式,驅動器電源域通常與轉換器的其他電源域分開。根據特定類型,輸出驅動器可能是噪聲進入轉換器的潛在路徑,也可能是噪聲源。例如,在具有CMOS輸出的ADC中,較大的開關瞬變會產生噪聲,在特定情況下可能會導致ADC出現性能問題。對于通常與采用JESD204B輸出的高速串行ADC一起使用的CML輸出驅動器,最好保留一個單獨的域,以確保為所需的高輸出數據速率(高達12.5 Gbit/s)提供最佳電源條件。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17822瀏覽量

251232 -

驅動器

+關注

關注

53文章

8267瀏覽量

146793 -

adc

+關注

關注

99文章

6530瀏覽量

545379

發布評論請先 登錄

相關推薦

使用AD9219-65M ADC四個通道輸出不正確

使用AD9219-65M ADC四個通道輸出通過后端解串后始終為0X200是為什么?

設置高速ADC的共模輸入電壓范圍(中文)

tas5731evm評價模塊

TAS5717/19的集成電容數字音頻功率放大器

關于ADC 輸入緩沖器和保護技術分析

與ADC接口:電源,第4部分

ADC接口:電源,第2部分

ADC 電源:輸入

ADC 電源:輸入

評論