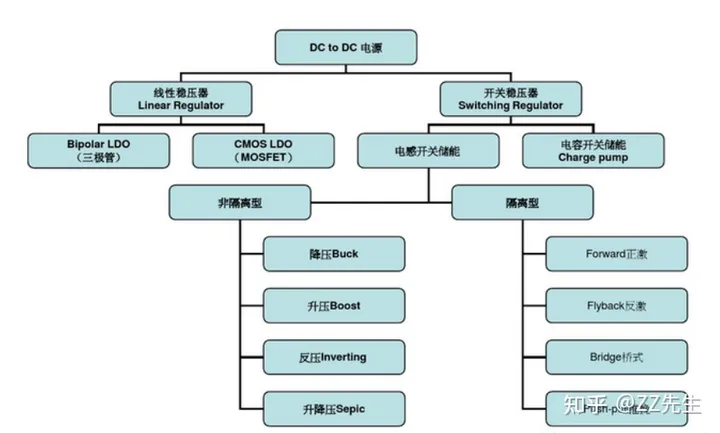

本文旨在幫助設計人員了解DC-DC補償的工作原理、補償網絡的必要性以及如何使用正確的工具輕松獲得有效的結果。該方法使用LTspice中的一個簡單電路,此電路基于電流模式降壓轉換器的一階(線性)模型。使用此電路,無需執行復雜的數學計算即可驗證補償網絡值。

背景知識

設計DC-DC轉換器時,應仔細選擇FET、電感、電流檢測電阻和輸出電容等元件,以匹配所需的輸出電壓紋波和瞬態性能。在設計功率級之后,閉合環路也很重要。DC-DC電源包含一個使用誤差放大器(EA)的負反饋環路。在負反饋系統中傳播的信號可能會在其路徑中遇到極點和零點。單個極點會使信號相位減小約90°,并使增益斜率減小-20 dB/Dec,而單個零點會使相位增加約90°,并使增益提高+20 dB/Dec。如果信號的相位減小-180°,則負反饋環路可能變成正反饋環路并發生振蕩。保持環路穩定并避免振蕩是電源的設計準則。

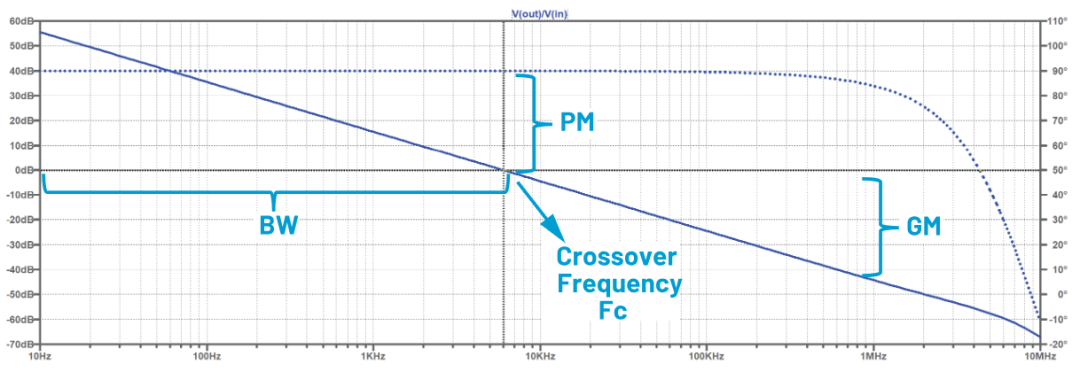

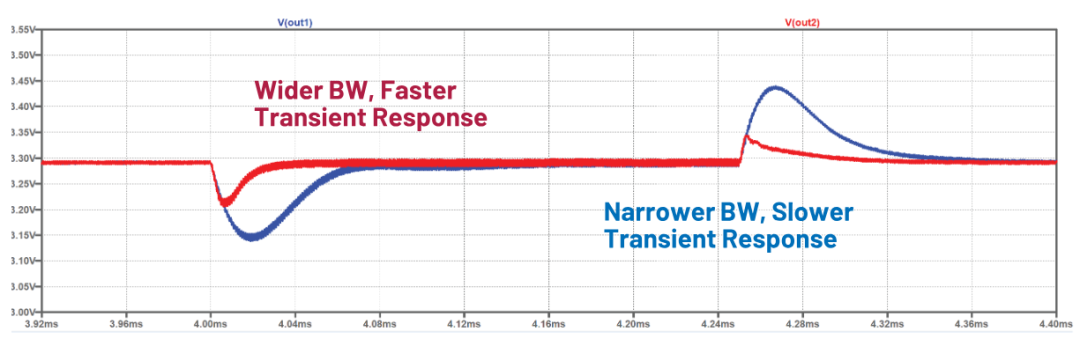

測試DC-DC穩定性的方法有兩種。第一種是頻率響應分析(FRA),此方法將會創建波特圖。第二種方法是時域分析,此方法將會使負載電流發生瞬變,并可觀察到輸出電壓的欠沖和過沖響應。為了實現穩定的設計,應確保避免相位降低-180°的情況,并保持相位裕量(PM)大于45°。相位裕量為60°是較為理想的情況。當電源設計的帶寬(BW)較寬時,器件對電流負載變化的響應會更快。電源的帶寬是0 dB增益與頻率軸交點的頻率。該頻率也稱為交越頻率Fc,可觀察到其相位高于45°。DC-DC轉換器的帶寬是其開關頻率Fsw的導數,通常在Fsw/10 < Fc < Fsw/5的范圍內。越趨近于Fsw/5則意味著帶寬越寬,實現起來也會更難。帶寬越寬,相位越低,因此需進行設計權衡。增益裕量(GM)是指Fsw/2和–180°處的負增益,-8 dB或更高的值將能很好地衰減可能的開關噪聲,或減小相移-180°時的增益可能性。我們希望以-20 dB/Dec的斜率穿過0 dB點。

圖1.波特圖,顯示了帶寬、相位、

增益裕量和0 dB時的交越頻率Fc

圖2.電源帶寬越寬,

器件對電流負載變化的響應越快

功率級LC濾波器

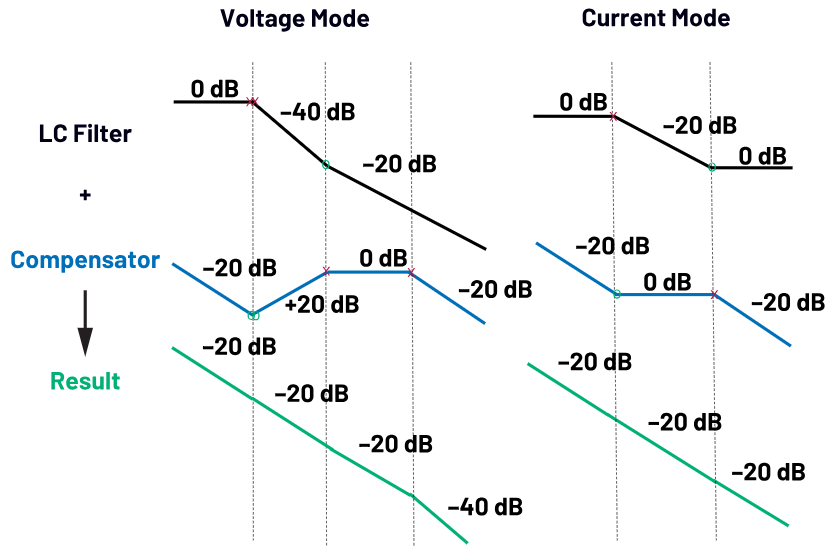

功率級LC濾波器是指給定拓撲(降壓、升壓等)的電感和等效輸出電容。各種拓撲常用的架構有兩種:電壓模式(VM)和電流模式(CM)。VM架構和CM架構中的同一LC濾波器會產生不同行為。簡單說來,用于VM架構的LC濾波器會增加兩個極點。CM架構額外包含一個電流檢測反饋路徑,有助于消除LC濾波器的雙極點。VM架構則難以做出補償,因為LC雙極點需要更多的零點來抵消雙極點效應,因此需要更多元件。

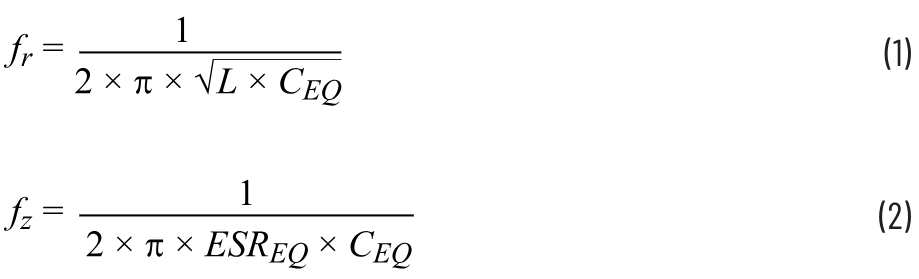

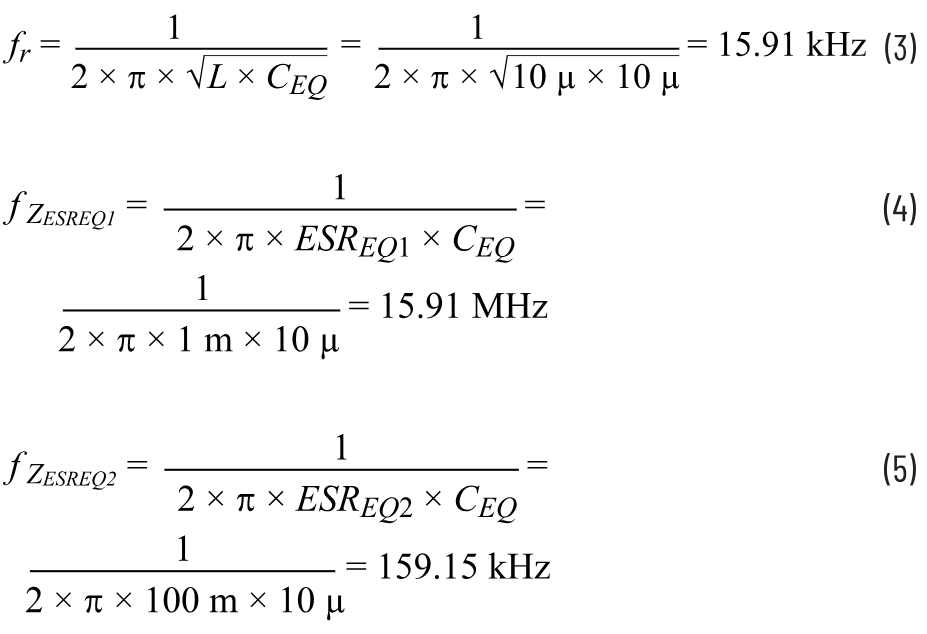

降壓VM架構和LC頻率行為由于等效輸出電容CEQ及其等效ESR (ESREQ),LC濾波器將導致增加兩個極點和一個零點:

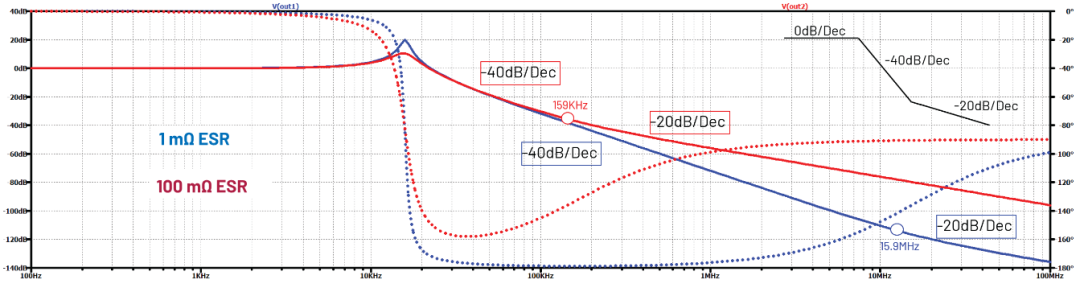

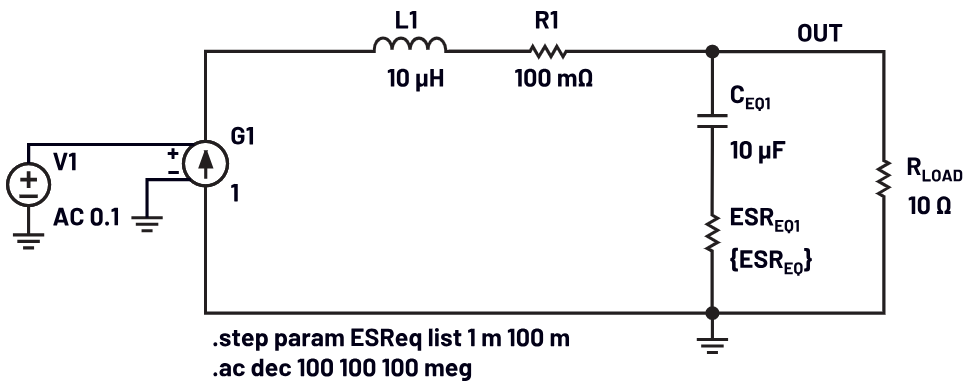

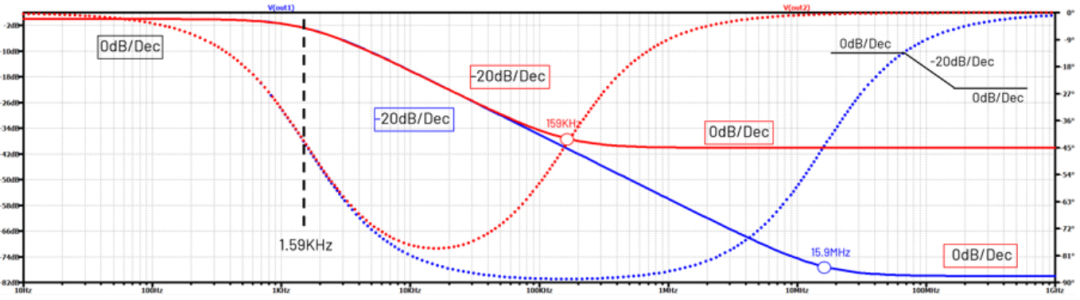

LC濾波器雙極點位置與LC寄生電阻無關。電感和等效電容值越大,雙極點位置就會越靠近頻率軸的原點0 Hz。如果CEQ及其ESREQ值較高,則LC濾波器零點頻率位置將向左移動或更接近0 Hz。VM中的LC濾波器行為如圖3所示,其仿真結果如圖4所示。紅線和藍線之間的差異是電容ESR值造成的,分別為1 mΩ和100 mΩ。Fr位置相同,因為LC值沒有改變,但零點位置因ESR值的改變而變化。

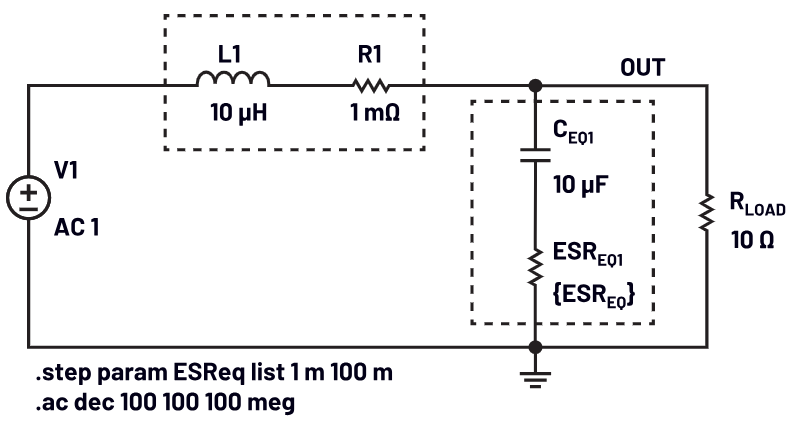

圖3.VM降壓LC濾波器行為的簡化模型電路對于VM架構,LC濾波器會增加兩個極點和一個零點。頻率響應形狀始終相同:斜率變化為0 dB/Dec至-40 dB/Dec至-20 dB/Dec。極點和零點的位置取決于電感、總電容和等效電容ESR值。

圖3.VM降壓LC濾波器行為的簡化模型電路對于VM架構,LC濾波器會增加兩個極點和一個零點。頻率響應形狀始終相同:斜率變化為0 dB/Dec至-40 dB/Dec至-20 dB/Dec。極點和零點的位置取決于電感、總電容和等效電容ESR值。

圖4.簡化VM降壓LC濾波器行為的仿真結果

圖4.簡化VM降壓LC濾波器行為的仿真結果

CM架構和LC頻率行為可以通過電壓控制電流源來仿真CM中LC濾波器的頻率行為,如圖5所示。ESR在兩個數值間步進,以凸顯零點位置的差異。由下式計算得出CM降壓架構中LC濾波器的極點位置:

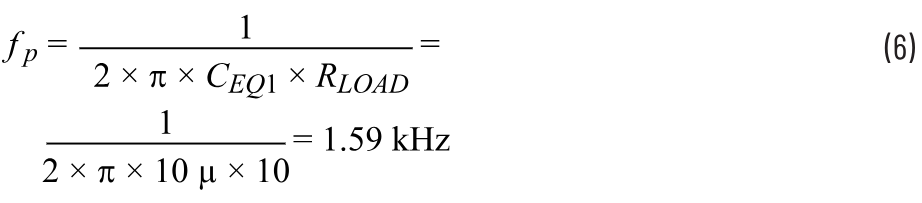

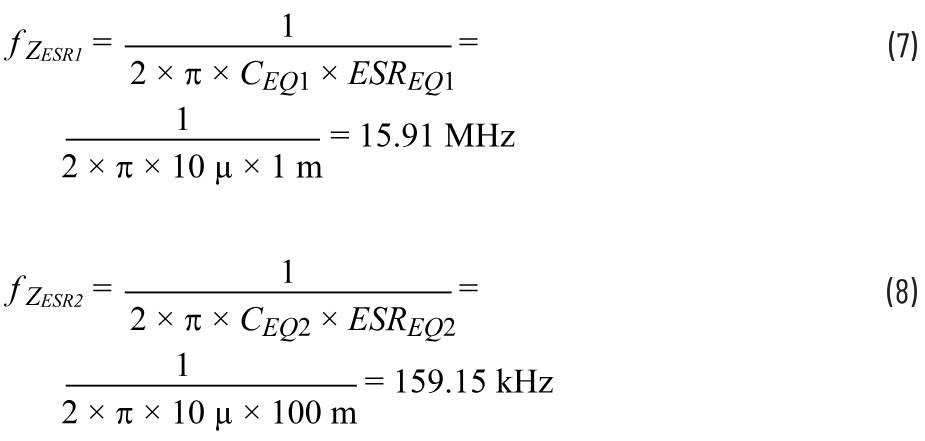

RLOAD為負載電阻,即輸出電壓與電流的比值。例如,若輸出電壓為5 V,負載電流為2 A,則RLOAD將等于5 V/2 A = 2.5 Ω。零點位置由等效輸出電容及其等效ESR決定。同VM架構類似,1 mΩ和100 mΩ ESR對應的兩個零點值為:

圖5.電壓控制電流源用作CM降壓的模型;

ESR為步進式

對于CM架構,LC濾波器會增加一個極點和一個零點。頻率響應形狀始終相同:斜率變化為0 dB/Dec至-20 dB/Dec至0 dB/Dec。極點/零點的頻率位置取決于輸出電容、等效ESR和負載值。

補償器

LC濾波器會導致相位損失。補償網絡用于補償相位,通過向環路添加極點和零點,可抵消LC濾波器引起的相位滯后/超前和增益變化。

圖6.CM降壓LC濾波器頻率響應形狀的仿真

圖6.CM降壓LC濾波器頻率響應形狀的仿真

電流模式架構補償器

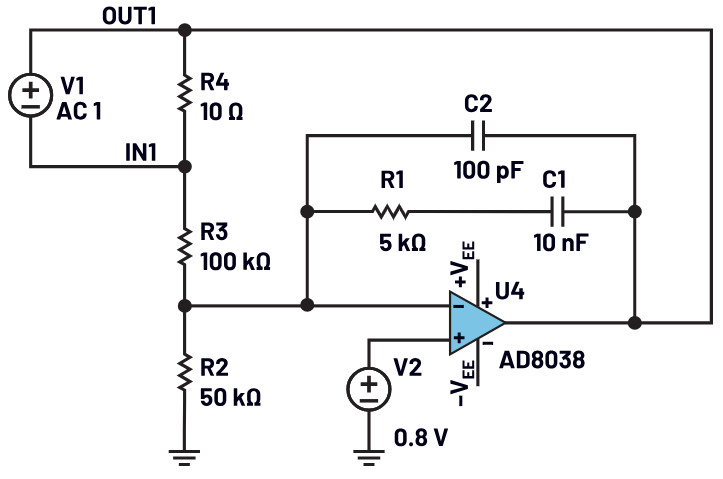

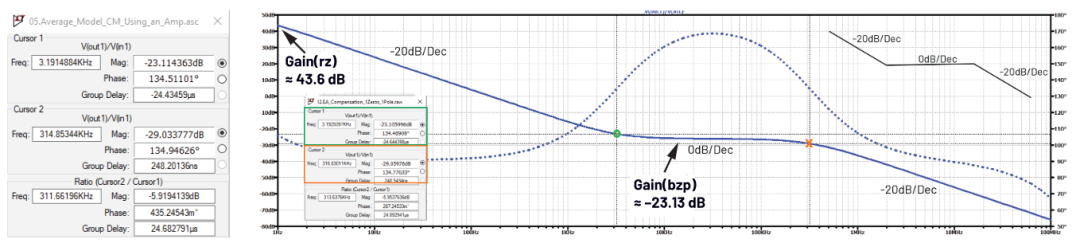

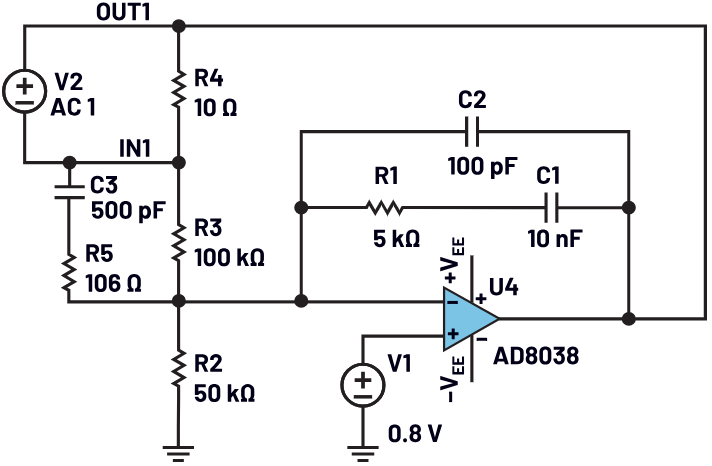

CM架構補償器稱為2型補償器。圖7所示為2型補償器。AD8038為EA,R2、R3為反饋電阻,R4為電阻,V1通過R4將頻率注入環路以執行FRA。補償網絡由R1、C1和C2組成。

圖7.LTspice中的2型補償器模型

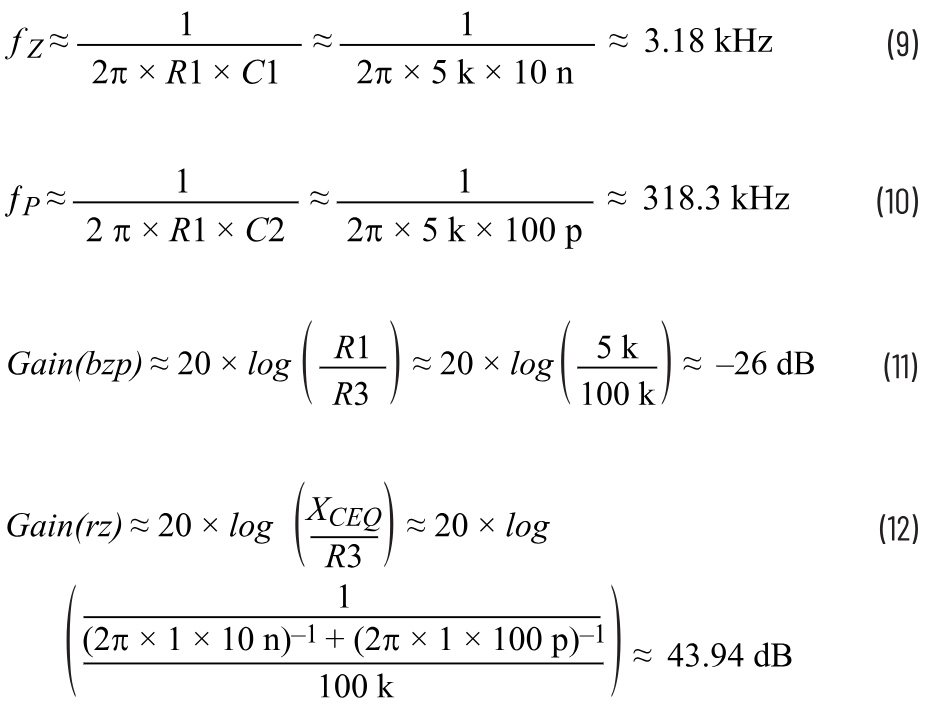

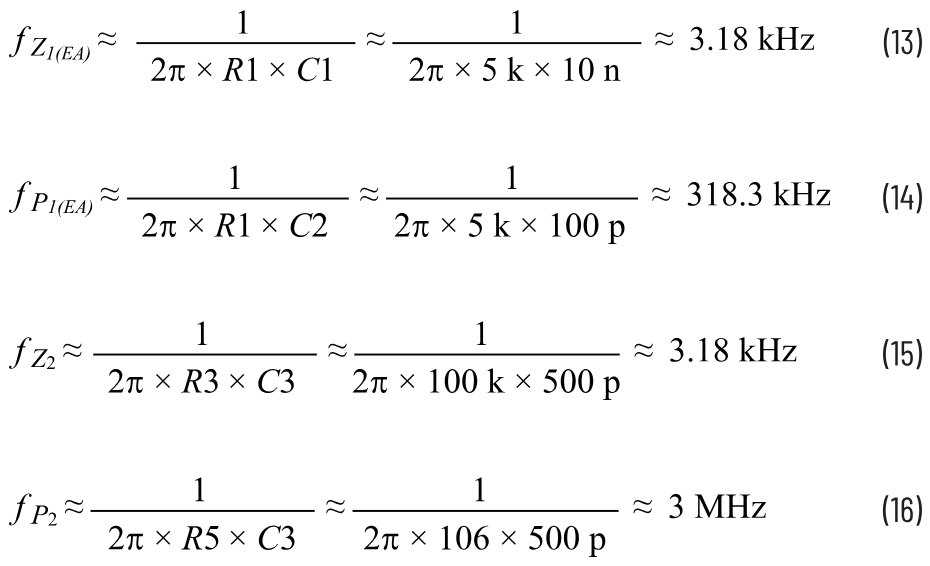

零點/極點和增益的預期結果:

Gain(bzp)為零點和極點之間的增益,由R1與R3的比值決定。Gain(rz)為直流增益。在上述計算過程中,原點處的極點使用1 Hz的頻率;因此,補償器的初始斜率為-20 dB/Dec。圖8顯示仿真結果與計算值密切相關。

圖8.2型補償器仿真結果、

圖8.2型補償器仿真結果、

極點/零點位置和斜率變化

VM架構補償器VR

在VM架構中,補償器有一個額外的極點/零點組合,可抵消LC濾波器的額外相位損失。圖9顯示了用于VM架構的3型補償器網絡,圖10顯示了其頻率響應。

圖9.VM架構補償器,也稱為3型補償器

C3和R5是與頂部反饋電阻R3并聯的兩個附加元件。3型補償器的極點和零點位置為:

請注意,Fz1(EA)和Fz2被置于同一頻率。有時會使用類似3型的補償方案,即在頂部反饋電阻上設計單個電容,以剔除高頻極點,補償器斜率將繼續保持在0 dB。

圖10.VM補償器電路的LTspice交流仿真結果

圖10.VM補償器電路的LTspice交流仿真結果

調整時間常數一致

一種閉合環路的方法是讓LC濾波器極點/零點的時間常數與補償器零點/極點的時間常數一致,這樣就可以實現相互抵消,并提供總計-20 dB/Dec的增益斜率。

圖11.調整對齊VM和CM中LC濾波器

與補償器的極點和零點

圖12.LTC3981 28 V至5 V/6 A設計原理圖,

圖12.LTC3981 28 V至5 V/6 A設計原理圖,

其中補償網絡未對齊

圖13.補償網絡未對齊,開關頻率與設計頻率不同,

瞬態測試引起振蕩

使用一階平均模型對齊極點/零點

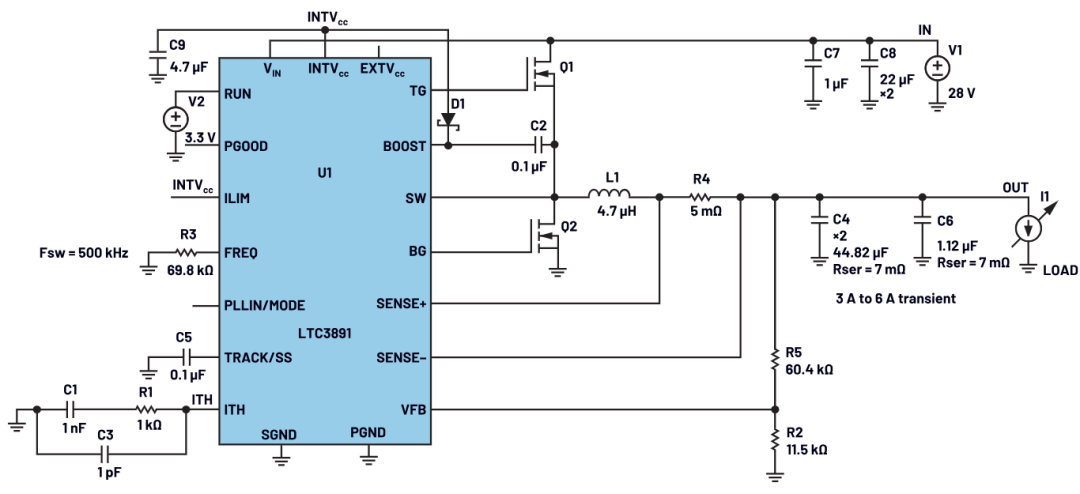

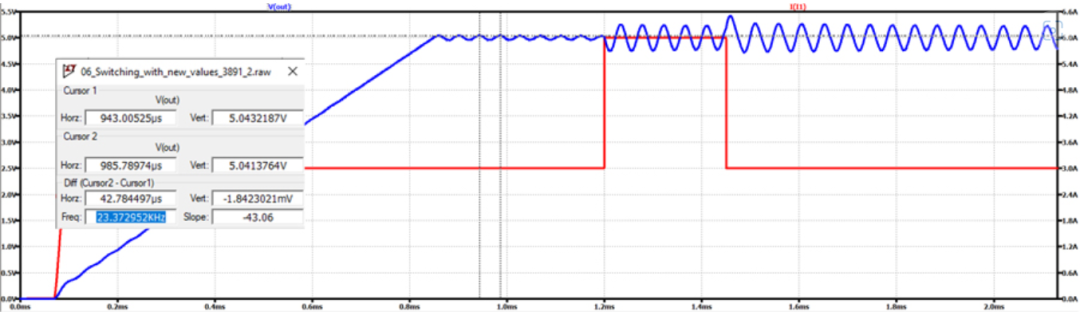

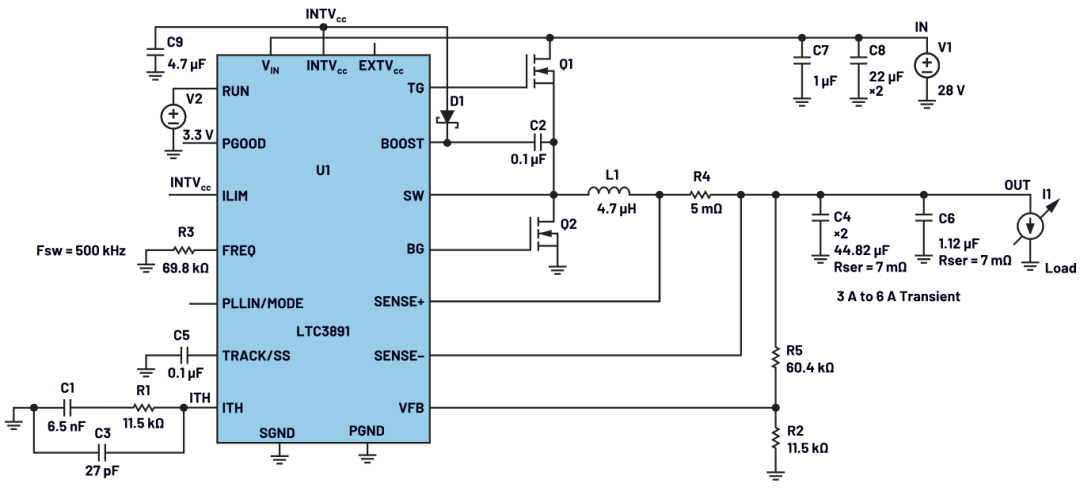

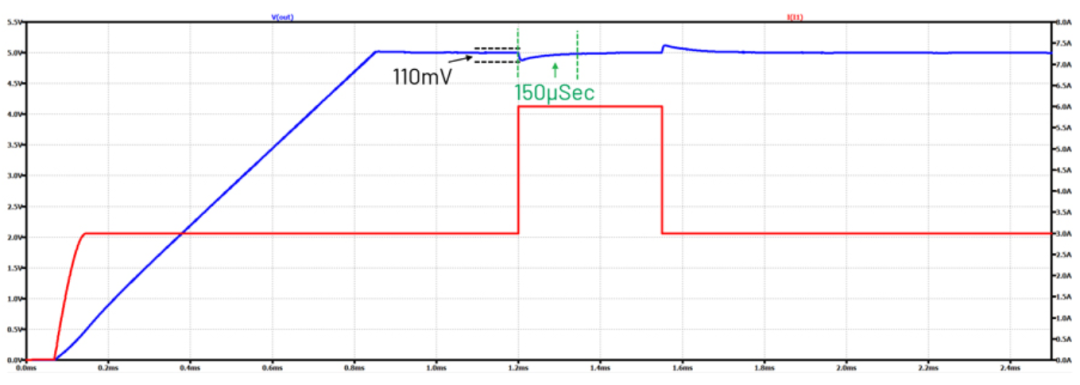

LTC3891是一款CM控制器,用于將28 V降壓至5 V/6 A。ITH引腳上的補償網絡與等效輸出電容及其總ESR不一致,導致在瞬態負載測試中出現振蕩。輸出端測得的開關頻率為23 kHz,而不是預期的500 kHz。

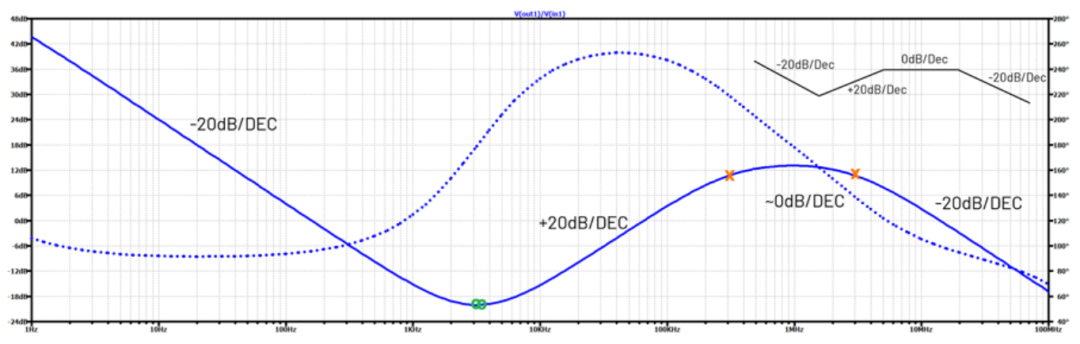

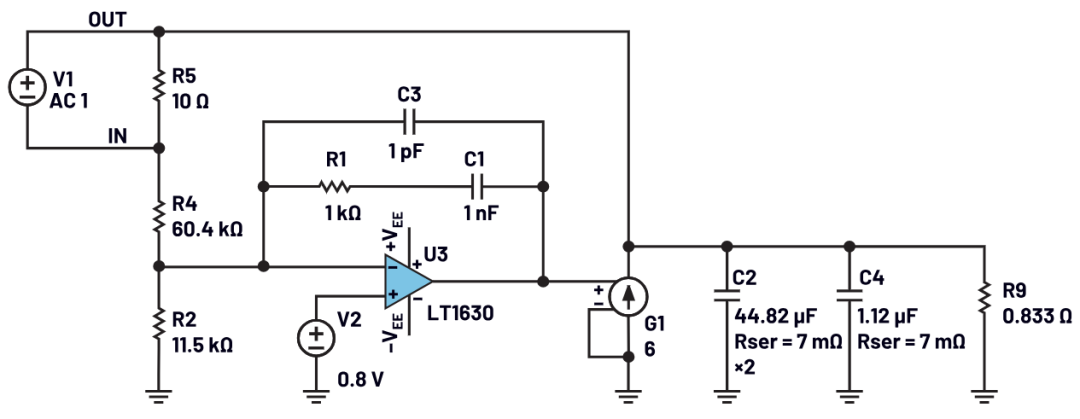

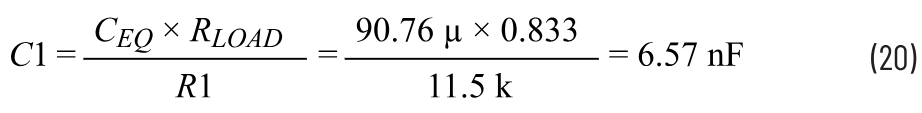

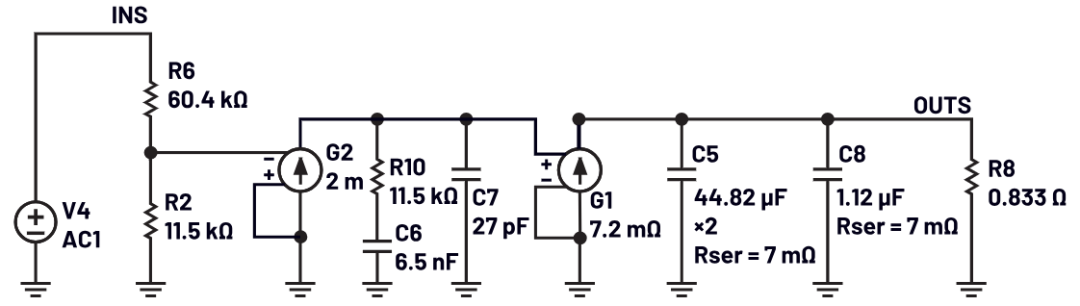

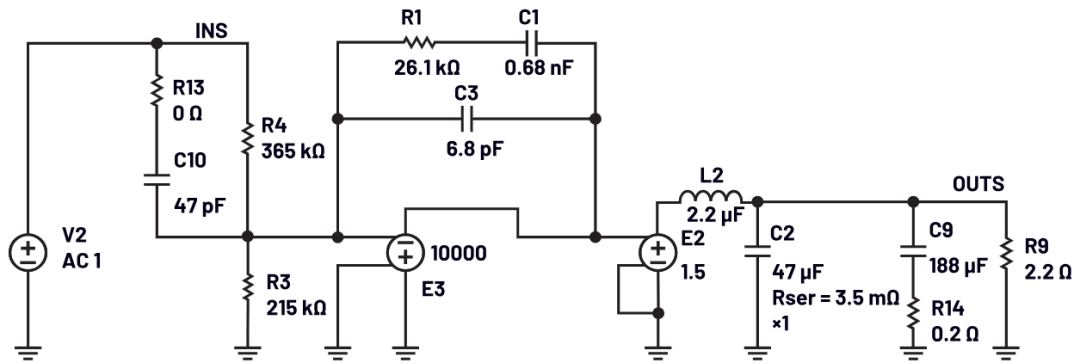

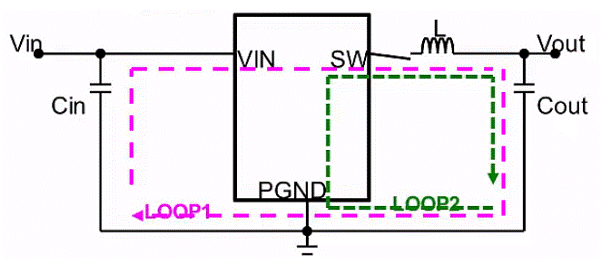

將功率級和補償器這兩個電路組合在一起,形成一個模擬CM架構閉環行為的線性電路。

圖14.線性電路模擬CM穩壓器,補償網絡未對齊

圖14.線性電路模擬CM穩壓器,補償網絡未對齊

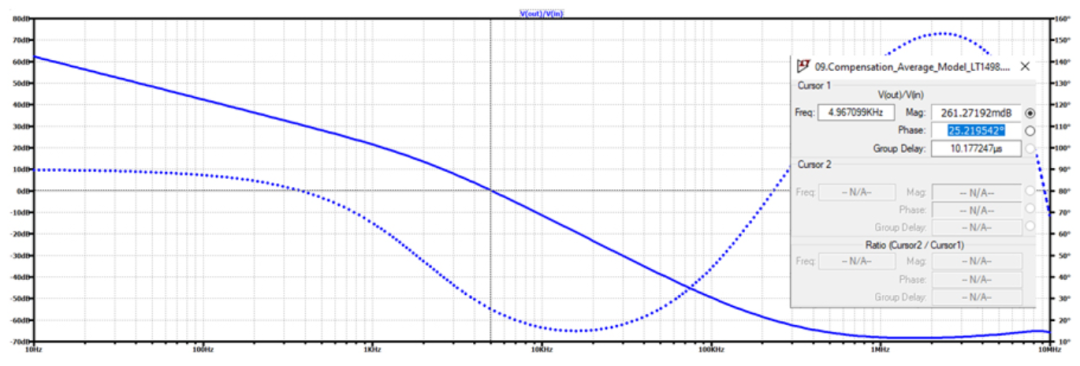

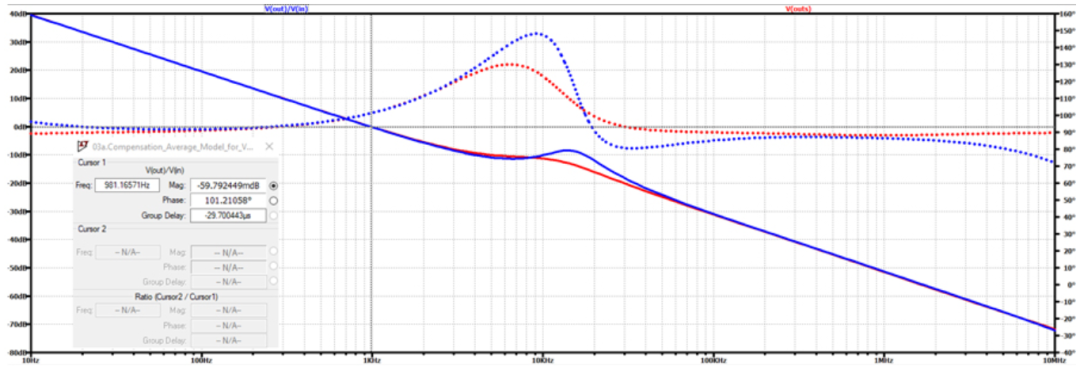

圖15.線性模型的仿真結果,

使用放大器作為誤差放大器,常數不一致

G1是電壓控制電流源。其值為6,意味著如果G1正輸入端的電壓為1 V,則其輸出端將提供6 A電流。該電路的頻率響在不同速率下顯示不同的斜率變化,0 dB交越頻率處的相位為25°。因此,時域中存在振蕩。

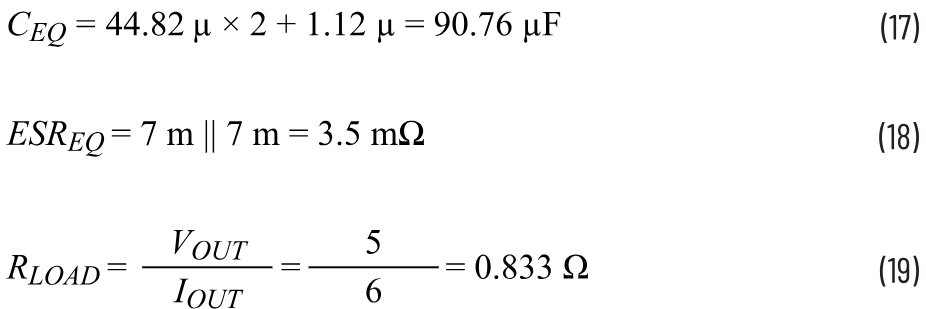

為使時間常數一致,我們首先需要知道功率級的CEQ、ESREQ和RLOAD。

R1由設計人員選擇;這里選擇R1 = 11.5 kΩ,與R3相同。R1 × C1(z) = CEQ× RLOAD(p)。求解C1:

圖16.極點/零點調整對齊后,

使用放大器作為EA的線性模型

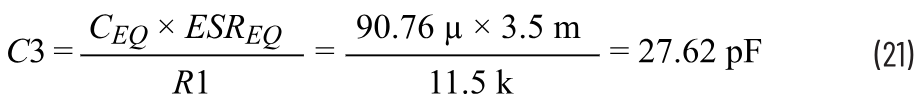

CEQ× ESREQ(Z) = R1 × C3 (P),補償器極點的時間常數由R1 × C3決定。求解C3:

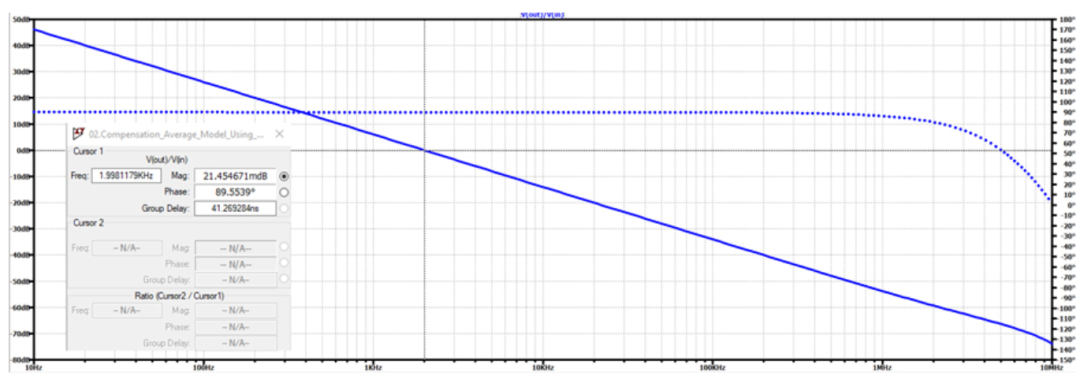

使用此平均模型時,正確仿真結果顯示-20 dB/Dec的斜率和90°的相位。如果結果不同,則需要驗證計算。

使用運算放大器作為EA的缺點之一在于無法正確預測帶寬。盡管如此,此方法仍然非常實用,可幫助驗證一致計算。可以通過增加R1電阻值來提高帶寬。如果R1增加,則補償器電容需要按相同比例減小,以保持時間常數一致。R1不可無限制地增加,因為增益越高,0 dB時的相位裕量越低。當時間常數一致時,相位將始終保持為90°。需要利用IC開關模型驗證計算值,然后還需進行瞬態響應基準測試。

圖17.極點/零點調整對齊后得到的結果,

斜率為-20 dB/Dec,90°高相位值

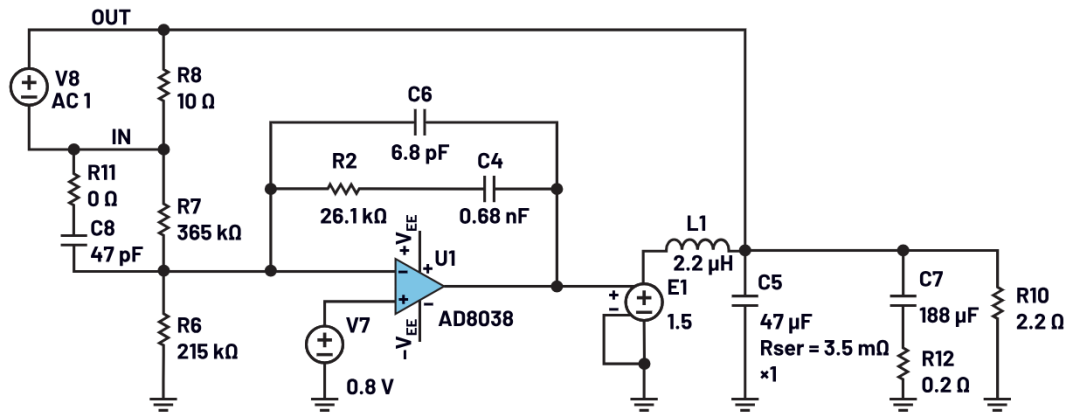

圖18.ITH引腳上的補償網絡

與輸出LC濾波器保持一致

圖19.保持補償網絡和LC濾波器的相關數值一致后得到的仿真結果,顯示了對負載瞬變的穩定響應

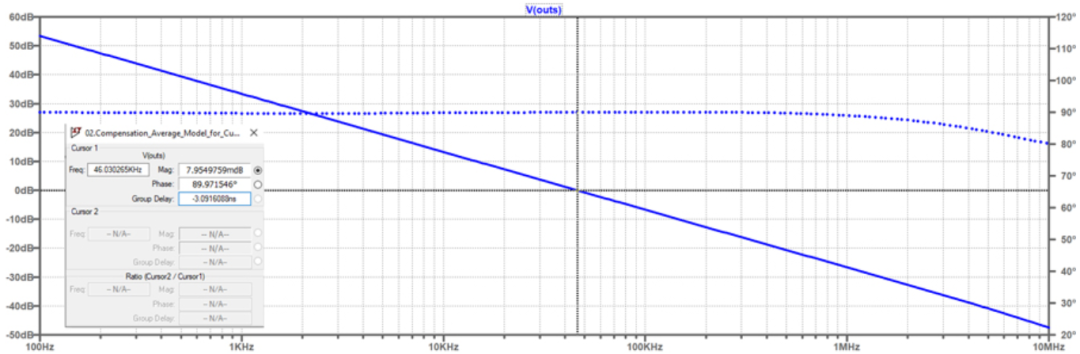

用另一個電壓控制電流源替代運算放大器,可以簡化該線性模型,并提升其準確率。LTC3891數據手冊提供了跨導值,1.2 V下gm = 2 mmho。G1正輸入為1 V,因此新的電流值將為7.2,因為7.2 A/1.2 V = 6 A/V。新電路(圖20)的仿真如圖21所示,預測帶寬將為46 kHz。

圖20.更為簡單的對齊電路,使用了G2作為誤差放大器,其相應的gm值取自數據手冊

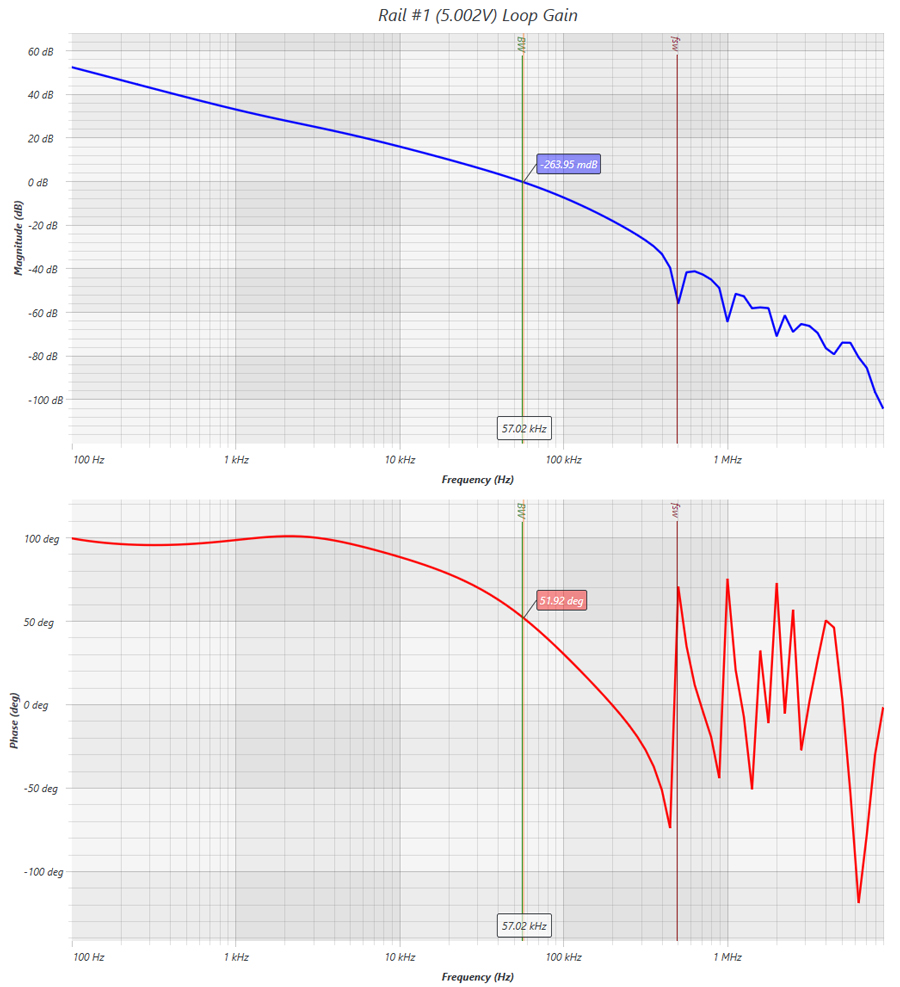

LTpowerCAD預測帶寬為57 kHz,相位裕量為52°。增益圖看起來非常相似。相位起初非常接近,但在10 kHz之后無法正確預測。

右半平面零點(RHPZ)

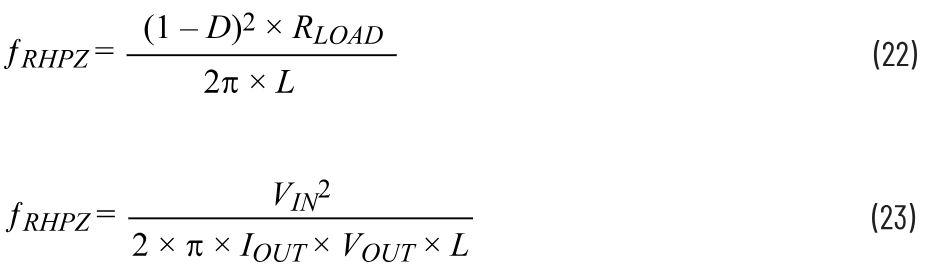

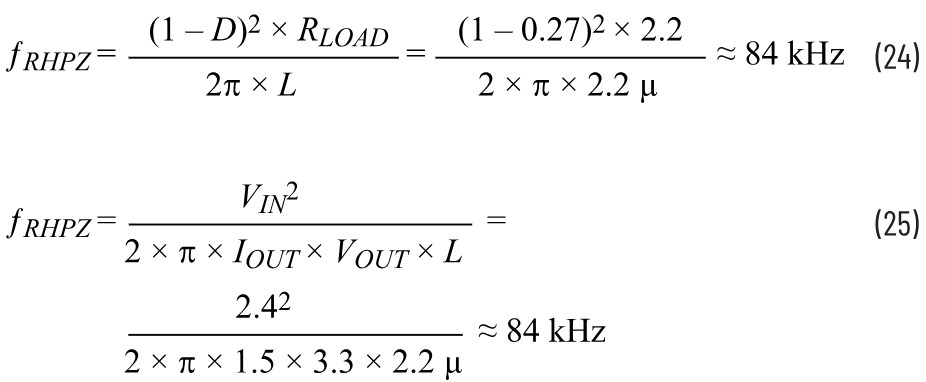

RHPZ零點會增加20 dB的增益,并使相位減小約90°,因此無法進行補償。對于在連續導通模式下工作的升壓、降壓-升壓和sepic等拓撲,這個零點會限制帶寬。RHPZ的頻率位置計算如下:

圖21.使用G2作為EA的更簡單電路模型可提供更寬的帶寬

圖21.使用G2作為EA的更簡單電路模型可提供更寬的帶寬

圖22.圖18中LTC3891設計的LTpowerCAD結果

圖22.圖18中LTC3891設計的LTpowerCAD結果

通常,在這些公式中,"電感"是需要由設計人員進行權衡取舍的唯一變量。RHPZ位置限制了設計的帶寬,因為環路需要在F(RHPZ)/10的頻率閉合。此處提供的線性模型電路未考慮RHPZ。

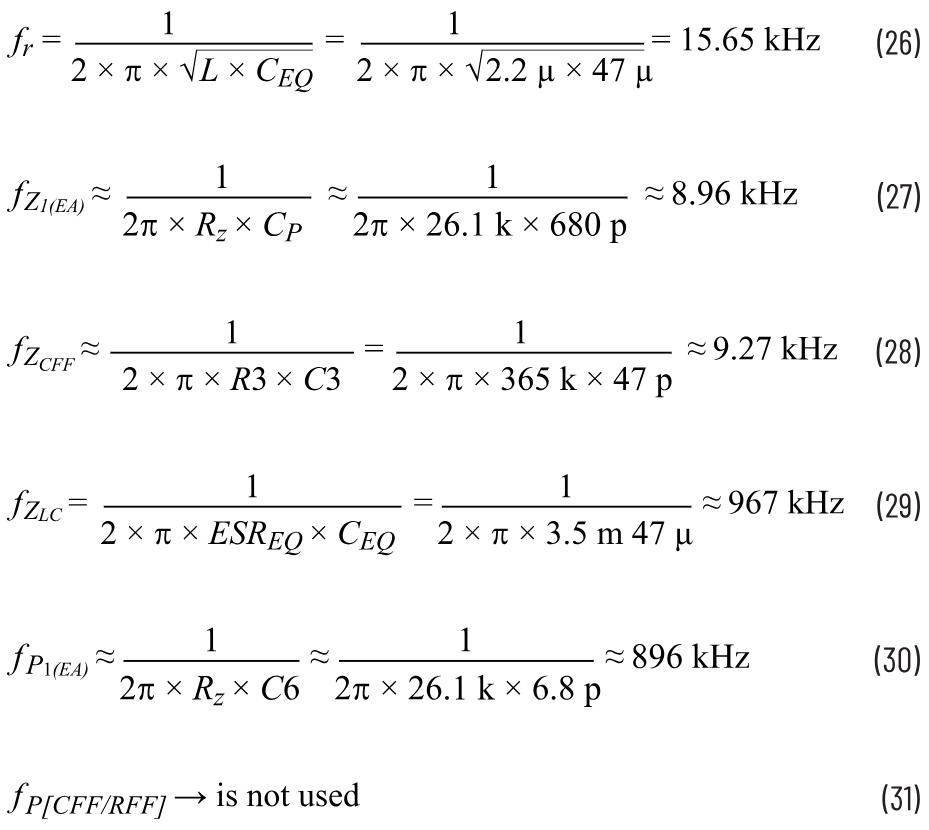

電壓模式降壓-升壓示例

LTC3533是一款VM架構降壓-升壓型穩壓器。在升壓模式下,其RHPZ將成為限制因素。當輸入為2.4 V的VIN(MIN)時,LTC3533演示板配置為3.3 V/1.5 A。在這種情況下,占空比D將為D = (Vo – VIN)/ Vo = (3.3 – 2.4)/3.3 ≈ 0.27。RLOAD = VOUT/IOUT = 3.3/1.5 = 2.2 Ω。

RHPZ位置可以通過以下任一公式求得:

閉合環路的安全位置將是在8.4 kHz。Rt設置開關頻率Fsw = 1 MHz。請注意,由于缺少RFF,此補償是類似3型的補償,因此Cff不會產生額外的高頻極點。

極點和零點的位置為:

LC濾波器的雙極點位置在15.65 kHz。兩個零點Fz1和FzCff集中在一起,頻率約為9 kHz,以抵消LC濾波器的極點。此外,LC濾波器在967 kHz處形成的零點的影響被896 kHz處的極點抵消。

圖23.LTC3533演示板原理圖

圖23.LTC3533演示板原理圖

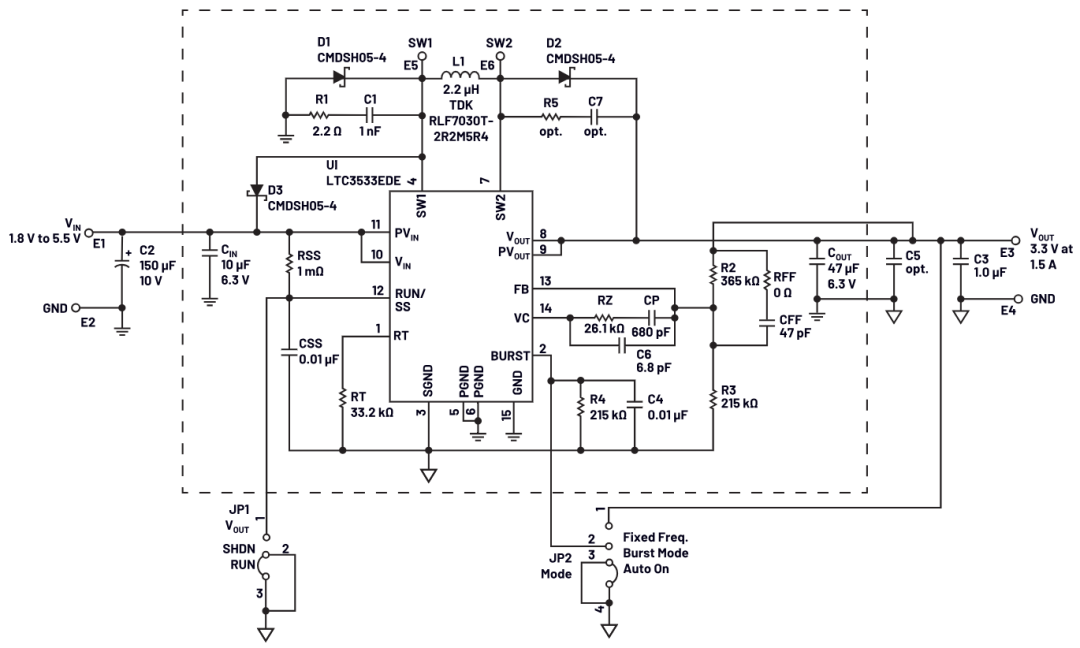

圖24.使用運算放大器作為EA的VM架構的一階模型;

圖24.使用運算放大器作為EA的VM架構的一階模型;

LTC3533演示板值

圖25.使用電壓控制電壓源的VM控制的更簡單電路

圖25.使用電壓控制電壓源的VM控制的更簡單電路

圖26.兩個電路的仿真結果

圖26.兩個電路的仿真結果

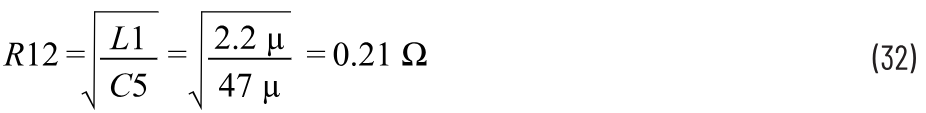

使用運算放大器作為EA的VM架構的平均LTspice電路,可用來檢查極點和零點的對齊情況。通過將電壓控制電壓源用作EA,可以進一步簡化電路。其增益值源自數據手冊中指定的誤差放大器AVOL,即80 dB。80 dB = 20log10000。因此在仿真中取用了10000。兩種電路的仿真提供了非常相似的解決方案。帶寬沒有像CM電路仿真中那樣變化。增益非常相似,相位預測值為90°,但這僅說明了可以進行正確對齊。輸出端有一個188 μF附加電容和一個0.2 Ω電阻。如圖4所示,電壓模式LC濾波器可以產生高Q,尤其是當ESR和DCR的值較低時。為確保LC濾波器具有適當的阻尼,需在輸出端額外添加一個RC,具體計算如下:

結論

LTspice電路仿真為驗證補償網絡的計算提供了一種高效可靠的方法。雖然所討論的線性模型不包括電流檢測元件、信號增益或RHPZ信息,但仿真速度快和兼容各種DC-DC拓撲的優勢將能讓相關設計人員大受裨益。此外,如果獲得的結果正確,輸出將顯示-20 dB/Dec的增益斜率和大約90°的相位。

原文轉自亞德諾半導體

-

電路

+關注

關注

172文章

5920瀏覽量

172285 -

轉換器

+關注

關注

27文章

8707瀏覽量

147219

發布評論請先 登錄

相關推薦

DC-DC直流升壓模塊的選型

升降壓電路-你會算DC-DC電感值嗎?

DC-DC升壓模塊的工作原理

24v-100v DC-DC電源設計

DC-DC 和LDO 簡單介紹

降壓型DC-DC轉換器與升壓型DC-DC轉換器的輸出紋波差異

電子技術(十九)——DC-DC

DC-DC電路設計要點及計算全解析

DC-DC轉換器電路圖 Boost升壓型DC-DC轉換器的工作原理

DC-DC的PCB設計注意的點

【世說設計】ADI拍了拍你,并獻上計算DC-DC補償網絡的分步過程教程

【世說設計】ADI拍了拍你,并獻上計算DC-DC補償網絡的分步過程教程

評論