為什么需要先進半導體封裝?

據麥姆斯咨詢介紹,人類正生活在一個以數據為中心的時代。各行各業產生的數據量不斷攀升,持續推動對高帶寬計算的需求增長。機器學習和人工智能(AI)等應用需要強大的處理能力,因此需要在芯片上更密集地布置晶體管,在封裝中需要更緊湊地互連凸點間距。后者強調了半導體封裝技術在滿足上述需求時的重要性。在此背景下,英國知名研究公司IDTechEx發布了這份關于先進半導體封裝材料及工藝的最新研究。

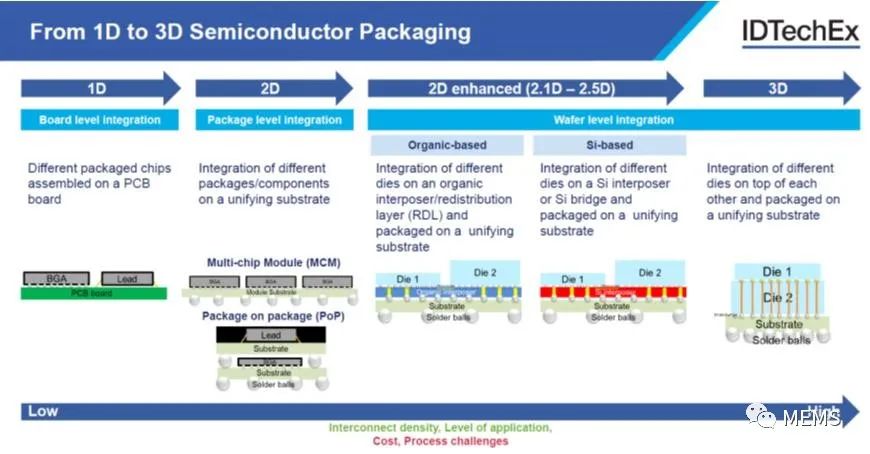

1D到3D半導體封裝

半導體封裝已經從板級集成發展到晶圓級集成,帶來了顯著的進步。晶圓級集成提供了優于傳統方案的諸多優勢,例如:提高了互連密度,為尺寸敏感應用提供了更小的占位面積,同時還增強了性能。

目前,包括2.5D IC、3D IC和高密度扇出晶圓級封裝等封裝技術,被歸類為“先進半導體封裝”,其特點是凸點間距低于100 μm,能夠實現至少10倍的更高互連密度以及更高的集成能力。

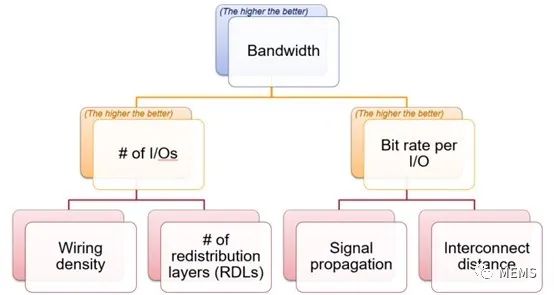

帶寬是關鍵

從封裝的角度來看,要提高帶寬,需要考慮兩個關鍵因素:I/O(輸入/輸出)總數和每個I/O的比特率。增加I/O總數需要在每個布線層/再分布層(RDL)中實現更精細的線寬/間距(L/S),并具有更高數量的布線層。另一方面,提高每I/O比特率受到芯粒(chiplets)之間互連距離和介質材料選擇的影響。這些因素直接影響著封裝系統的整體性能和效率。

影響封裝模塊帶寬的關鍵因素

釋放高帶寬:探索先進半導體封裝的材料和工藝

從材料和工藝角度深入研究如何實現更高的布線密度和每I/O比特率,揭示了介質材料選擇和適當工藝技術所發揮的關鍵作用。這些因素對封裝系統的整體性能和功能具有重大影響。

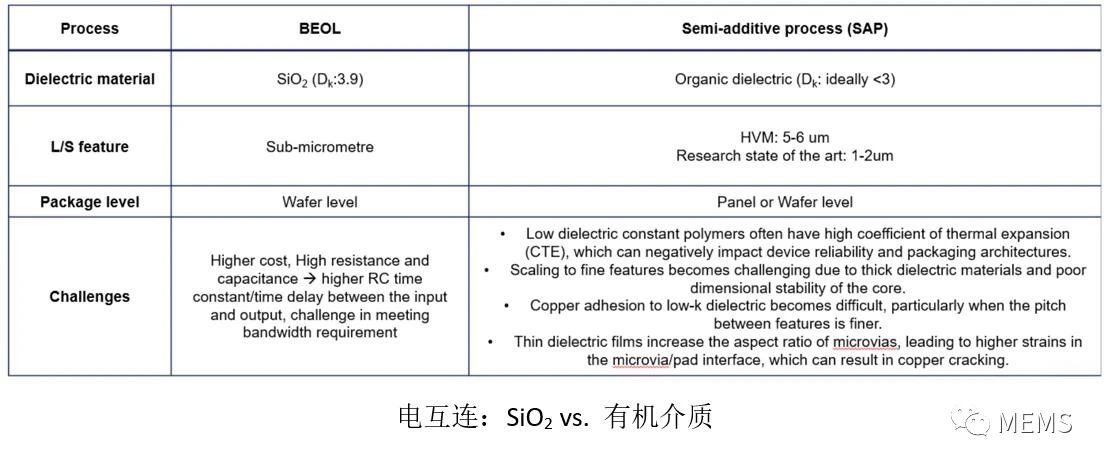

電互連:SiO2 vs. 有機介質

選擇合適的介質材料至關重要,需要考量低介電常數、最佳CTE(盡可能接近Cu的CTE)等特性,以及確保模塊可靠性的有利機械特性(例如楊氏模量和延伸率等)。這些選擇可以實現更高的數據速率,同時保持信號完整性,并有助于更精細的線寬/間距以提高布線密度。

在GPU等高性能加速器中,SiO2等無機介質已被廣泛用于實現超精細線寬/間距。然而,由于它們的高RC延遲,在需要高速連接的應用中受到限制。作為一種替代方案,有機介質因其成本效益,以及通過低介電常數減輕RC延遲而獲得關注。不過,有機介質仍存在挑戰,包括可能對器件可靠性帶來負面影響的高CTE,以及線寬/間距難以擴展等。

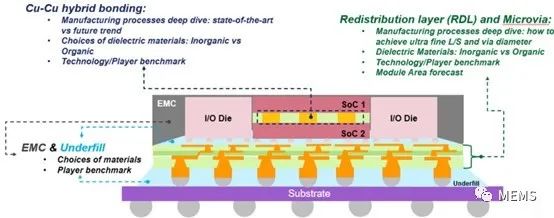

除了選擇合適的材料,封裝制造過程中采用的工藝技術在實現更高數量I/O以及提高I/O比特率方面也發揮著至關重要的作用。2.5D封裝工藝中涉及的步驟(光刻、CMP、蝕刻工藝等),以及3D Cu-Cu混合鍵合中的CMP和鍵合工藝,在實現更緊密布線和增加布線密度等方面提出了挑戰。IDTechEx在這份報告中提供了有關材料選擇如何影響制造工藝的詳細見解,幫助用戶全面了解它們對先進半導體封裝的影響。

本報告覆蓋了哪些材料和技術?

報告研究覆蓋的案例

本報告主要可分為四個部分,提供了理解先進半導體封裝材料和工藝的結構化方法。報告第一部分全面介紹了先進半導體封裝的技術、發展趨勢、關鍵應用和生態系統,為用戶提供了堅實的概述知識。

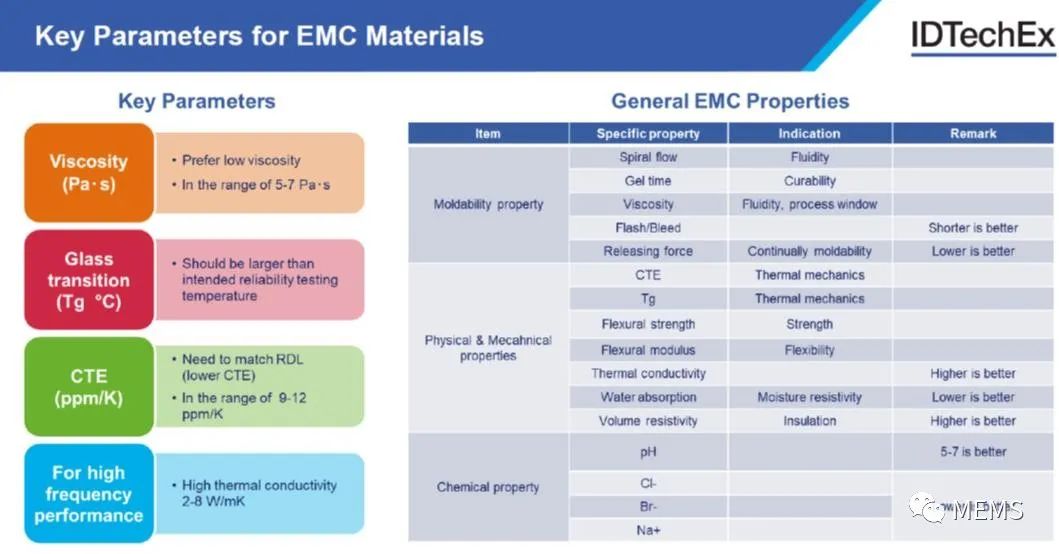

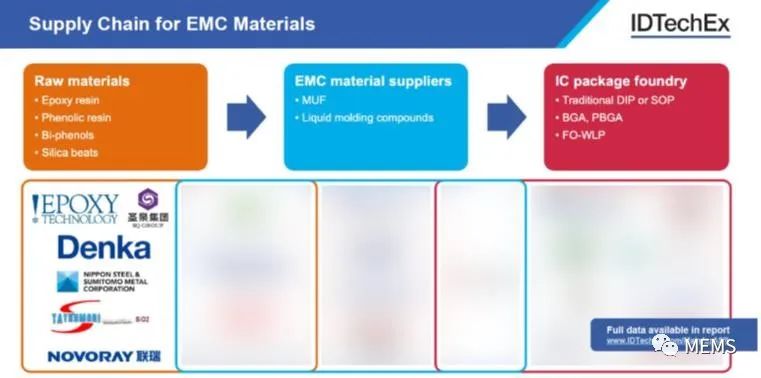

第二部分重點介紹了2.5D封裝工藝,深入研究了RDL和微孔介質材料、RDL制造技術以及EMC和MUF材料選擇等關鍵技術。本部分中的每個小章節都詳細分析了工藝流程、技術對標、廠商評估以及未來趨勢,為用戶提供了全面的見解。

EMC材料關鍵考量參數

EMC材料供應鏈(樣刊模糊化)

關于2.5D封裝的討論繼續到第三部分,重點聚焦了用于3D芯片堆疊的創新Cu-Cu混合鍵合技術。本章節提供了對制造工藝的深入研究,并為實現最佳結果提供了材料選擇指南。報告還展示了很多案例研究,重點介紹了使用有機和無機介質成功實現Cu-Cu混合鍵合的案例。

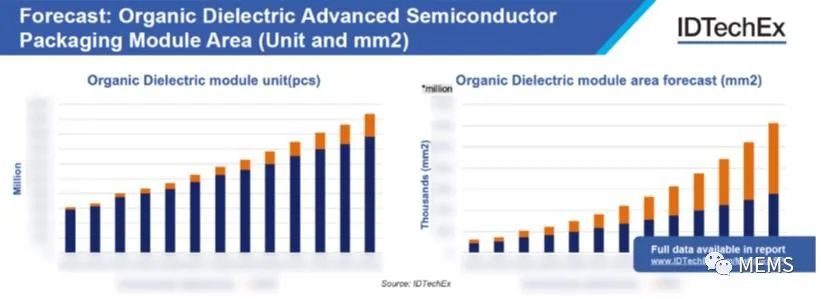

有機介質先進半導體封裝模塊10年期市場預測

此外,本報告在最后一部分提供了有機介質先進半導體封裝模塊的10年期市場預測,對未來預期的市場增長和趨勢提供了重要展望。

-

光刻

+關注

關注

8文章

323瀏覽量

30212 -

半導體封裝

+關注

關注

4文章

270瀏覽量

13793 -

3D芯片

+關注

關注

0文章

52瀏覽量

18442

原文標題:《先進半導體封裝材料及工藝-2023版》

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

半導體工藝講座

適合用于射頻、微波等高頻電路的半導體材料及工藝情況介紹

SiC半導體材料及其器件應用

《先進半導體封裝材料及工藝-2023版》

《先進半導體封裝材料及工藝-2023版》

評論