“去耦”電容并沒有去除來自電源網絡或某個“神秘來源”耦合過來的噪聲,從這個角度講,“去耦”電容的命名存在一定的誤導性。如果電源上存在噪聲,一般情況下是由于負載電路需要從電源網絡汲取較大的電流,而電源傳輸網絡(PDS)的輸出阻抗較高造成的。結果是當負載電流較大時,終端產生了電壓降,從而導致了紋波。而“去耦”電容在電源傳輸網絡中的真正作用是:在保證自身阻抗較小的同時,當負載電路切換狀態需要電流時,為其提供支持。懂了這一點,就會比較容易理解為何每個電源傳輸網絡都需要使用不同容值的多個電容。

電容的類型

通常來說,電容的容值越大,尺寸也越大。在大多數情況下,電容的物理尺寸、封裝類型、材質及安裝方式比容值更重要。所有的電容都有寄生參數,而寄生參數決定了電容在不同頻率下是否有效。

最常見的“去耦”電容包括以下幾種類型:

鋁電解電容

如下圖所示,無論是貼片的還是直插的,只要在PCB上看到的“直直挺立”的電容,基本上都是鋁電解電容。

鋁電解電容的特點是:

- 容值大、體積大、耐高壓、ESR低

- 由于電解液的揮發,使用時間久會導致容值下降

鋁電解電容在高壓應用中(比如48V的DC-DC輸入端)非常常見。但由于尺寸較大的原因,在低壓場景中較少使用。

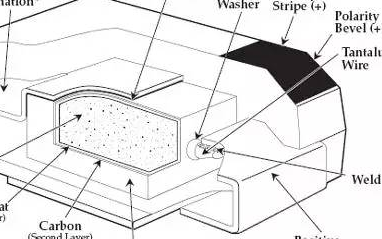

鉭電容是高性能的代名詞,也屬于電解電容的一種,使用金屬鉭做介質,而非電解液,因此很適合在高溫下工作。美系廠家(Kemet, AVX)的鉭電容喜歡用黃色,而日系廠家(SANYO)喜歡用黑色。

鉭電容的特點是:

- 1 uF到1000 uF、中等尺寸(體積小且能達到較高容量)、耐壓低、ESR低

- 價格貴,選擇少,但失效率低

隨著鋁電容的推廣,在很多低端場合,鉭電容有被替代的趨勢。但在高端領域,比如軍工,鉭電容仍是當之無愧的王者。在某些高端的消費電子領域,也可以看到鉭電容的身影。比如下圖中的高端顯卡:

陶瓷電容

陶瓷電容是最小也最便宜的。最近受疫情影響,缺貨嚴重的MLCC(Multi-layer Ceramic Capacitor)就是片式多層陶瓷電容器英文縮寫。

陶瓷電容有各種不同的尺寸、容值和耐壓值。根據電解質材質的不同,陶瓷電容也分很多品類。比如使用X7R做為電解質的陶瓷電容質量較好,它有極高的電壓穩定性及很低的ESR,且溫度范圍比較寬,非常適合濾波、去耦的場合;又如以Y5V做為電解質的陶瓷電容,它的特點是介電常數較高,因此單位容量的電容值較高,從這個角度講應該比較適合“去耦”的應用場合,但其穩定性較差,隨溫度及電壓變化大,因此不是很好的“去耦”選擇。

陶瓷電容的特點是:

- 容值小、尺寸小、ESR低

- 價格最低、可靠性高

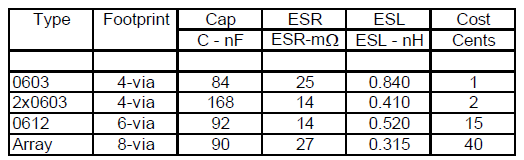

排容是由若干個電容排列而成的電容陣列,應用于對元器件空間要求嚴格的PCB,如手提電腦,PDA,手提電話等,特別適用于輸入,輸出接口電路。從性能上講,排容可以降低電容的ESL。但排容的價格至少10倍于同等容值的陶瓷電容(以0603為例)。如果為了省錢,并聯兩個0603的陶瓷電容同樣可以達到一個排容的ESL。

排容的特點是:

- 節省PCB空間,陣列式的觸點可以使ESL非常低

- 價格貴

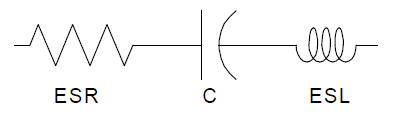

電容等效電路

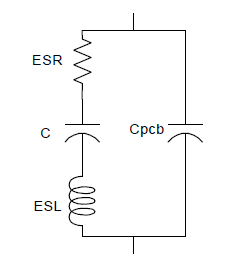

下圖是一個去耦電容的等效電路:

可以看到,任何一個電容都會存在兩個寄生參數,可以等效為一個串聯電阻ESR(Equivalent Series Resistance)以及一個串聯電感ESL(Equivalent Series Inductor)。

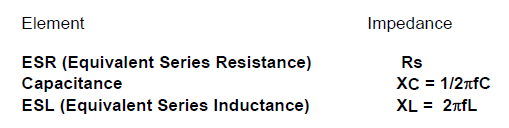

ESR、電容、ESL的阻抗如下:

因此,去耦電容的有效阻抗計算公式為:

串聯諧振

由上述公式可得,當達到串聯諧振頻率f,使得XL=Xc時,電容的阻抗最小,即ESR的阻值。當頻率高于諧振頻率時,電容呈現出電感的特性。

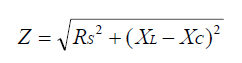

下圖是一個1 uF的0603陶瓷電容的頻率-阻抗曲線:

串聯諧振頻率在3.5 MHz。超過3.5 MHz后,電容的阻抗取決于ESL。

并聯諧振

如果PCB使用了電源平面對,則還需要考慮平面電容與PCB表面所有其他電容互相作用而在某個頻率產生的阻抗尖峰(Impedance Hole),該頻率會大于串聯諧振頻率(因為平面電容通常大于PCB上的電容),我們稱其為并聯諧振頻率。

下圖是PCB板上的電容等效模型:

在高頻的時候,電容“C”相當于短路。并聯諧振頻率發生在XL(陶瓷電容的ESL)及XC-PCB(平面電容阻抗)相等的時候。

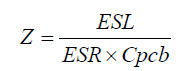

在并聯諧振頻率處,電路的阻抗幅度與陶瓷電容的ESR成反比:

如果ESR非常小,則阻抗會變得非常大。典型的問題出現在幾百MHz的時候,如果并聯諧振頻率正好等于時鐘或者某個信號的諧波頻率,則阻抗會變得很大。

因此,在選擇電容時,必須要考慮ESR在一個合理的區間內:ESR要足夠小以保證低頻時的頻率特性,但同時需要足夠大以抑制并聯諧振頻率時的阻抗尖峰。

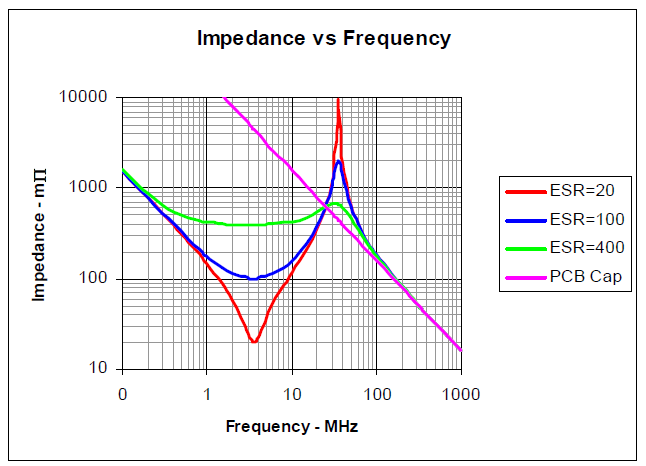

下圖為1 uF的0603陶瓷電容及PCB平面電容為10 nF時的頻率-阻抗曲線:

圖中展示了不同ESR陶瓷電容在串聯諧振頻率及并聯諧振下的阻抗。粉紅色的曲線為PCB平面電容。可以看到并聯諧振時的阻抗總是高于PCB平面電容阻抗本身。當ESR為20毫歐時,在并聯諧振頻率35.6 MHz處,阻抗尖峰達到了9.5歐姆。

去耦電容特性測量

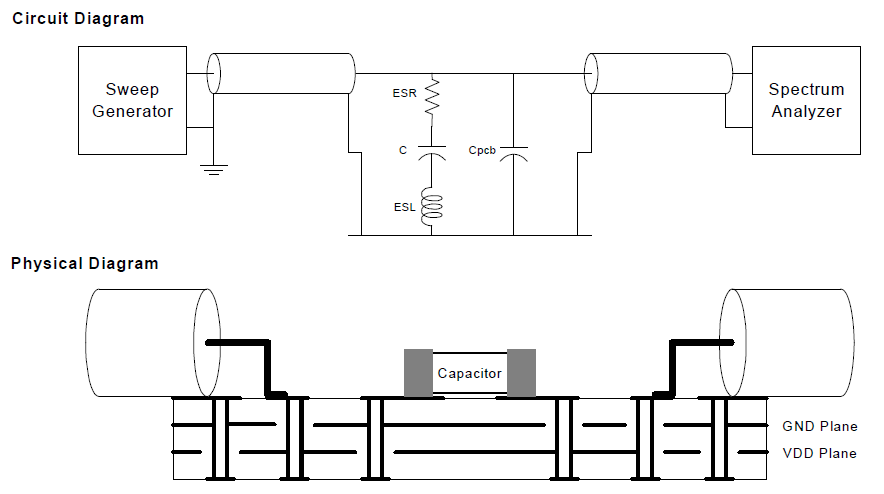

下圖為測量“去耦”電容特性的參考電路及實際測試的情況:

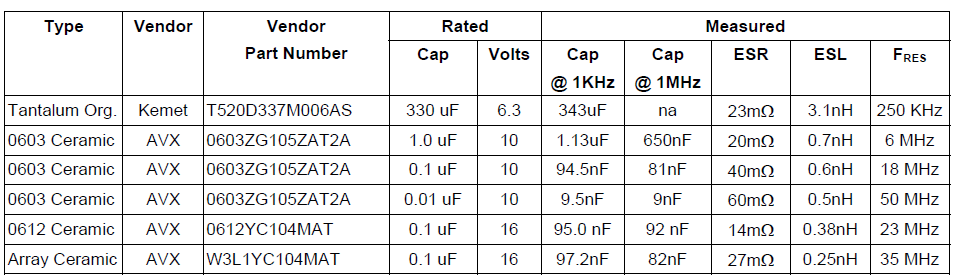

下圖為常用去耦電容的特性:

最后一列Fres為電容的串聯諧振頻率,超過這一頻率,電容就會表現為感性,其阻抗就會迅速變大。以上數據來源于電源平面與裝配去耦電容層非常接近的情況,電容的焊盤到電源平面的過孔長度只有11 mils。

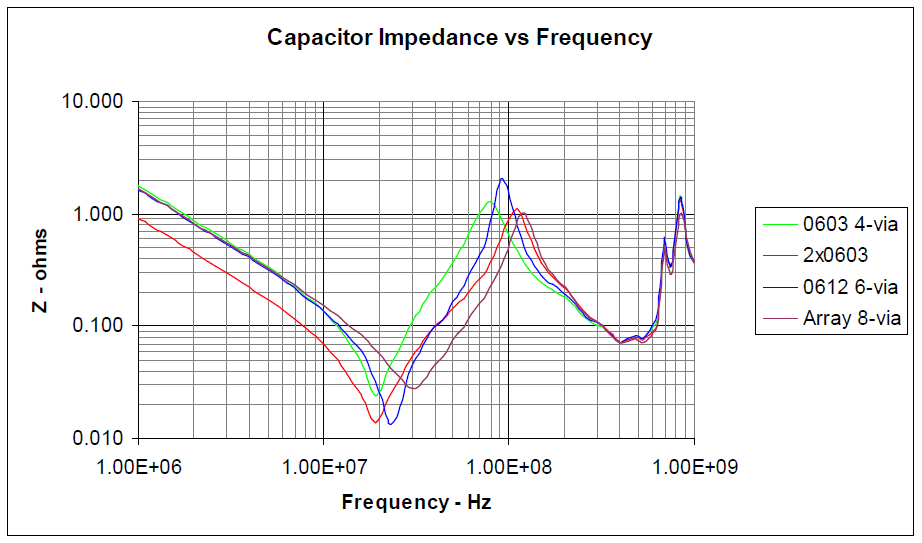

下圖是不同3種不同類型電容的頻率響應曲線:

所有電容的容值都為0.1 uF,由于測試板的電容焊盤到電源平面的過孔長度略大(30 mils),因此測出的ESL與上表相比略大:

平面電容

從上面的表格中可以看到,即使使用了容值僅為0.01 uF的電容,其串聯諧振頻率也僅能達到50 MHz。如果頻率更高,就無法為負載提供低阻抗的路徑了。這時,就必須使用電源平面對。關于電源平面對,在上一章節已經介紹過,這里不再贅述。再強調一下結論:

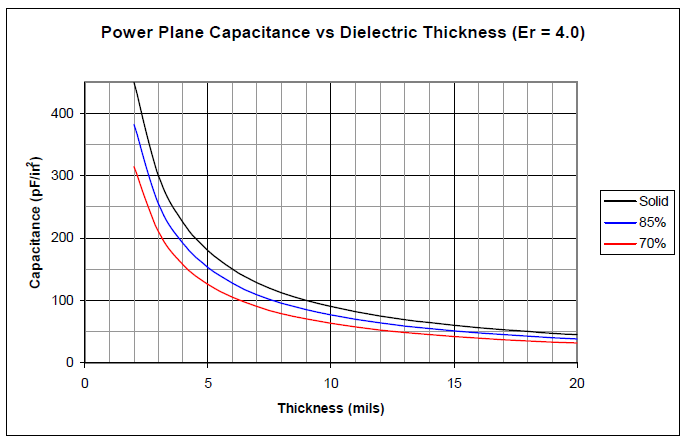

當VDD與GND的電解質厚度為3 mils時,電源平面電容為每平方英寸300 pF。如果考慮到AntiPad或者過孔到平面的間距,有效容值約為85%左右;對于BGA器件,由于存在較多的過孔,其有效容值只能達到70%左右。

去耦電容的擺放

開始這個話題前,先明確一個概念:電源平面對的ESL遠小于普通電容(篇幅原因,不再詳細分析原因)。

所有人都告訴我們,去耦電容應盡可能接近芯片的電源和地。這個結論是不是絕對的呢?

其實更正確的說法應當是:如果不存在電源平面(對),去耦電容應盡可能接近芯片的電源和地。如果存在合理設計的電源平面(即存在平面電容),去耦電容擺放的位置并不會造成太大的影響,考慮如何更方便地進行走線或者裝配,比電容的位置更重要。

下圖是一個電容測試板,有8個平面、6個信號層及2個外層。使用配合測量的電源/地平面容值為15.77 nF。測試板的左側是兩根焊在PCB上的同軸電纜引線,用于測量。

由于電源平面對的感抗很低,電容的擺放位置并沒有那么重要,此時更應該考慮的是過孔的長度(表面到地平面)以及電源平面到IC的距離。

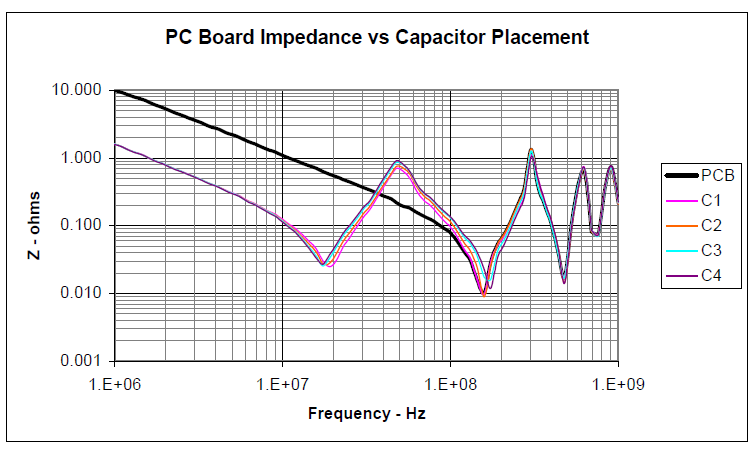

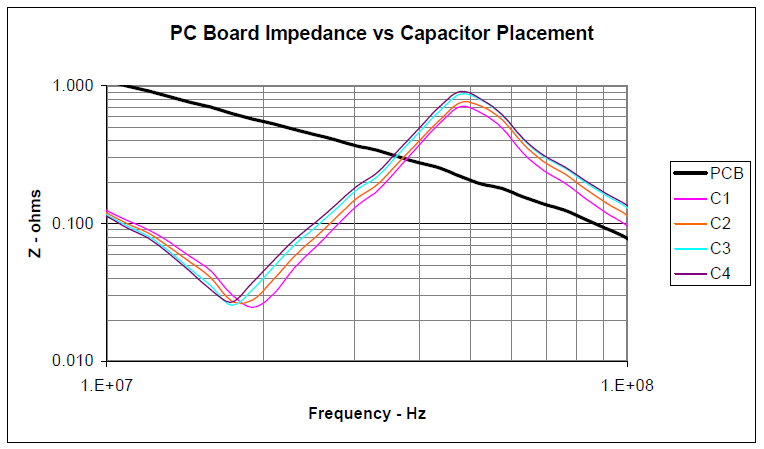

為了驗證電容在不同位置的效果,我們沿著板長的方向,每隔2.5''擺放一個0.1 uF的0603電容,下圖是實際測出的在不同位置擺放電容時阻抗-頻率曲線:

放大細節:

可以看到,電容不同的位置只是使串聯諧振頻率偏移了8%左右;而并聯諧振頻率幾乎沒有差異。可見,在電源平面/地平面設計良好的情況下,去耦電容擺放的位置并沒有太大的影響。

-

ESR

+關注

關注

4文章

202瀏覽量

31141 -

去耦電容

+關注

關注

11文章

316瀏覽量

22392 -

鋁電解電容

+關注

關注

1文章

81瀏覽量

13402 -

GND

+關注

關注

2文章

539瀏覽量

38754

發布評論請先 登錄

相關推薦

什么是電容?真正的電容究竟是什么?

“去耦”電容其作用究竟是什么?

“去耦”電容其作用究竟是什么?

評論