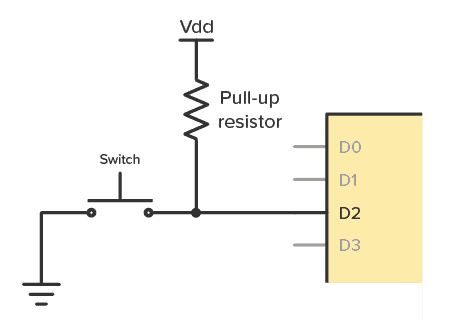

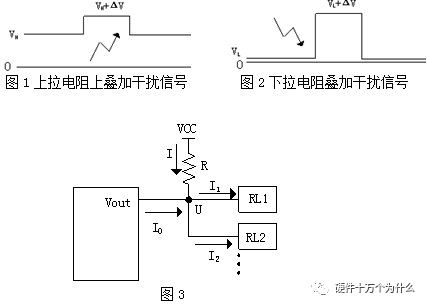

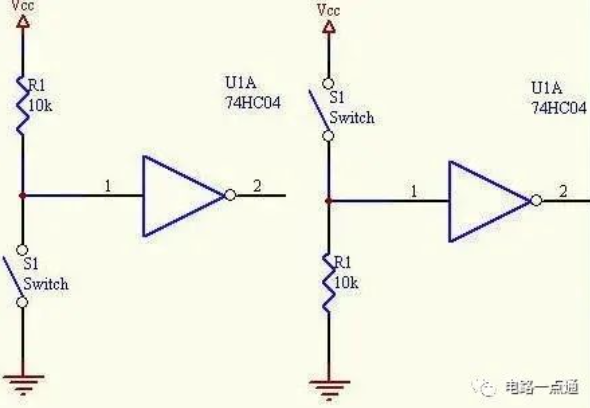

在構建電路時,常會使用到上拉電阻,我們經常在一些數字電路中看到它。它只是一個電阻,從輸入端連接到電路的正電源VDD。如下圖所示:

上拉電阻用于確保在未按下按鈕時輸入引腳處于高電平狀態。如果沒有這顆電阻,那么輸入電壓將是浮動的,并且會伴隨著輸入在HIGH和LOW之間隨機變化的風險,此外它會產生噪聲。

一、如何選擇上拉電阻值?

規則一:值不能太高。

上拉值越高,輸入電壓越低。重要的是要讓電壓足夠高,使芯片將其視為HIGH或邏輯1輸入。例如,如果使用帶有10V電源的CD4017,則輸入端至少需要7V才能將其視為高電平。

規則二:也不能太小。

例如,如果選擇100Ω,問題是按下按鈕時會有大量電流流過它。例如,使用9V電源,接上100Ω的電阻,那么電流為90mA。這是不必要的功耗浪費,這也意味著電阻器需要承受0.81W的功率。值得注意的是,大多數電阻器只能承載高達0.25W的功率。

二、得出的結論

選擇上拉電阻時的經驗法則是選擇至少比引腳輸入阻抗(或內阻)小10倍的電阻值。通常,一個10kΩ的上拉值就可以解決問題。

三、上拉電阻如何工作?

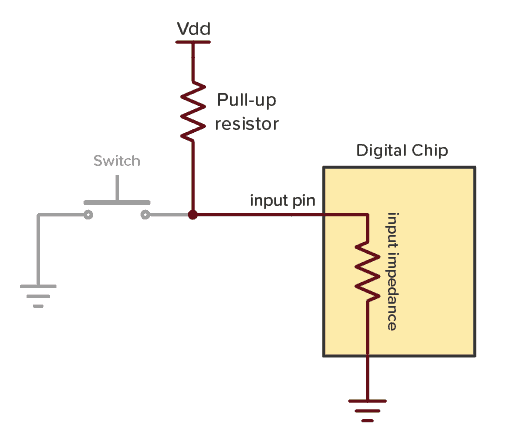

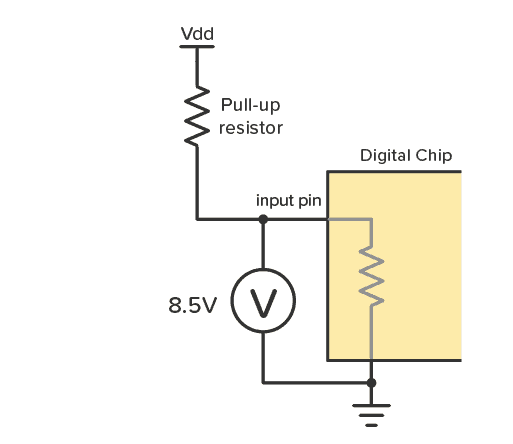

我們可以將集成電路 (IC) 的輸入引腳視為具有接地的電阻器。這稱為輸入阻抗:

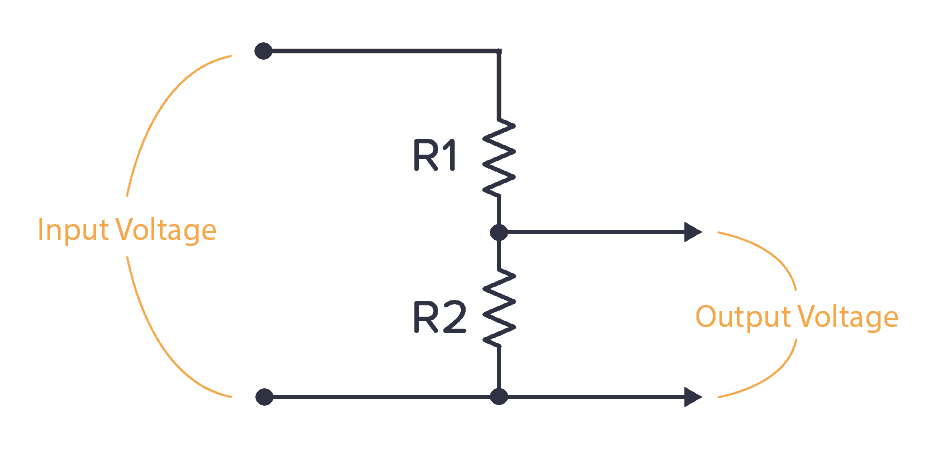

這兩個電阻組成了一個分壓器。如果查看標準分壓器電路,可以看到上拉電阻為R1,輸入阻抗為R2:

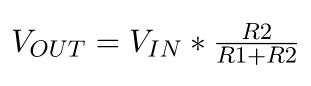

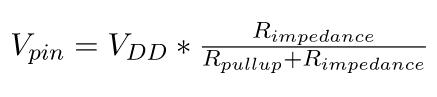

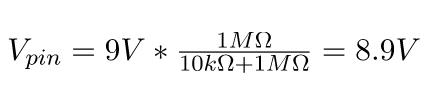

我們可以使用分壓器公式找到未按下按鈕時輸入引腳上的電壓:

下面重命名了公式的組成部分以適應上拉示例。輸入電壓為上拉示例中的VDD 。輸出電壓是輸入引腳上的電壓。于是公式就變成了:

示例計算

假設您的芯片的輸入阻抗為1MΩ(對于許多芯片來說,100kΩ到1MΩ是正常的)。如果您的電源是9V,并且您選擇了一個10kΩ

的上拉電阻,那么輸入引腳上的電壓是多少?

輸入引腳上的電壓為 8.9V,足以充當高電平輸入。

一般來說,如果堅持使用不超過輸入阻抗十倍的上拉電阻器的經驗法則,將確保必須具有至少90%的VDD電壓輸入引腳。

如何找到IC的輸入阻抗?

我們可以很容易地測量出芯片的輸入阻抗。阻抗實際上是電阻的一個術語,它可以根據頻率而變化。但是對于這種上拉情況,我們只處理直流電流。

將例如10kΩ的上拉電阻連接到芯片的輸入端,并測量輸入端的電壓。

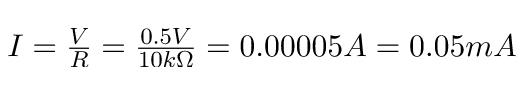

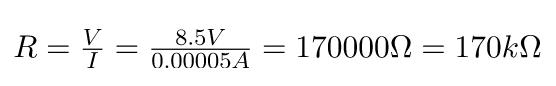

假設你測量時得到8.5V。那么,通過歐姆定律就能計算流過電阻器的電流。電阻兩端的電壓降為9V–8.5V=0.5V,因此將得到:

有0.05mA電流流過電阻器,因此也通過輸入引腳下降到地。再次,使用歐姆定律找出電壓降為8.5V和電流為0.05mA的物體的電阻:

輸入阻抗為170kΩ。這意味著該輸入的上拉電阻不應超過17kΩ。

-

上拉電阻

+關注

關注

5文章

360瀏覽量

30624 -

阻抗

+關注

關注

17文章

958瀏覽量

45976

發布評論請先 登錄

相關推薦

上拉電阻如何工作?如何選擇上拉電阻值?

上拉電阻如何工作?如何選擇上拉電阻值?

評論