隨著深度學習、高性能計算、NLP、AIGC、GLM、AGI的快速發展,大模型得到快速發展。2023年科創圈的頂尖技術無疑是大模型,據科技部新一代人工智能發展研究中心發布的《中國人工智能大模型地圖研究報告》顯示,我國已發布79個參數規模超過10億的大模型,幾乎形成了百模大戰的局面。在大模型研發方面,中國14個省區市都在積極開展工作,其中北京擁有38個項目,廣東擁有20個項目。

目前,自然語言處理是大模型研發最活躍的領域,其次是多模態領域,而在計算機視覺和智能語音等領域大模型相對較少。大學、科研機構和企業等不同創新主體都參與了大模型的研發,但學術界和產業界之間的合作研發仍有待加強。

隨著人工智能大模型參數量從億級增長到萬億級,人們對支撐大模型訓練所需的超大規模算力和網絡連接的重要性越來越關注。大模型的訓練任務需要龐大的GPU服務器集群提供計算能力,并通過網絡進行海量數據交換。然而,即使單個GPU性能強大,如果網絡性能跟不上,整個算力集群的計算能力也會大幅下降。因此,大集群并不意味著大算力,相反,GPU集群越大,額外的通信損耗也越多。本文將詳細介紹CPU和GPU的復雜性比較,多元算力的結合(CPU+GPU),算存互連和算力互連的重要性。

多元算力:CPU+GPU

ChatGPT廣受歡迎使得智算中心的關注度再次上升,GPU同時也成為各大公司爭相爭奪的對象。GPU不僅是智算中心的核心,也在超算領域得到廣泛的應用。根據最新一屆TOP500榜單(于2023年5月下旬公布)顯示:

使用加速器或協處理器的系統從上一屆的179個增加到185個,其中150個系統采用英偉達(NVIDIA)的Volta(如V100)或Ampere(如A100)GPU。

在榜單的前10名中,有7個系統使用GPU,在前5名中,只有第二名沒有使用GPU。

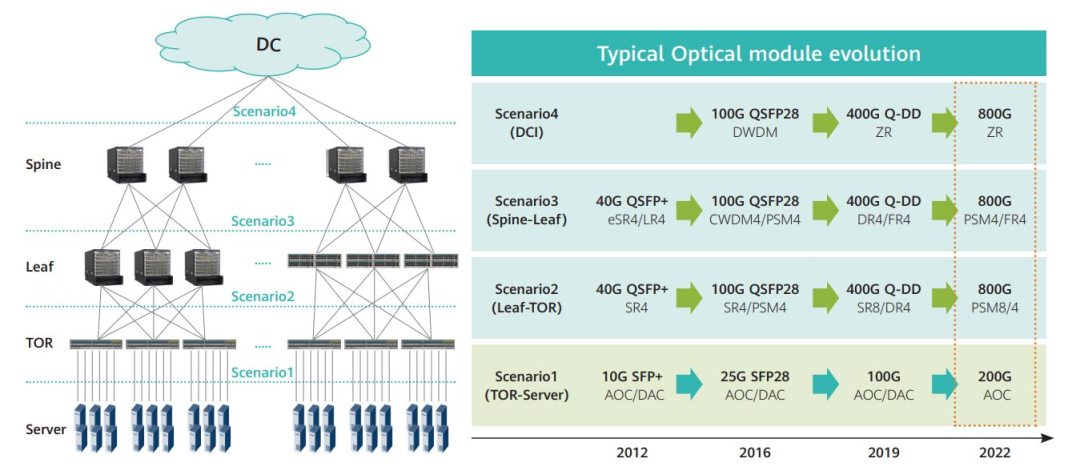

超大規模數據中心架構及光模塊升級路徑

當然,CPU仍然是不可或缺的。以榜單前10名為例,AMC EPYC家族處理器占據4個位置,英特爾至強家族處理器和IBM的POWER9各占據2個位置,而Arm也有1個位置(富士通A64FX)位居第二位。

通用算力和智能算力相輔相成,可以滿足多樣化的計算需求。以歐洲高性能計算聯合事業(EuroHPC JU)正在部署的MareNostrum 5為例:基于第四代英特爾至強可擴展處理器的通用算力計劃將于2023年6月開放服務,而基于NVIDIA Grace CPU的"下一代"通用算力以及由第四代英特爾至強可擴展處理器和NVIDIA Hopper GPU(如H100)組成的加速算力,則計劃于2023年下半年投入使用。

一、GPU:大芯片與小芯片

盡管英偉達在GPU市場上占據著統治地位,但AMD和英特爾并未放棄競爭。以最新的TOP500榜單前10名為例,其中4個基于AMC EPYC家族處理器的系統中,有2個搭配AMD Instinct MI250X和NVIDIA A100,前者排名較高,分別位居第一和第三位。

然而,在人工智能應用方面,英偉達GPU的優勢顯著。在GTC 2022上發布的NVIDIA H100 Tensor Core GPU進一步鞏固其領先地位。H100 GPU基于英偉達Hopper架構,采用臺積電(TSMC)N4制程,擁有高達800億個晶體管,并在計算、存儲和連接方面全面提升:

132個SM(流式多處理器)和第四代Tensor Core使性能翻倍;

比前一代更大的50MB L2緩存和升級到HBM3的顯存構成新的內存子系統;

第四代NVLink總帶寬達到900GB/s,支持NVLink網絡,PCIe也升級到5.0。

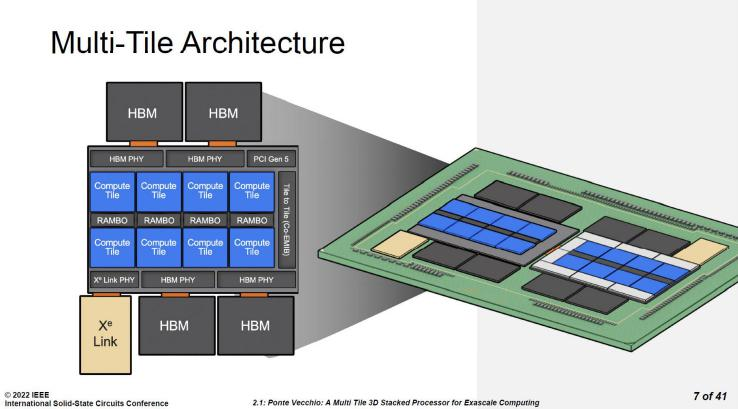

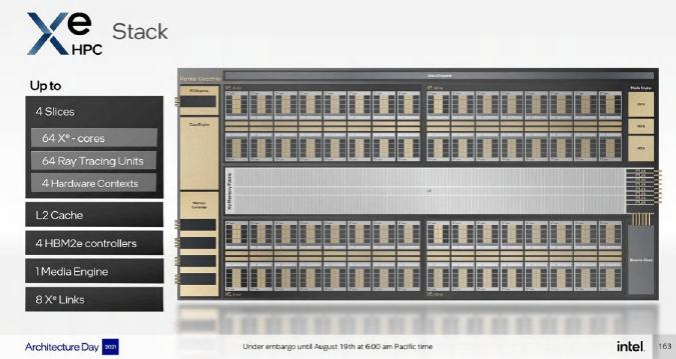

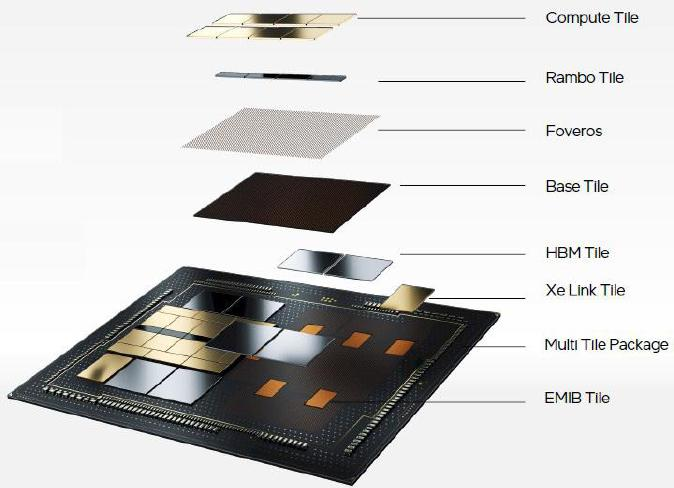

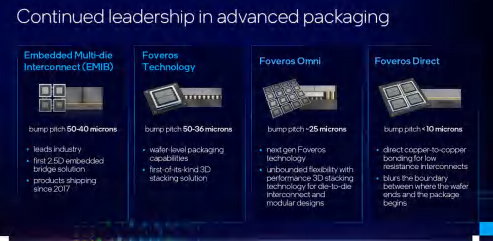

在2023年1月,英特爾也推出代號為Ponte Vecchio的英特爾數據中心GPU Max系列,與第四代英特爾至強可擴展處理器和英特爾至強CPU Max系列一起發布。英特爾數據中心GPU Max系列利用英特爾的Foveros和EMIB技術,在單個產品上整合47個小芯片,集成超過1000億個晶體管,擁有高達408MB的L2緩存和128GB的HBM2e顯存,充分體現芯片模塊化的理念。

可插拔光模塊與 CPO 對比

二、CPU:性能核與能效核

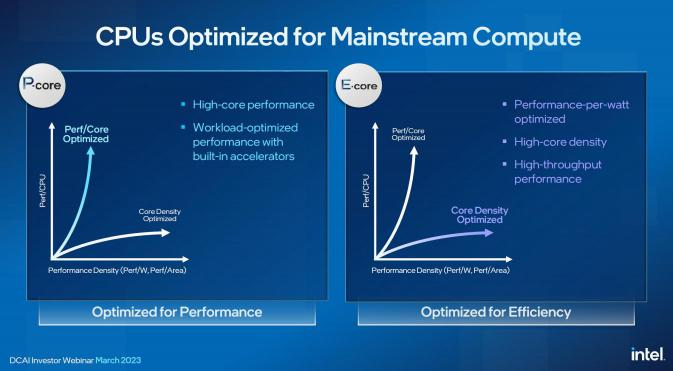

通用算力的發展趨勢是多元化的,以滿足不同應用場景的需求。在手機、PC和其他終端產品中,經過驗證的"大小核"架構逐漸成為主流,而在服務器CPU市場也開始流行起來。然而,服務器的特點是集群作戰,并不迫切需要在同一款CPU內部實現大小核的組合。主流廠商正通過提供全是大核或全是小核的CPU來滿足不同客戶的需求,其中大核注重單核性能,適合縱向擴展,而小核注重核數密度,適合橫向擴展。

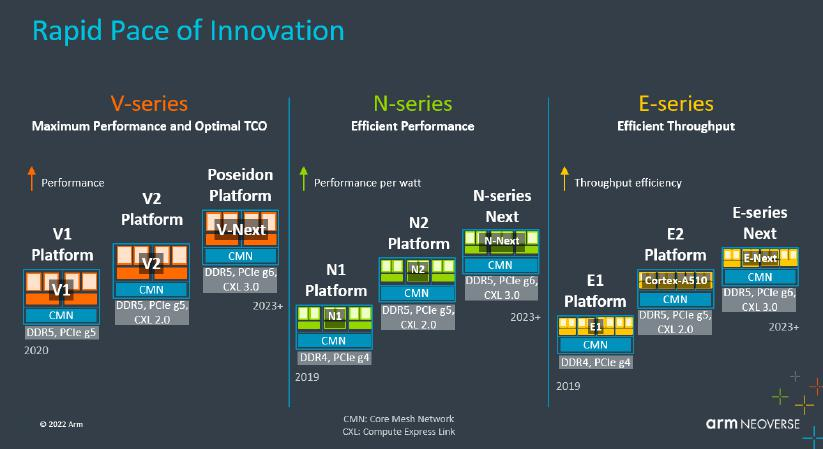

作為big.LITTLE技術的發明者,Arm將異構核的理念引入服務器CPU市場,并已經有一段時間。Arm的Neoverse平臺分為三個系列:

Neoverse V系列用于構建高性能CPU,提供高每核心性能,適用于高性能計算、人工智能機器學習加速等工作負載;

Neoverse N系列注重橫向擴展性能,提供經過優化的平衡CPU設計,以提供理想的每瓦性能,適用于橫向擴展云、企業網絡、智能網卡DPU、定制ASIC加速器、5G基礎設施以及電源和空間受限的邊緣場景;

Neoverse E系列旨在以最小的功耗支持高數據吞吐量,面向網絡數據平面處理器、低功耗網關的5G部署。

這些系列的設計旨在滿足不同領域和應用的需求。

在規模較大的云計算中心、智算中心和超級計算中心等應用場景中,可以將大小核架構在數據中心市場上的實踐歸納為兩個系列:V系列側重單核性能的縱向擴展(Scale-up)而N系列側重多核性能的橫向擴展(Scale-out)。

在這些應用場景中,V系列產品的代表包括64核的AWS Graviton3(猜測為V1)和72核的NVIDIA Grace CPU(V2)而N系列產品除阿里云的128核倚天710(猜測為N2)外,還在DPU領域得到廣泛應用。最近發布的AmpereOne采用Ampere Computing公司自研的A1核,最多擁有192個核心,更接近Neoverse N系列的設計風格。英特爾在面向投資者的會議上也公布類似的規劃。

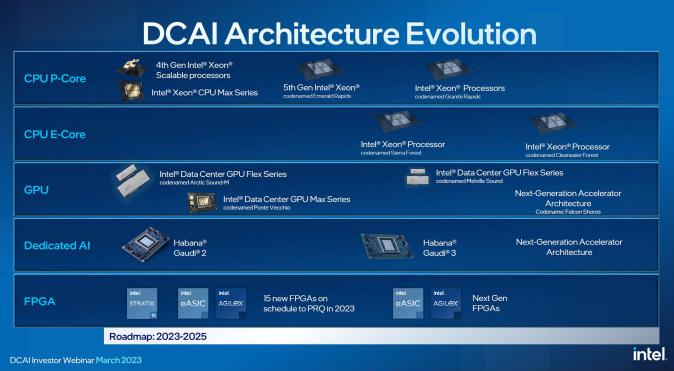

英特爾在面向投資者的會議上也公布類似的規劃:

2023年第四季度推出第五代英特爾至強可擴展處理器(代號Emerald Rapids)

2024年推出的代號為Granite Rapids的下一代產品。這些處理器將延續目前的性能核(P-Core)路線。另外,2024年上半年推出的代號為Sierra Forest的CPU將是第一代能效核(E-Core)至強處理器,擁有144個核心。

第五代英特爾至強可擴展處理器與第四代共享平臺易于遷移而Granite Rapids和Sierra Forest將采用英特爾的3納米制程。P-Core和E-Core的組合已經在英特爾的客戶端CPU上得到驗證,兩者之間的一個重要區別是否支持超線程。E-Core每個核心只有一個線程注重能效,適用于追求更高物理核密度的云原生應用。

AMD 的策略大同小異。

2022年11月發布代號為Genoa的第四代EPYC處理器,采用5納米的Zen 4核心,最高可達96個核心。

2023年中,AMD還將推出代號為Bergamo的“云原生”處理器,據傳擁有多達128個核心,通過縮小核心和緩存來提供更高的核心密度。

雖然性能核和能效核這兩條路線之間存在著核心數量的差異,但增加核心數是共識。隨著CPU核心數量的持續增長,對內存帶寬的要求也越來越高,僅僅升級到DDR5內存是不夠的。AMD的第四代EPYC處理器(Genoa)已將每個CPU的DDR通道數量從8條擴展到12條,Ampere Computing也有類似的規劃。

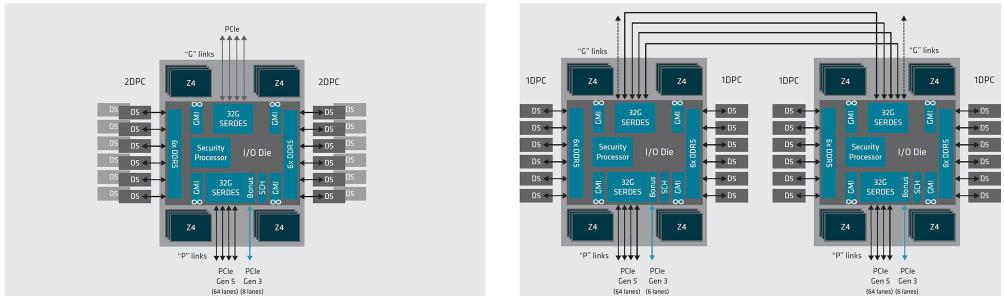

然而,擁有超過100個核心的CPU已經超出了一些企業用戶的實際需求,而每個CPU的12條內存通道在雙路配置下也給服務器主板設計帶來新的挑戰。在多種因素的影響下,單路服務器在數據中心市場的份額是否會有顯著增長,這仍然需要拭目以待。

AMD 第四代 EPYC 處理器擁有 12 個 DDR5 內存通道,但單路(2DPC)和雙路(1DPC)配置都不超 過 24 個內存槽,比 8 內存通道 CPU 的雙路配置(32 個內存槽)還要少。換言之,單 CPU 的內存通 道數增加了,雙路配置的內存槽數反而減少

三、GPU和CPU芯片相比誰更復雜

在大規模并行計算方面,高端GPU(如NVIDIA的A100或AMD的Radeon Instinct MI100)和高端CPU(如Intel的Xeon系列或AMD的EPYC系列)都具有各自的復雜性。GPU擁有大量的CUDA核心或流處理器,專注于并行計算,以支持高性能的并行任務。而高端CPU則具有更多的核心、更高的頻率和復雜的超線程技術,以提供強大的通用計算能力。我們從應用場景、晶體管數量、架構設計幾個維度來看看。

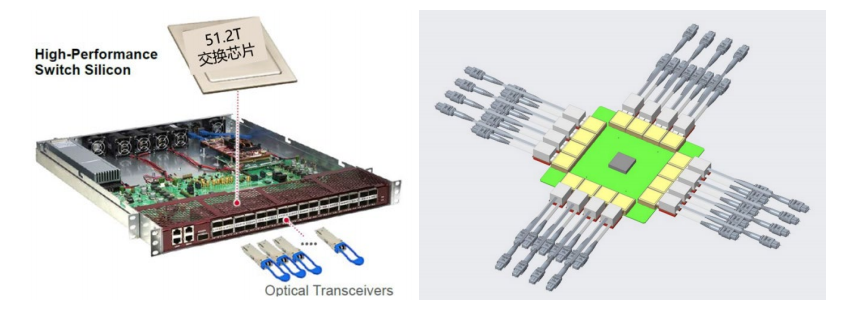

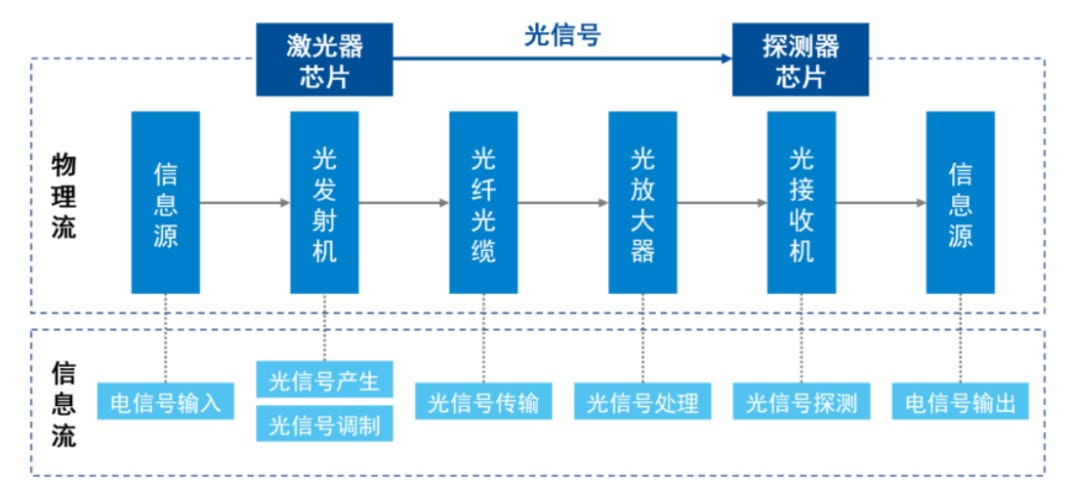

光芯片是光通信系統中的核心元件

1、應用場景

GPU擁有大量的計算核心、專用存儲器和高速數據傳輸通道,其設計注重于滿足圖形渲染和計算密集型應用的需求,強調大規模并行計算、內存訪問和圖形數據流處理。GPU的核心理念是并行處理,通過擁有更多的處理單元,能夠同時執行大量并行任務。這使得GPU在處理可并行化的工作負載(如圖形渲染、科學計算和深度學習)時表現出色。相比之下,CPU專注于通用計算和廣泛的應用領域,通常具有多個處理核心、高速緩存層次和復雜的指令集體系結構。

2、晶體管數量

頂級的GPU通常擁有更多的晶體管,這是因為它們需要大量的并行處理單元來支持高性能計算。舉例來說,NVIDIA的A100 GPU擁有約540億個晶體管,而AMD的EPYC 7742 CPU則包含約390億個晶體管。晶體管數量的差異反映了GPU在并行計算方面的重要性和專注度。

3、架構設計

從架構和設計的角度來看,CPU通常被認為更復雜。CPU需要處理各種不同類型的任務,并且需要優化以盡可能快地執行這些任務。為了實現這一目標,CPU采用了許多復雜的技術,如流水線、亂序執行、分支預測和超線程等。這些技術旨在提高CPU的性能和效率。

相比之下,頂級的GPU可能在硬件規模(如晶體管數量)上更大,但在架構和設計上可能相對簡化。GPU的設計注重于大規模并行計算和圖形數據流處理,因此其架構更加專注和優化于這些特定的任務。

1)GPU架構

GPU具有一些關鍵的架構特性。

首先,它擁有大量的并行處理單元(核心),每個處理單元可以同時執行指令。如NVIDIA的Turing架構具有數千個并行處理單元,也稱為CUDA核心。其次,GPU采用分層的內存架構,包括全局內存、共享內存、本地內存和常量內存等。這些內存類型用于緩存數據,以減少對全局內存的訪問延遲。另外,GPU利用硬件進行線程調度和執行,保持高效率。在NVIDIA的GPU中,線程以warp(32個線程)的形式進行調度和執行。此外,還擁有一些特殊的功能單元,如紋理單元和光柵化單元,這些單元專為圖形渲染而設計。最新的GPU還具有為深度學習和人工智能設計的特殊單元,如張量核心和RT核心。此外,GPU采用了流多處理器和SIMD(單指令多數據流)架構,使得一條指令可以在多個數據上并行執行。

具體的GPU架構設計因制造商和產品線而異,例如NVIDIA的Turing和Ampere架構與AMD的RDNA架構存在一些關鍵差異。然而,所有的GPU架構都遵循并行處理的基本理念。

2)CPU架構

CPU(中央處理單元)的架構設計涉及多個領域,包括硬件設計、微體系結構和指令集設計等。

指令集架構(ISA)是CPU的基礎,它定義了CPU可以執行的操作以及如何編碼這些操作。常見的ISA包括x86(Intel和AMD)、ARM和RISC-V。現代CPU采用流水線技術,將指令分解為多個階段,以提高指令的吞吐量。CPU還包含緩存和內存層次結構,以減少訪問內存的延遲。亂序執行和寄存器重命名是現代CPU的關鍵優化手段,可以提高指令的并行執行能力和解決數據冒險問題。分支預測是一種優化技術,用于預測條件跳轉指令的結果,以避免因等待跳轉結果而產生的停頓。現代CPU通常具有多個處理核心,每個核心可以獨立執行指令,并且一些CPU還支持多線程技術,可以提高核心的利用率。

CPU架構設計是一個極其復雜的過程,需要考慮性能、能耗、面積、成本和可靠性等多個因素。

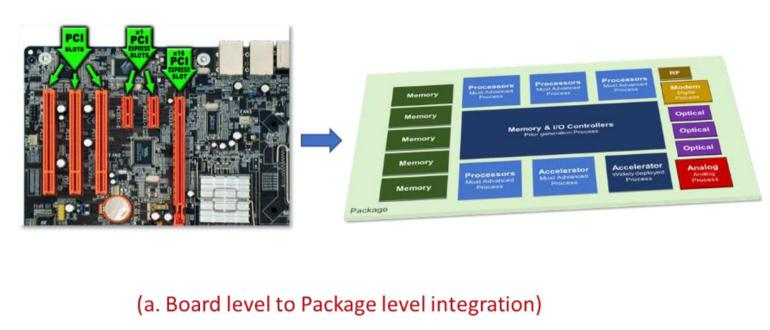

四、Chiplet 與芯片布局

在CPU的Chiplet實現上,AMD和英特爾有一些不同。從代號為羅馬(Rome)的第二代EPYC開始,AMD將DDR內存控制器、Infinity Fabric和PCIe控制器等I/O器件從CCD中分離出來,集中到一個獨立的芯片(IOD)中,充當交換機的角色。這部分芯片仍然采用成熟的14納米制程,而CCD內部的8個核心和L3緩存的占比從56%提高到86%,從7納米制程中獲得更大的收益。通過分離制造IOD和CCD,并按需組合,帶來了許多優點:

1、獨立優化

根據I/O、運算和存儲(SRAM)的不同需求,選擇適合成本的制程。例如,代號為Genoa的第四代EPYC處理器將使用5納米制程的CCD搭配6納米制程的IOD。

2、高度靈活

一個IOD可以搭配不同數量的CCD,以提供不同核心數的CPU。例如,代號為羅馬的第二代EPYC處理器最多支持8個CCD,但也可以減少到6個、4個或2個,因此可以輕松提供8至64個核心。將CCD視為8核CPU,IOD視為原來服務器中的北橋或MCH(內存控制器中心),第二代EPYC相當于一套微型化的八路服務器。采用這種方法構建64核的CPU比在單個芯片上提供64核要簡化許多,并具有良率和靈活性的優勢。

3、擴大規模更容易

通過增加CCD的數量,在IOD的支持下,可以輕松獲得更多的CPU核心。例如,第四代EPYC處理器通過使用12個CCD將核心數量擴展到96個。這種Chiplet實現方式為AMD帶來許多優勢,并且在制程選擇、靈活性和擴展性方面更具有競爭力。

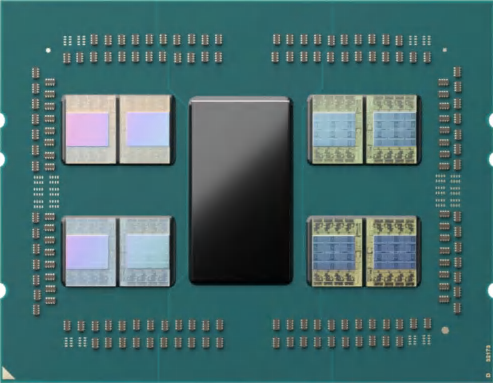

AMD 第四代 EPYC 處理器,12 顆 CCD 環繞 1 顆 IOD

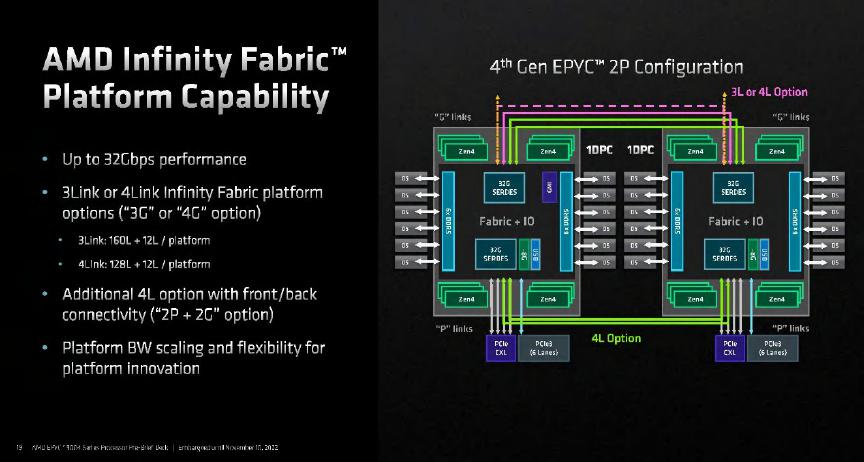

第二至四代EPYC處理器采用星形拓撲結構,以IOD為中心連接多個較小規模的CCD。這種架構的優勢在于可以靈活增加PCIe和內存控制器的數量,降低成本。然而,劣勢在于任意核心與其他資源的距離較遠,可能會限制帶寬和增加時延。

在過去,AMD憑借制程優勢和較高的核數,使得EPYC處理器在多核性能上表現出色。然而,隨著競爭對手如英特爾和Arm的制造工藝改進以及大核心性能提升,AMD的核數優勢可能會減弱,多核性能優勢難以持續。同時,其他廠商的多核CPU采用網格化布局,通過快速互聯來減小核心與其他資源的訪問距離,更有效地控制時延。

五、Arm 新升:NVIDIA Grace 與 AmpereOne

Arm一直希望在服務器市場上占有一席之地。亞馬遜、高通、華為等企業都推出基于Arm指令集的服務器CPU。隨著亞馬遜的Graviton、Ampere Altra等產品在市場上站穩腳跟,Arm在服務器CPU市場上的地位逐漸增強。同時,隨著異構計算的興起,Arm在高性能計算和AI/ML算力基礎設施中的影響力也在擴大。

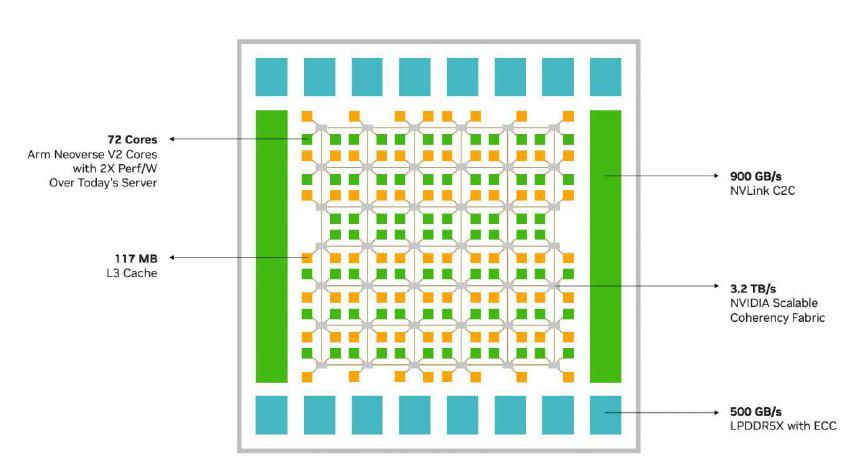

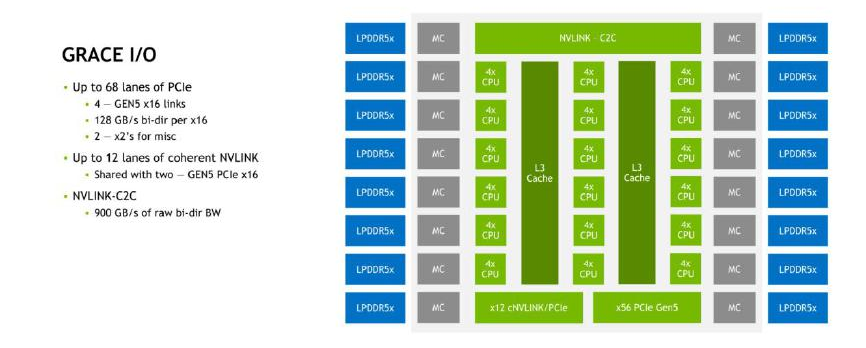

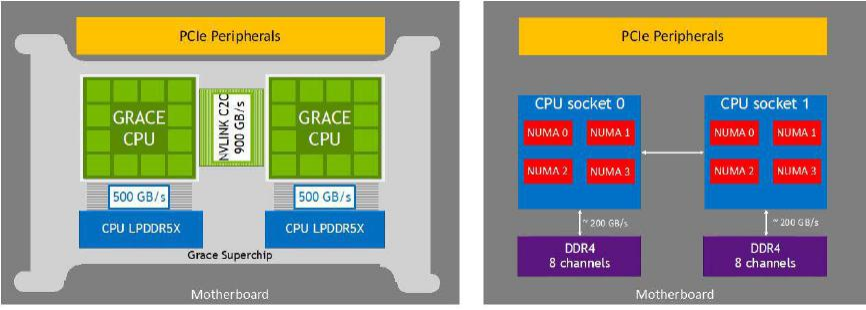

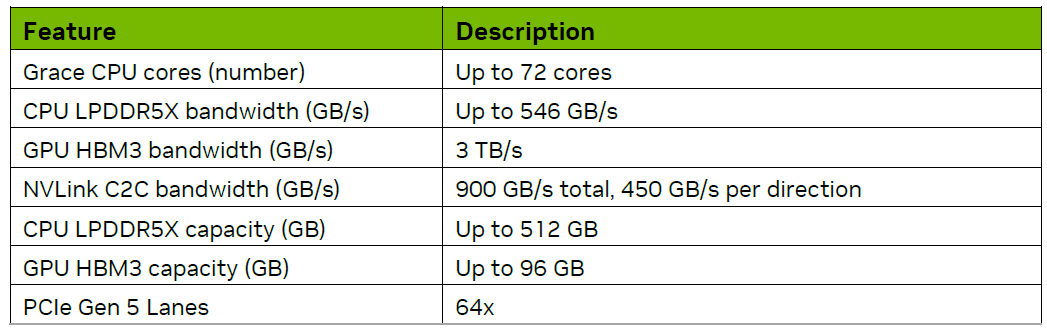

英偉達推出的基于Arm Neoverse架構的數據中心專用CPU即NVIDIA Grace,具有72個核心。Grace CPU超級芯片由兩個Grace芯片組成,通過NVLink-C2C連接在一起,在單插座內提供144個核心和1TB LPDDR5X內存。此外NVIDIA還宣稱Grace可以通過NVLink-C2C與Hopper GPU連接,組成Grace Hopper超級芯片。

NVIDIA Grace是基于Arm Neoverse V2 IP的重要產品。目前尚未公布NVIDIA Grace的晶體管規模,但可以參考基于Arm Neoverse V1的AWS Graviton 3和阿里云倚天710的數據。根據推測,基于Arm Neoverse V1的AWS Graviton 3約有550億晶體管,對應64核和8通道DDR5內存;基于Arm Neoverse N2的阿里云倚天710約有600億晶體管,對應128核、8通道DDR5內存和96通道PCIe 5.0。從NVIDIA Grace Hopper超級芯片的渲染圖來看,Grace的芯片面積與Hopper接近,已知后者為800億晶體管,因此推測72核的Grace芯片的晶體管規模大于Graviton 3和倚天710是合理的,并與Grace基于Neoverse V2(支持Arm V9指令集、SVE2)的情況相符。

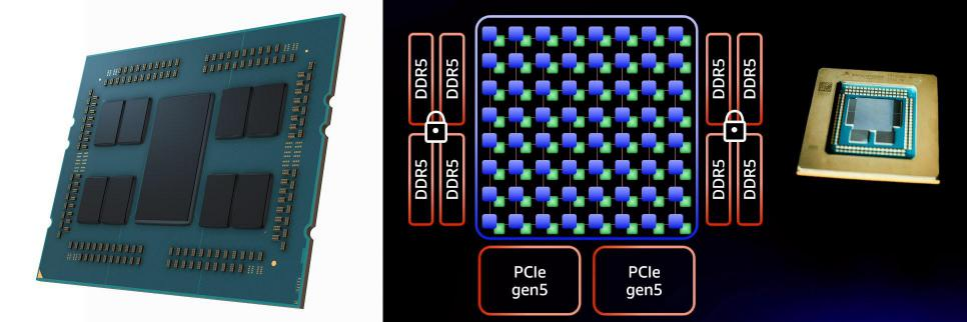

Arm Neoverse V2配套的互連方案是CMN-700,在NVIDIA Grace中稱為SCF(Scalable Coherency Fabric可擴展一致性結構)。英偉達聲稱Grace的網格支持超過72個CPU核心的擴展,實際上在英偉達白皮書的配圖中可以數出80個CPU核心。每個核心有1MB L2緩存,整個CPU有高達117MB的L3緩存(平均每個核心1.625MB),明顯高于其他同級別的Arm處理器。

NVIDIA Grace CPU 的網格布局

NVIDIA Grace芯片內的SCF提供3.2 TB/s的分段帶寬,連接CPU核心、內存控制器和NVLink等系統I/O控制器。網格中的節點稱為CSN通常每個CSN連接2個核心和2個SCC(SCF緩存分區)。然而,從示意圖可以看出,位于網格角落的4個CSN連接了2個核心和1個SCC,而位于中部兩側的4個CSN連接了1個核心和2個SCC。總體而言,Grace的網格內應該有80個核心和76個SCC,其中8個核心可能由于良率等因素而被屏蔽。而網格外圍缺失的4個核心和8個SCC的位置被用于連接NVLink、NVLink-C2C、PCIe和LPDDR5X內存控制器等。

NVIDIA Grace支持Arm的許多管理特性,如服務器基礎系統架構(SBSA)、服務器基礎啟動要求(SBBR)、內存分區與監控(MPAM)和性能監控單元(PMU)。通過Arm的內存分區和監控功能,可以解決由于共享資源競爭而導致的CPU訪問緩存過程中性能下降的問題。高優先級的任務可以優先占用L3緩存,或者根據虛擬機預先劃分資源,實現業務之間的性能隔離。

NVIDIA Grace CPU 超級芯片

作為最新、最強版本的Arm架構核心(Neoverse V2)的代表,NVIDIA Grace引起業界的高度關注,尤其是考慮到它將受益于NVIDIA強大的GPGPU技術。人們在GTC 2023上終于有機會親眼目睹Grace的實物,但實際市場表現還需要一段時間來驗證。大家對Grace在超級計算和機器學習等領域的表現抱有很高的期待。

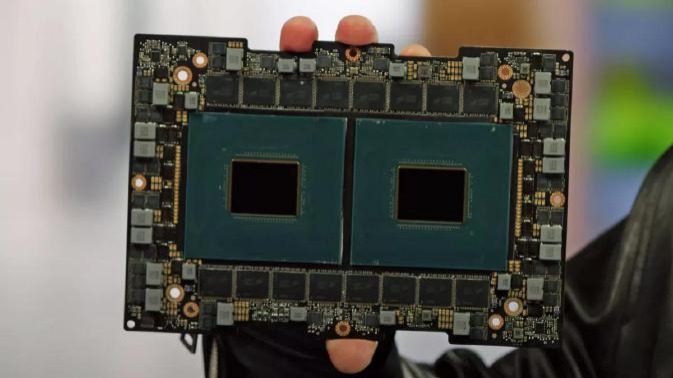

GTC2023 演講中展示的 Grace 超級芯片實物

六、網格架構的兩類 Chiplet

Ampere One采用流行的Chiplet技術,擁有多達192個核心和384MB L2緩存,這并不令人意外。目前普遍的推測是,它的設計類似于AWS Graviton3即將CPU和緩存單獨放置在一個die上,DDR控制器的die位于其兩側,而PCIe控制器的die位于其下方。將CPU核心和緩存與負責外部I/O的控制器分離在不同的die上,是實現服務器CPU的Chiplet的主流做法。

IOD 居 中 的 AMD 第 二 代 EPYC 處 理 器, 與 核 心 die 居 中 的 AWS Graviton3 處理器

正如之前提到的AMD EPYC家族處理器采用星形拓撲結構,將I/O部分集中放置在一個IOD上,而CPU核心和緩存(CCD)則環繞在周圍。這是由網格架構的特性所決定的,要求CPU核心和緩存必須位于中央,而I/O部分則分散在外圍。因此,當進行拆分時,布局會相反,中央的die會更大,而周圍的die會更小。

與EPYC家族的架構相比,網格架構具有更強的整體性,天生具有單體式(Monolithic)結構不太適合拆分。在網格架構中,必須考慮交叉點(節點)的利用率問題,如果有太多的空置交叉點,會導致資源浪費,因此縮小網格規模可能更為有效。

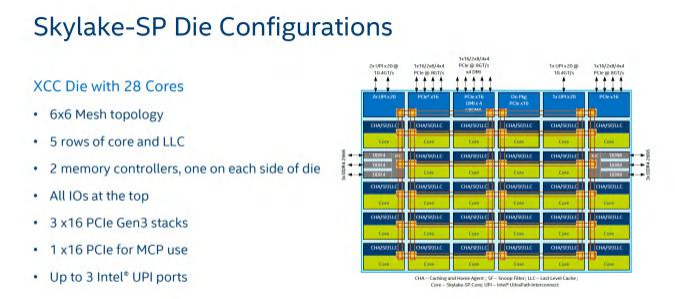

以初代英特爾至強可擴展處理器為例,為了滿足核數(Core Count,CC)從4到28的范圍變化提供三種不同構型的die(die chop)。其中,6×6的XCC(eXtreme CC,最多核或極多核)支持最多28個核心;6×4的HCC(High CC,高核數)支持最多18個核心;4×4的LCC(Low CC,低核數)支持最多10個核心。

從這個角度來看,Ampere One不支持128核及以下是合理的,除非增加die的構型,但這涉及到公司規模和出貨量的支持需要量產來解決。而第四代英特爾至強可擴展處理器提供了兩種構型的die。

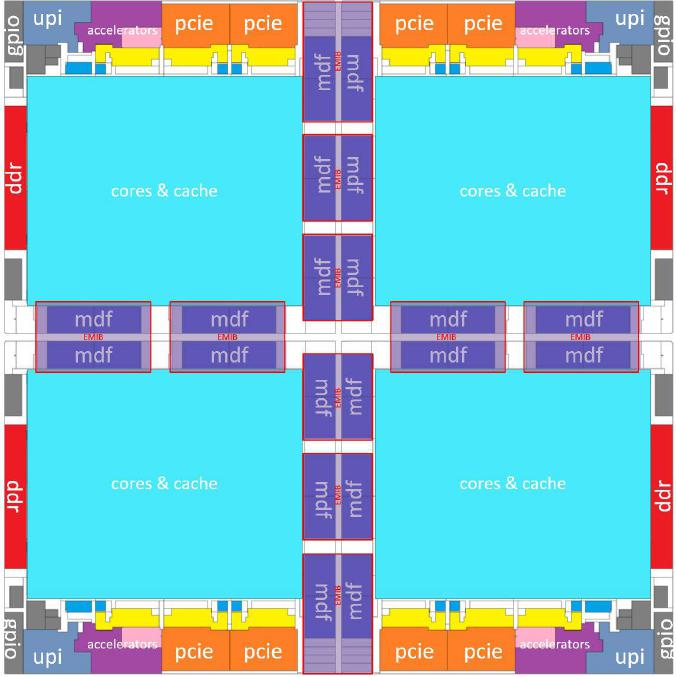

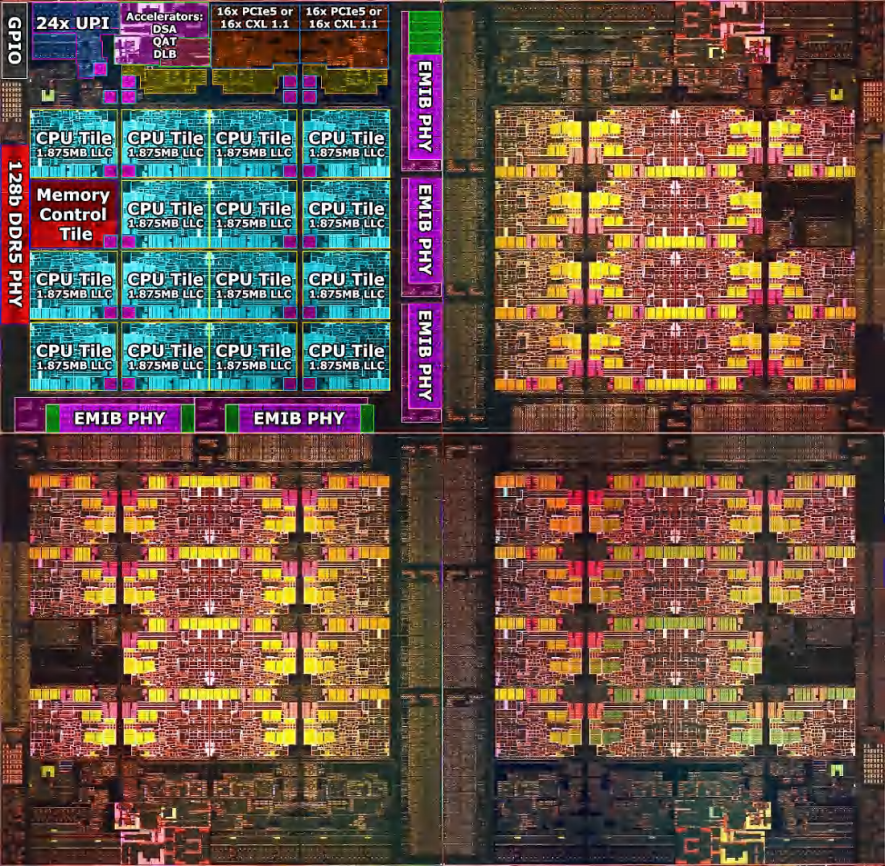

其中,MCC(Medium CC中等核數)主要滿足32核及以下的需求,比代號Ice Lake的第三代英特爾至強可擴展處理器的40核要低,因此網格規模比后者的7×8少了1列為7×7,最多可以安置34個核心及其緩存。而36到60個核心的需求則必須由XCC來滿足,它是前面提到的Chiplet版本,將網格架構從中間切割成4等分,非常獨特。

XCC版本的第四代英特爾至強可擴展處理器由兩種互為鏡像的die拼成2×2的大矩陣,因此整體具有高度對稱性上下和左右都對稱,而前三代產品和同代的MCC版本則沒有如此對稱。

英特爾認為,第四代英特爾至強可擴展處理器(XCC版本)由4個die拼接而成,形成了一個準單體式(quasi-monolithic)的die。單體式的概念比較容易理解常見的網格架構就是這樣的。在第四代英特爾至強可擴展處理器中外圈左右是DDR內存控制器,上下是PCIe控制器和集成的加速器(DSA/QAT/DLB/IAA),而UPI位于四個角落,這是典型的網格架構布局。

第四代英特爾至強可擴展處理器的 EMIB 連接

算存互連:Chiplet 與 CXL

“東數西存”是“東數西算”的基礎和前奏,而不是子集。其涉及到數據、存儲和計算之間的關系。數據通常在人口密集的東部產生,而存儲則在地廣人稀的西部進行。其中主要難點在于如何以較低的成本完成數據傳輸。計算需要頻繁地訪問數據,而在跨地域的情況下,網絡的帶寬和時延成為難以克服的障礙。

與數據傳輸和計算相比,存儲并不消耗太多能源,但占用大量空間。核心區域始終是稀缺資源,就像核心城市的核心地段不會被用來建設超大規模的數據中心一樣,CPU的核心區域也只能留給存儲器的硅片面積有限。

實現“東數西算”并非一蹴而就的事情,超大規模的數據中心與核心城市也逐漸疏遠而且并不是越遠越好。同樣圍繞CPU已經建立一套分層的存儲體系,盡管從高速緩存到內存都屬于易失性存儲器(內存)但通常那些處于中間狀態的數據對訪問時延的要求更高,因此需要更靠近核心。如果是需要長期保存的數據,離核心遠一些也沒有關系,而訪問頻率較低的數據可以存儲在較遠的位置(西存)。

距離CPU核心最近的存儲器是各級緩存(Cache),除了基于SRAM的各級Cache之外。即使在緩存中也存在遠近之分。在現代CPU中,L1和L2緩存已經成為核心的一部分則需要考慮占用面積的主要是L3緩存。

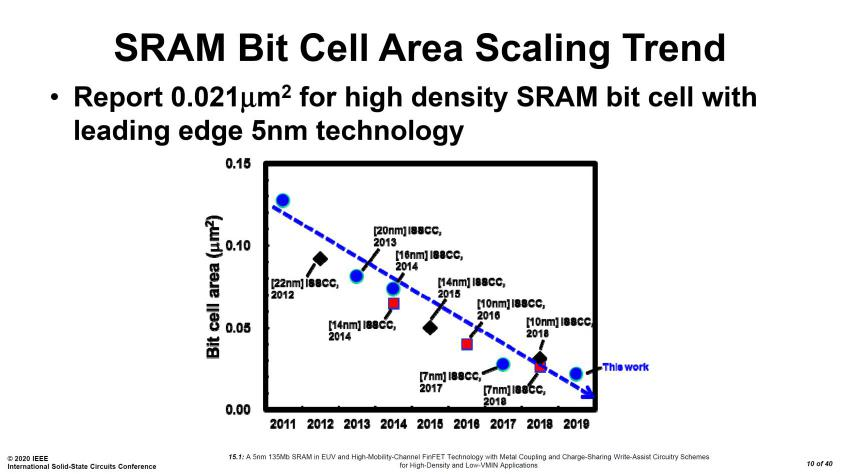

一、SRAM 的面積律

現在是2023年制造工藝正在向3納米邁進。臺積電公布其N3制程的SRAM單元面積為0.0199平方微米,相比N5制程的面積為0.021平方微米,僅縮小了5%。更為困擾的是由于良率和成本問題,預計N3并不會成為臺積電的主力工藝客戶們更關注第二代3納米工藝N3E。而N3E的SRAM單元面積為0.021平方微米與N5工藝完全相同。

就成本而言據傳N3一片晶圓的成本為2萬美元而N5的報價為1.6萬美元,這意味著N3的SRAM比N5貴25%。作為參考Intel的7納米制程(10納米)的SRAM面積為0.0312平方微米Intel的4納米制程(7納米)的SRAM面積為0.024平方微米與臺積電的N5和N3E工藝相當。

盡管半導體制造商的報價是商業機密但SRAM的價格越來越高,密度也難以再提高。因此將SRAM單獨制造并與先進封裝技術結合,以實現高帶寬和低時延成為一種合理的選擇。

二、向上堆疊,翻越內存墻

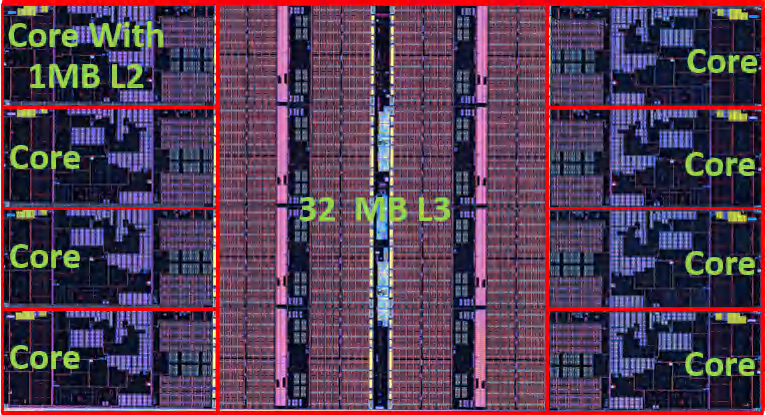

當前,AMD的架構面臨內存性能落后的問題。其中原因包括核心數量較多導致平均每個核心的內存帶寬偏小、核心與內存的距離較遠導致延遲較大以及跨CCD的帶寬過小等。為了彌補訪問內存的劣勢,AMD需要使用較大規模的L3緩存。

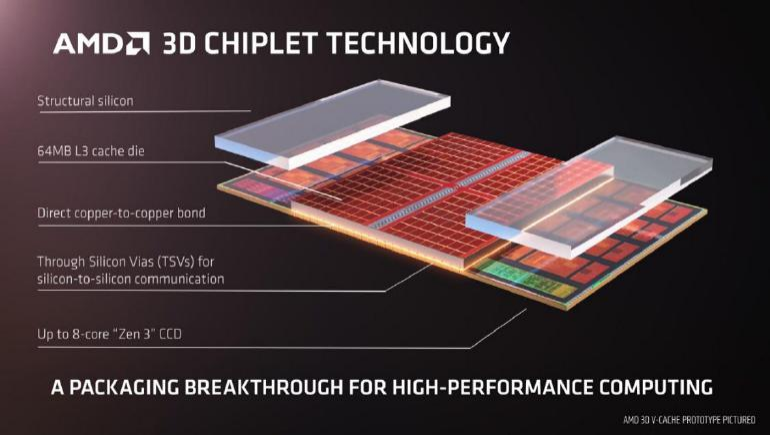

然而,從Zen 2到Zen 4架構,AMD每個CCD的L3緩存仍然保持32MB的容量并沒有與時俱進。為了解決SRAM規模滯后的問題,AMD決定將擴容SRAM的機會獨立于CPU之外。在代號為Milan-X的EPYC 7003X系列處理器上,AMD應用了第一代3D V-Cache技術。這些處理器采用Zen 3架構核心,每個緩存(L3緩存芯片,簡稱L3D)的容量為64MB,面積約為41mm2采用7納米工藝制造。

緩存芯片通過混合鍵合、TSV(Through Silicon Vias,硅通孔)工藝與CCD(背面)垂直連接。該單元包含4個組成部分:最底層的CCD、上層中間部分L3D、以及上層兩側的支撐結構,采用硅材質以在垂直方向上平衡整個結構并將下方CCX(Core Complex,核心復合體)部分的熱量傳導到頂蓋。

Zen4 CCD 的布局,請感受一下 L3 Cache 的面積

在Zen 3架構核心設計之初AMD就預留了必要的邏輯電路和TSV電路,相關部分大約使CCD的面積增加4%。L3D的堆疊位置恰好位于CCD的L2/L3緩存區域上方。這一設計既符合雙向環形總線內CCD中緩存居中、CPU核心分布在兩側的布局。又考慮到(L3)緩存的功率密度相對較低于CPU核心,有利于控制整個緩存區域的發熱量。

3D V-Cache 結構示意圖

Zen 3架構的L3緩存由8個切片組成每片4MB;而L3D設計為8個切片每片8MB。兩組緩存的每個切片之間有1024個TSV連接,總共有8192個連接。AMD聲稱這額外的L3緩存只會增加4個周期的延遲。

隨著Zen 4架構處理器的推出,第二代3D V-Cache也登場了。它的帶寬從上一代的2TB/s提升到2.5TB/s容量仍然為64MB,制程仍然是7納米,但面積縮減到了36mm2。這個面積的縮減主要來自TSV部分,AMD聲稱在TSV的最小間距沒有縮小的情況下,相關區域的面積縮小了50%。代號為Genoa-X的EPYC系列產品預計將于2023年中發布。

增加SRAM容量可以大幅提高緩存命中率,減少內存延遲對性能的影響。AMD的3D V-Cache以相對合理的成本實現了緩存容量的巨大提升(在CCD內L3緩存的基礎上增加了2倍),對性能的改進也非常明顯。

應用 3D V-Cache 的 AMD EPYC 7003X 處理器

三、HBM 崛起:從 GPU 到 CPU

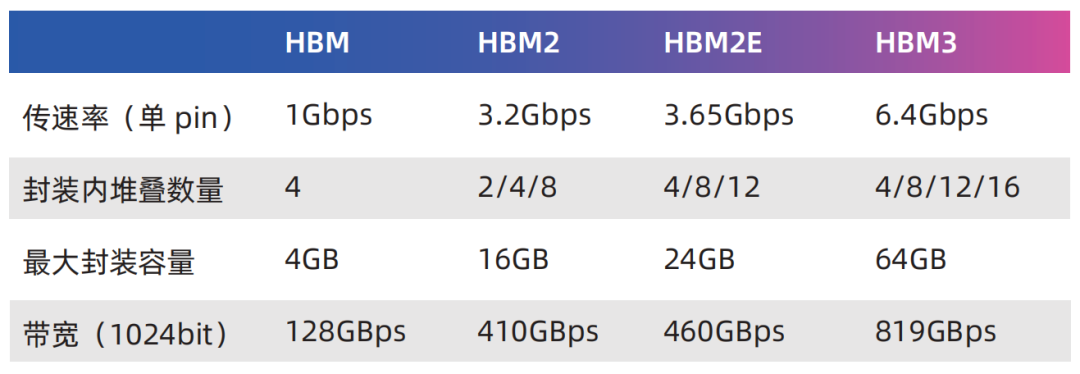

HBM(High Bandwidth Memory)是一種由AMD和SK海力士于2014年共同發布的技術,它使用TSV技術將多個DRAM芯片堆疊在一起,大幅提高容量和數據傳輸速率。隨后三星、美光、NVIDIA、Synopsys等公司也積極參與這一技術路線。標準化組織JEDEC也將HBM2列入了標準(JESD235A)并陸續推出了HBM2e(JESD235B)和HBM3(JESD235C)。主要得益于堆疊封裝和巨大的位寬(單封裝1024位),HBM提供遠遠超過其他常見內存形式(如DDR DRAM、LPDDR、GDDR等)的帶寬和容量。

典型的實現方式是通過2.5D封裝與處理器核心連接,在CPU、GPU等產品中廣泛應用。早期有人將HBM視為L4緩存,從TB/s級別的帶寬來看這個觀點也是合理的。而從容量的角度來看HBM比SRAM或eDRAM要大得多。

因此,HBM既可以勝任(一部分)緩存的工作也可以作為高性能內存使用。AMD是HBM的早期采用者,目前AMD Instinct MI250X計算卡在單一封裝內集成了2顆計算核心和8顆HBM2e,總容量為128GB,帶寬達到3276.8GB/s。NVIDIA主要在專業卡中應用HBM其2016年的TESLA P100 HBM版配備了16GB HBM2,隨后的V100則配備了32GB HBM2。目前熱門的A100和H100也都有HBM版,前者最大提供80GB HBM2e,帶寬約為2TB/s;后者升級到HBM3,帶寬約為3.9TB/s。華為的昇騰910處理器也集成了4顆HBM。

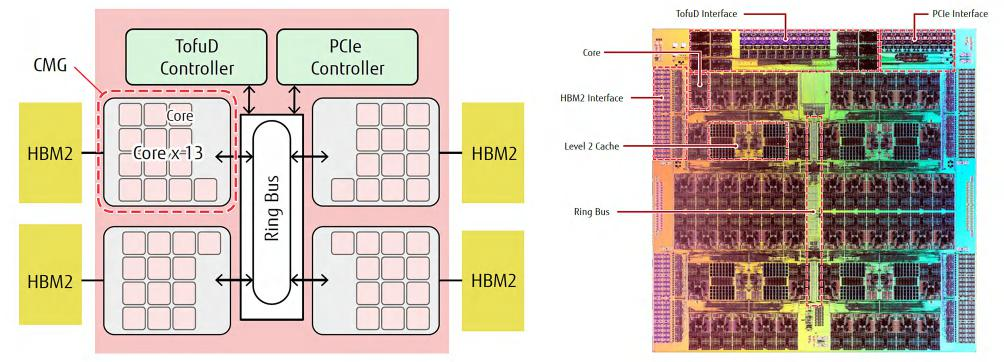

對于計算卡、智能網卡、高速FPGA等產品來說,HBM作為GDDR的替代品,應用已非常成熟。CPU也已經開始集成HBM,其中最突出的案例是曾經問鼎超算TOP500的富岳(Fugaku),它采用富士通研發的A64FX處理器。A64FX基于Armv8.2-A架構,采用7納米制程,在每個封裝中集成了4顆HBM2,總容量為32GB,帶寬為1TB/s。

富士通 A64FX CPU

四、向下發展:基礎層加持

英特爾數據中心Max GPU系列引入了Base Tile的概念,可以將其看作是基礎芯片。相對于中介層的概念,我們也可以將基礎芯片視為基礎層。表面上看基礎層和硅中介層的功能類似,都用于承載計算核心和高速I/O(如HBM),但實際上基礎層的功能更加豐富。

硅中介層主要利用成熟的半導體光刻、沉積等工藝(如65納米級別),在硅上形成高密度的電氣連接。而基礎層更進一步:既然已經在加工多層圖案,為什么不將邏輯電路等功能也整合進去呢?

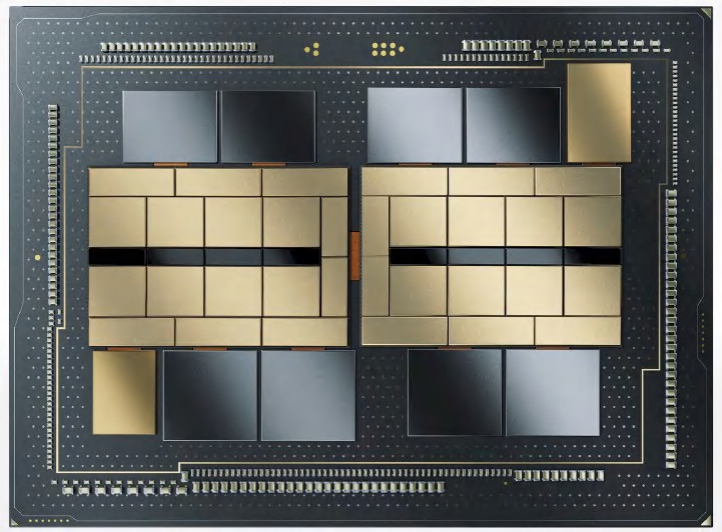

英特爾數據中心 Max GPU

在ISSCC 2022上,英特爾展示了英特爾數據中心Max GPU的Chiplet(小芯片)架構。其中基礎芯片的面積為640mm2,采用了英特爾7納米制程,這是目前英特爾用于主流處理器的先進制程。為什么在"基礎"芯片上需要使用先進制程呢?這是因為英特爾將高速I/O的SerDes都集成在基礎芯片中,類似于AMD的IOD。這些高速I/O包括HBM PHY、Xe Link PHY、PCIe 5.0以及緩存等。這些電路都更適合使用5納米及以上的工藝制造,將它們與計算核心解耦后重新打包在同一制程內是一個相當合理的選擇。

英特爾數據中心 Max GPU 的 Chiplet 架構

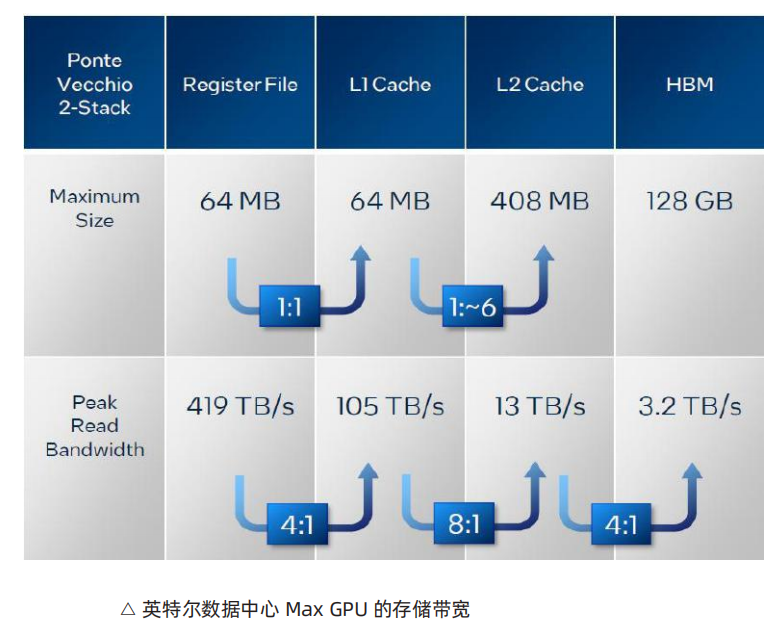

英特爾數據中心Max GPU系列通過Foveros封裝技術,在基礎芯片上方疊加了8顆計算芯片(Compute Tile)和4顆RAMBO芯片(RAMBO Tile)。計算芯片采用臺積電N5工藝制造,每顆芯片擁有4MB的L1 Cache。RAMBO是"Random Access Memory Bandwidth Optimized"的縮寫,即帶寬優化的隨機訪問存儲器。獨立的RAMBO芯片基于英特爾7納米制程,每顆芯片有4個3.75MB的Bank,總共提供15MB的容量。每組4顆RAMBO芯片共提供了60MB的L3 Cache。此外,在基礎芯片中還有一個容量為144MB的RAMBO,以及L3 Cache的交換網絡(Switch Fabric)。

因此,在英特爾數據中心Max GPU中,基礎芯片通過Cache交換網絡將基礎層內的144MB Cache與8顆計算芯片和4顆RAMBO芯片的60MB Cache組織在一起,總共提供了204MB的L2/L3 Cache。整個封裝由兩組組成,即總共408MB的L2/L3 Cache。每組處理單元通過Xe Link Tile與其他7組進行連接。Xe Link芯片采用臺積電N7工藝制造。

XHPC 的邏輯架構

前面已經提到,I/O 芯片獨立是大勢所趨,共享 Cache 與 I/O 拉近也是趨勢。英特爾數據中心 Max GPU 將 Cache 與各種高 速 I/O 的 PHY 集成在同一芯片內,正是前述趨勢的集大成者。 至于 HBM、Xe Link 芯片,以及同一封裝內相鄰的基礎芯片,則 通過 EMIB(爆炸圖中的橙色部分)連接在一起。

英特爾數據中心 Max GPU 爆炸圖

根據英特爾在 HotChips 上公布的數據,英特爾數據中心 Max GPU 的 L2 Cache 總帶寬可以達到 13TB/s。考慮到封裝了兩組基礎芯片和計算芯片給帶寬打個對折,基礎芯片和 4 顆 RAMBO 芯片的帶寬是 6.5TB/s,依舊遠遠超過目前至強和 EPYC 的 L2、L3 Cache 的帶寬。其實之前 AMD 已經通過指甲蓋大小的 3D V-Cache 證明 3D 封裝的性能,那就更不用說英特爾數據中心 Max GPU 的 RAMBO 及基礎芯片的面積。

回顧一下3D V-Cache的一個弱點即散熱不良。我們還發現將Cache集成到基礎芯片中有一個優點:將高功耗的計算核心安排在整個封裝的上層,更有利于散熱。進一步觀察在網格化的處理器架構中L3 Cache并不是簡單的幾個塊(切片),而是分成數十甚至上百個單元分別連接到網格節點上。基礎芯片在垂直方向上可以完全覆蓋或容納處理器芯片,其中的SRAM可以分成相等數量的單元與處理器的網格節點相連接。

目前已經成熟的3D封裝技術中,凸點間距在30到50微米的范圍內足以滿足每平方毫米內數百至數千個連接的需求,可以滿足當前網格節點帶寬的需求。當然更高密度的連接也是可行的,10微米甚至亞微米的技術正在不斷推進中,但優先考慮的場景是HBM、3D NAND等高度定制化的內部堆棧混合鍵合,可能并不適合Chiplet對靈活性的需求。

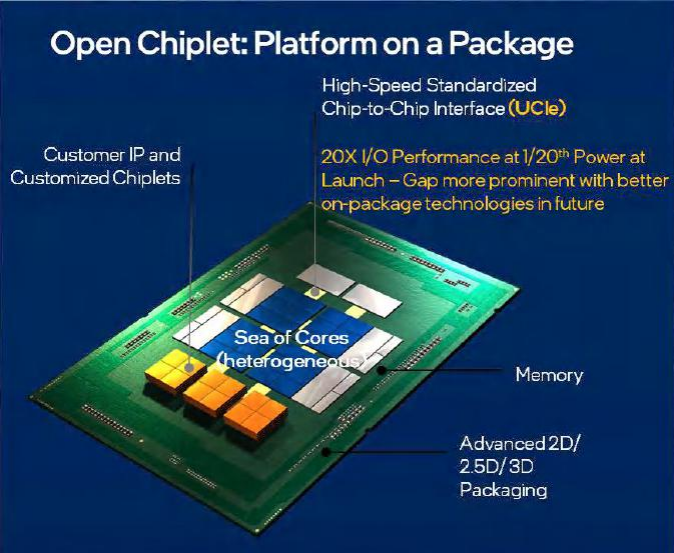

五、標準化:Chiplet 與 UCIe

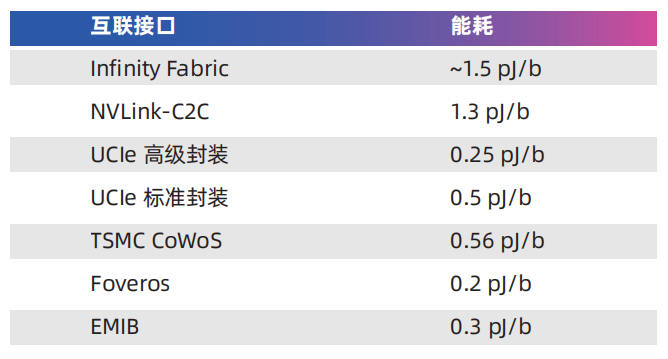

為了實現這一愿景,2022年3月,通用處理器市場的核心參與者,包括Intel、AMD、Arm等,共同發布新的互聯標準UCIe(Universal Chiplet Interconnect Express通用小芯片互連通道),旨在解決Chiplet的行業標準化問題。這一標準的推出將有助于推動Chiplet技術的發展和應用。

由于標準的主導者與PCIe和CXL(Compute Express Link)已經有密切的關系,因此UCIe非常強調與PCIe/CXL的協同,提供在協議層本地端進行PCIe和CXL協議映射的功能。與CXL的協同說明UCIe的目標不僅僅是解決芯片制造中的互聯互通問題,而是希望芯片與設備、設備與設備之間的交互是無縫的。

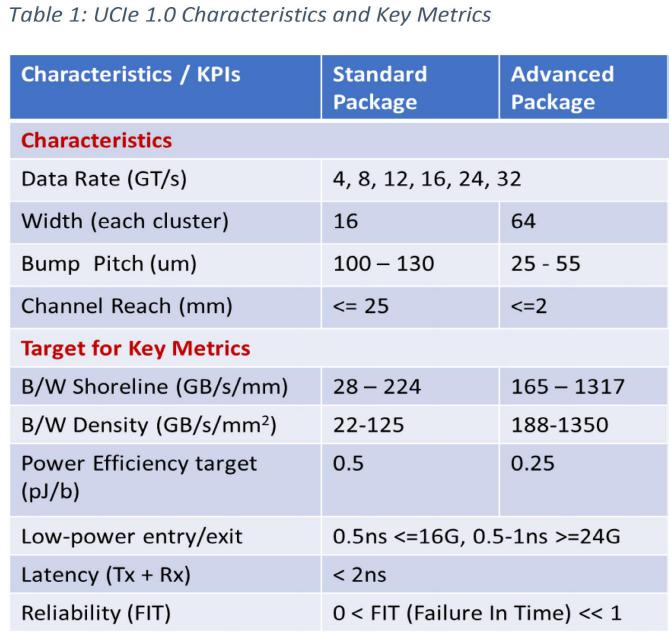

在UCIe 1.0標準中展現兩種層面的應用:Chiplet(封裝內)和Rack space(封裝外)。這意味著UCIe可以在芯片內部實現Chiplet之間的互聯,同時也可以在封裝外部實現芯片與設備之間的互聯。這種靈活性使得UCIe能夠適應不同的應用場景。

UCIe 規劃的機架連接交給了 CXL

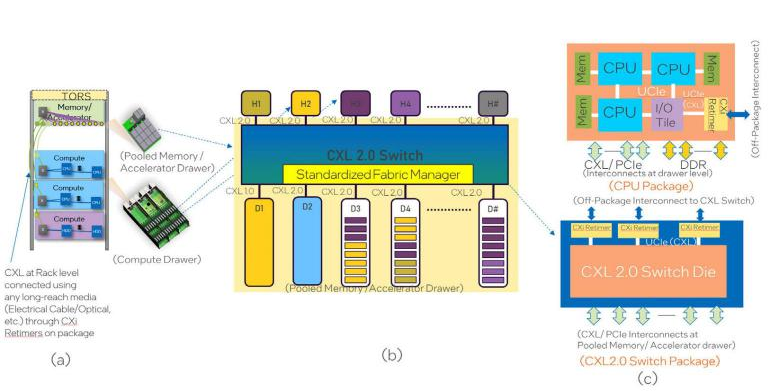

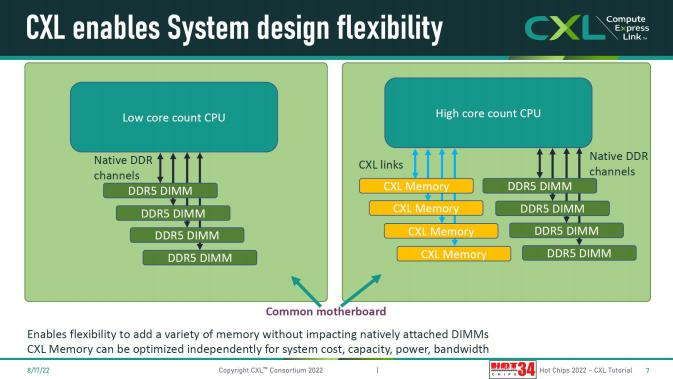

1、CXL:內存的解耦與擴展

相對于PCIe,CXL最重要的價值在于減少各子系統內存的訪問延遲(理論上PCIe的延遲為100納秒級別而CXL為10納秒級別)。例如GPU訪問系統內存時,這對于設備之間的大容量數據交換至關重要。這種改進主要源于兩個方面:

首先,PCIe在設計之初并沒有考慮緩存一致性問題。當通過PCIe進行跨設備的DMA讀寫數據時,在操作延遲期間,內存數據可能已經發生變化,因此需要額外的驗證過程,這增加了指令復雜度和延遲。而CXL通過CXL.cache和CXL.memory協議解決緩存一致性問題,簡化操作也減少延遲。

其次,PCIe的初衷是針對大流量進行優化,針對大數據塊(512字節、1KB、2KB、4KB)進行優化,希望減少指令開銷。而CXL則針對64字節傳輸進行優化,對于固定大小的數據塊而言操作延遲較低。換句話說,PCIe的協議特點更適合用于以NVMe SSD為代表的塊存儲設備,而對于注重字節級尋址能力的計算型設備CXL更為適合。

除充分釋放異構計算的算力,CXL還讓內存池化的愿景看到了標準化的希望。CXL Type 3設備的用途是內存緩沖,利用CXL.io和CXL.memory的協議實現擴展遠端內存。在擴展后,系統內存的帶寬和容量即為本地內存和CXL內存模塊的疊加。

在新一代CPU普遍支持的CXL 1.0/1.1中,CXL內存模塊首先實現主機級的內存擴展,試圖突破傳統CPU內存控制器的發展瓶頸。CPU核心數量增長的速度遠遠快于內存通道的增加速度是其中的原因。

在過去的十年間CPU的核心數量從8到12個增長到了60甚至96個核心,而每個插槽CPU的內存通道數僅從4通道增加到8或12通道。每個通道的內存在此期間也經歷三次大的迭代,帶寬大約增加1.5到2倍,存儲密度大約增加4倍。從發展趨勢來看,每個CPU核心所能分配到的內存通道數量在明顯下降,每個核心可以分配的內存容量和內存帶寬也有所下降。這是內存墻的一種表現形式,導致CPU核心無法充分獲取數據以處于滿負荷的運行狀態,從而導致整體計算效率下降。

2、UCIe 與異構算力

隨著人工智能時代的到來,異構計算已經成為常態。原則上只要功率密度允許,這些異構計算單元的高密度集成可以由UCIe完成。除集成度的考慮,標準化的Chiplet還帶來功能和成本的靈活性。對于不需要的單元,在制造時可以不參與封裝,而對于傳統處理器而言,無用的單元常常成為無用的"暗硅",意味著成本的浪費。一個典型的例子是DSA,如英特爾第四代可擴展至強處理器中的若干加速器,用戶可以付費開啟,但是如果用戶不付費,這些DSA其實已經制造出來。

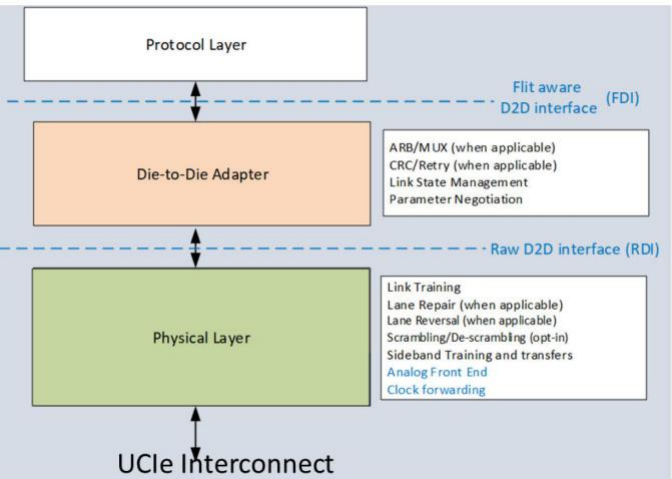

UCIe包括協議層(Protocol Layer)、適配層(Adapter Layer)和物理層(Physical Layer)。協議層支持PCIe 6.0、CXL 2.0和CXL 3.0同時也支持用戶自定義的協議。根據不同的封裝等級,UCIe還提供不同的Package模塊。通過使用UCIe的適配層和PHY替換PCIe/CXL的PHY和數據包可以實現更低功耗和性能更優的Die-to-Die互連接口。

UCIe考慮了兩種不同等級的封裝:標準封裝(Standard Package)和先進封裝(Advanced Package)。這兩種封裝在凸塊間距、傳輸距離和能耗方面存在數量級的差異。例如,對于先進封裝,凸塊間距(Bump Pitch)為25~55μm,代表采用硅中介層的2.5D封裝技術特點。以英特爾的EMIB為例,當前的凸塊間距約為50μm,未來將演進至25μm甚至10μm。臺積電的InFO、CoWoS等也具有類似的規格和演進趨勢。而標準封裝(2D)的規格則對應目前應用最廣泛的有機載板。

不同封裝的信號密度也存在本質差異。標準封裝模塊對應的是16對數據線(TX、RX),而高級封裝模塊則包含64對數據線。每32個數據管腳還額外提供2個用于Lane修復的管腳。如果需要更大的帶寬,可以擴展更多的模塊并且這些模塊的頻率是可以獨立設置的。

需要特別提到的是,UCIe與高速PCIe的深度集成使其更適合高性能應用。實際上,SoC(片上系統)是一個廣義的概念而UCIe面向的是宏觀系統級的集成。傳統觀念中適合低成本、高密度的SoC可能需要集成大量的收發器、傳感器、塊存儲設備等。例如,一些面向邊緣場景的推理應用和視頻流處理的IP設計企業非常活躍,這些IP可能需要更靈活的商品化落地方式。由于UCIe不考慮相對低速設備的集成,低速、低成本接口的標準化仍然有空間。

算力互連:由內及外,由小漸大

隨著"東數西算"工程的推進,出現了細分場景如"東數西渲"和"東數西訓"。視頻渲染和人工智能(AI)/機器學習(ML)的訓練任務本質上都是離線計算或批處理,可以在"東數西存"的基礎上進行。即原始素材或歷史數據傳輸到西部地區的數據中心后,在該地區獨立完成計算過程,與東部地區的數據中心交互較少,因此不會受到跨地域時延的影響。換句話說,"東數西渲"和"東數西訓"的業務邏輯成立是因為計算與存儲仍然就近耦合,不需要面對跨地域的"存算分離"挑戰。

在服務器內部,CPU和GPU之間存在類似但不同的關系。對于當前熱門的大模型來說,對計算性能和內存容量都有很高的要求。然而,CPU和GPU之間存在一種"錯配"現象:GPU的AI算力明顯高于CPU,但直接的內存(顯存)容量通常不超過100GB,與CPU的TB級內存容量相比相差一個數量級。幸運的是CPU和GPU之間的距離可以縮短,帶寬可以提升。通過消除互連瓶頸,可以大大減少不必要的數據移動,提高GPU的利用率。

一、為GPU而生的CPU

NVIDIA Grace CPU的核心基于Arm Neoverse V2架構,其互連架構SCF(可擴展一致性結構)可以看作是定制版的Arm CMN-700網格。然而在外部I/O方面,NVIDIA Grace CPU與其他Arm和x86服務器有很大不同,這體現NVIDIA開發這款CPU的主要意圖,即為需要高速訪問大內存的GPU提供服務。

在內存方面,Grace CPU具有16個LPDDR5X內存控制器,這些內存控制器對應著封裝在一起的8個LPDDR5X芯片,總容量為512GB。經過ECC開銷后,可用容量為480GB。因此可以推斷有一個內存控制器及其對應的LPDDR5X內存die用于ECC。根據NVIDIA官方資料,與512GB內存容量同時出現的內存帶寬參數是546GB/s而與480GB(帶ECC)同時出現的是約500GB/s,實際的內存帶寬應該在512GB/s左右。

PCIe控制器是必不可少的Arm CPU的慣例是將部分PCIe通道與CCIX復用,但這樣的CCIX互連帶寬相對較弱,不如英特爾專用于CPU間互連的QPI/UPI。

NVIDIA Grace CPU提供68個PCIe 5.0通道,其中有2個x16通道可以用作12通道一致性NVLink(cNVLINK)。真正用于芯片(CPU/GPU)之間互連的是cNVLINK/PCIe隔"核"相望的NVLink-C2C接口,其帶寬高達900GB/s。

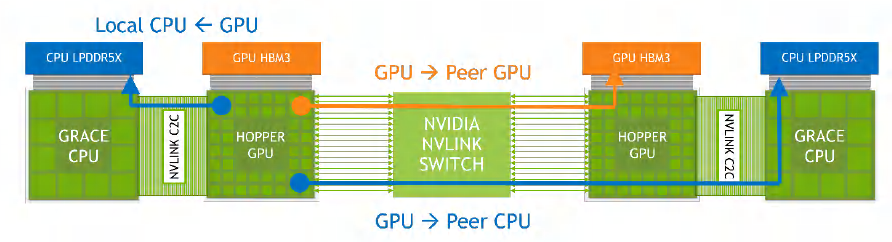

NVLink-C2C中的C2C代表芯片到芯片之間的連接。根據NVIDIA在ISSCC 2023論文中的描述,NVLink-C2C由10組連接組成(每組9對信號和1對時鐘),采用NRZ調制,工作頻率為20GHz,總帶寬為900GB/s。每個封裝內的傳輸距離為30mm,PCB上的傳輸距離為60mm。對于NVIDIA Grace CPU超級芯片,使用NVLink-C2C連接兩個CPU可以構成一個144核的模塊;而對于NVIDIA Grace Hopper超級芯片,即將Grace CPU和Hopper GPU進行互聯。

NVLink-C2C的900GB/s帶寬是非常驚人的數據。作為參考,Intel代號為Sapphire Rapids的第四代至強可擴展處理器包含3或4組x24 UPI 2.0(@16GT/s)多個處理器之間的總帶寬接近200GB/s;而AMD第四代EPYC處理器使用的GMI3接口用于CCD與IOD之間的互聯帶寬為36GB/s,而CPU之間的Infinity Fabric相當于16通道PCIe 5.0,帶寬為32GB/s。在雙路EPYC 9004之間可以選擇使用3或4組Infinity Fabric互聯,4組的總帶寬為128GB/s。

通過巨大的帶寬,兩顆Grace CPU可以被緊密聯系在一起,其"緊密"程度遠超傳統的多路處理器系統,已經足以與基于有機載板的大多數芯片封裝方案(2D封裝)相匹敵。要超越這個帶寬,需要引入硅中介層(2.5D封裝)的技術。例如,蘋果M1 Ultra的Ultra Fusion架構利用硅中介層連接兩顆M1 Max芯粒。蘋果聲稱Ultra Fusion可以同時傳輸超過10,000個信號,實現高達2.5TB/s的低延遲處理器互聯帶寬。Intel的EMIB也是一種2.5D封裝技術,其芯粒間的互聯帶寬也應當達到TB級別。

NVLink-C2C的另一個重要應用案例是GH200 Grace Hopper超級芯片,它將一顆Grace CPU與一顆Hopper GPU進行互聯。Grace Hopper是世界上第一位著名的女性程序員,也是"bug"術語的發明者。因此,NVIDIA將這一代CPU和GPU分別命名為Grace和Hopper,這個命名實際上有著深刻的意義,充分說明在早期規劃中,它們就是緊密結合的關系。

NVIDIA Grace Hopper 超級芯片主要規格

CPU和GPU之間的數據交換效率(帶寬、延遲)在超大機器學習模型時代尤為重要。NVIDIA為Hopper GPU配備了大容量高速顯存,全開啟6組顯存控制器,容量達到96GB,帶寬達到3TB/s。

相比之下,獨立的GPU卡H100的顯存配置為80GB,而H100 NVL的雙卡組合則為188GB。Grace CPU搭載了480GB的LPDDR5X內存,帶寬略超過500GB/s。盡管Grace的內存帶寬與使用DDR5內存的競品相當,但CPU與GPU之間的互連才是決定性因素。典型的x86 CPU只能通過PCIe與GPU通信而NVLink-C2C的帶寬遠超PCIe并具有緩存一致性的優勢。

通過NVLink-C2C Hopper GPU可以順暢地訪問CPU內存超過H100 PCIe和H100 SXM。此外,高帶寬的直接尋址還可以轉化為容量優勢,使Hopper GPU能夠尋址576GB的本地內存。

CPU擁有的內存容量是GPU無法比擬的,而GPU到CPU之間的互連(PCIe)是瓶頸。NVLink-C2C的帶寬和能效比優勢是GH200 Grace Hopper超級芯片相對于x86+GPU方案的核心優勢之一。NVLink-C2C每傳輸1比特數據僅消耗1.3皮焦耳能量大約是PCIe 5.0的五分之一具有25倍的能效差異。需要注意的是這種比較并不完全公平,因為PCIe是板間通信,與NVLink-C2C的傳輸距離有本質區別。

NVLink最初是為了實現高速GPU之間的數據交換而設計的,通過NVSwitch的幫助,可以將服務器內部的多個GPU連接在一起,形成一個容量成倍增加的顯存池。

二、NVLink 之 GPU 互連

NVLink的目標是突破PCIe接口的帶寬瓶頸,提高GPU之間交換數據的效率。2016年發布的P100搭載了第一代NVLink,提供160GB/s的帶寬,相當于當時PCIe 3.0 x16帶寬的5倍。V100搭載的NVLink2將帶寬提升到300GB/s 接近PCIe 4.0 x16的5倍。A100搭載了NVLink3帶寬為600GB/s。

H100搭載的是NVLink4,相對于NVLink3,NVLink4不僅增加了鏈接數量,內涵也有比較重大的變化。NVLink3中,每個鏈接通道使用4個50Gb/s差分對,每通道單向25GB/s,雙向50GB/s。A100使用12個NVLink3鏈接,總共構成了600GB/s的帶寬。NVLink4則改為每鏈接通道使用2個100Gb/s差分對,每通道雙向帶寬依舊為50GB/s,但線路數量減少了。

在H100上可以提供18個NVLink4鏈接總共900GB/s帶寬。NVIDIA的GPU大多提供NVLink接口,其中PCIe版本可以通過NVLink Bridge互聯,但規模有限。更大規模的互聯還是得通過主板/基板上的NVLink進行組織,與之對應的GPU有NVIDIA私有的規格SXM。

SXM規格的NVIDIA GPU主要應用于數據中心場景其基本形態為長方形,正面看不到金手指屬于一種mezzanine卡,采用類似CPU插座的水平安裝方式"扣"在主板上,通常是4-GPU或8-GPU一組。其中4-GPU的系統可以不通過NVSwitch即可彼此直連,而8-GPU系統需要使用NVSwitch。

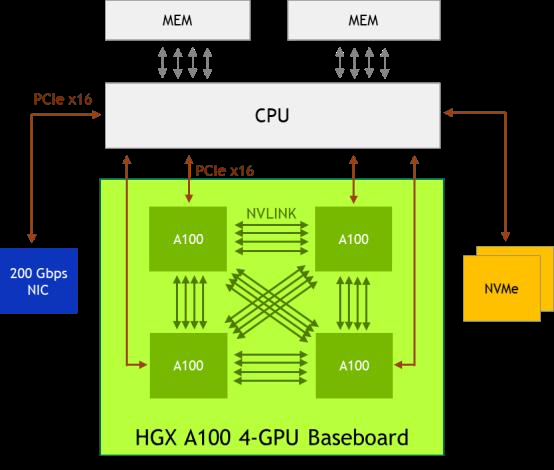

NVIDIA HGX A100 4-GPU 系 統 的 組 織 結 構。 每 個 A100 的 12 條 NVLink 被均分為 3 組,分別與其他 3 個 A100 直聯

經過多代發展,NVLink已經日趨成熟,并開始應用于GPU服務器之間的互連,進一步擴大GPU(以及其顯存)集群的規模。

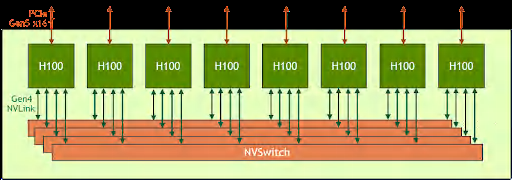

NVIDIA HGX H100 8-GPU 系 統 的 組 織 結 構。 每 個 H100 的 18 條 NVLink 被分為 4 組,分別與 4 個 NVSwitch 互聯。

三、NVLink 組網超級集群

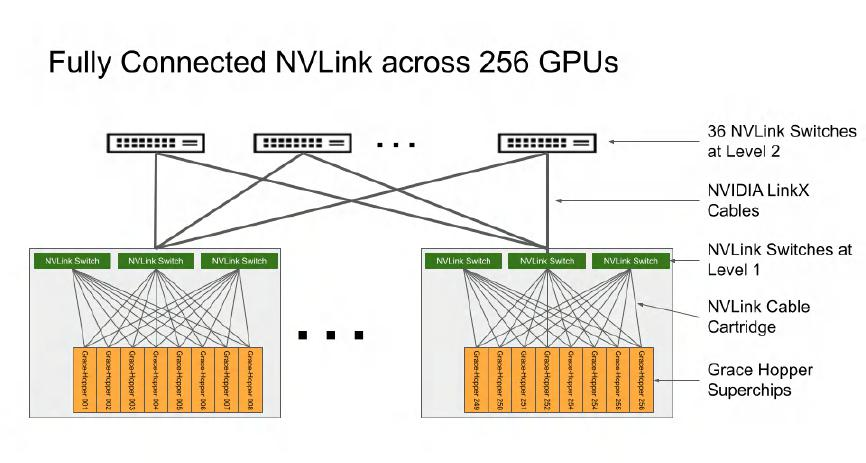

在2023年5月底召開的COMPUTEX上,英偉達宣布了由256個Grace Hopper超級芯片組成的集群,總共擁有144TB的GPU內存。大語言模型(LLM)如GPT對顯存容量的需求非常迫切,巨大的顯存容量符合大模型的發展趨勢。那么,這個前所未見的容量是如何實現的呢?

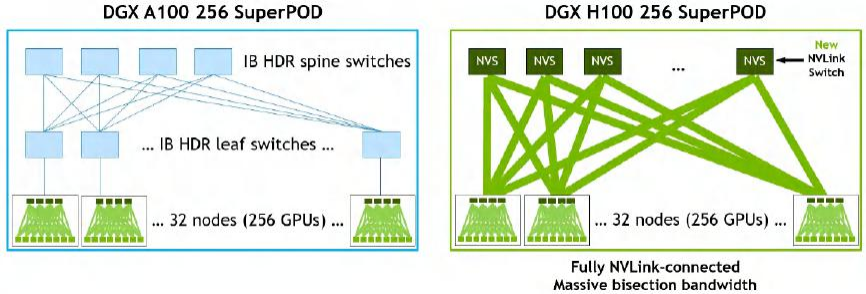

其中一個重大創新是NVLink4 Networks,它使得NVLink可以擴展到節點之外。通過DGX A100和DGX H100構建的256-GPU SuperPOD的架構圖,可以直觀地感受到NVLink4 Networks的特點。在DGX A100 SuperPOD中,每個DGX節點的8個GPU通過NVLink3互聯,而32個節點則需要通過HDR InfiniBand 200G網卡和Quantum QM8790交換機互聯。在DGX H100 SuperPOD中,節點內部采用NVLink4互聯8個GPU,節點之間通過NVLink4 Network互聯,各節點接入了稱為NVLink Switch的設備。

DGX A100 和 DGX H100 256 SuperPOD 架構

根據NVIDIA提供的架構信息NVLink Network支持OSFP(Octal Small Form Factor Pluggable)光口,這也符合NVIDIA聲稱的線纜長度從5米增加到20米的說法。DGX H100 SuperPOD使用的NVLink Switch規格為:端口數量為128個,有32個OSFP籠(cage),總帶寬為6.4TB/s。

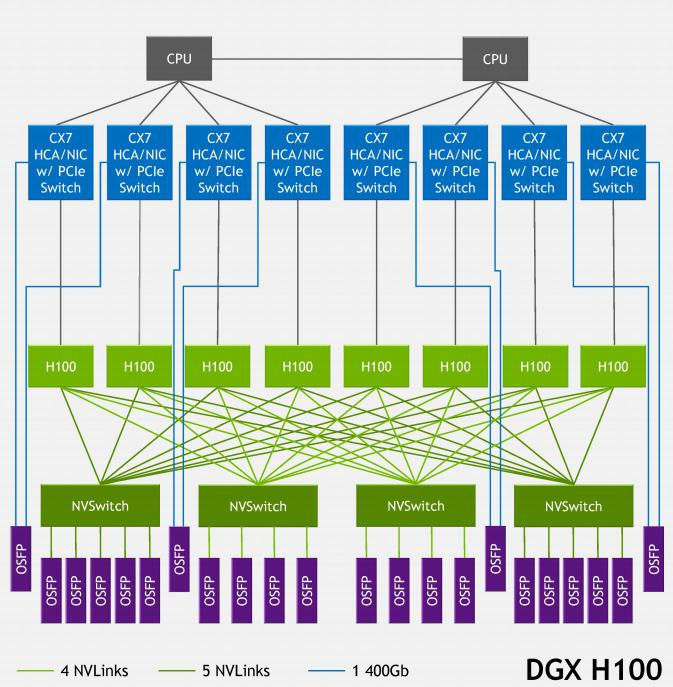

DGX H100 SuperPOD 節點內部的網絡架構

每個8-GPU節點內部有4個NVSwitch,對于DGX H100 SuperPOD每個NVSwitch都通過4或5條NVLink對外連接。每條NVLink的帶寬為50GB/s,對應一個OSFP口相當于400Gb/s,非常成熟。每個節點總共需要連接18個OSFP接口,32個節點共需要576個連接,對應18臺NVLink Switch。

DGX H100也可以(僅)通過InfiniBand互聯,參考DGX H100 BasePOD的配置,其中的DGX H100系統配置了8個H100、雙路56核第四代英特爾至強可擴展處理器、2TB DDR5內存,搭配了4塊ConnectX-7網卡——其中3塊雙端口卡用于管理和存儲服務,還有一塊4個OSFP口的用于計算網絡。

回到Grace Hopper超級芯片,NVIDIA提供了一個簡化的示意圖其中的Hopper GPU上的18條NVLink4與NVLink Switch相連。NVLink Switch連接了"兩組"Grace Hopper超級芯片。任何GPU都可以通過NVLink-C2C和NVLink Switch訪問網絡內其他CPU、GPU的內存。

NVLink4 Networks的規模是256個GPU,注意是GPU而不是超級芯片,因為NVLink4連接是通過H100 GPU提供的。對于Grace Hopper超級芯片,這個集群的內存上限就是:(480GB內存+96GB顯存)×256節點=147456GB,即144TB的規模。假如NVIDIA推出了GTC2022中提到的Grace + 2Hopper,那么按照NVLink Switch的接入能力,那就是128個Grace和256個Hopper,整個集群的內存容量將下降至約80TB的量級。

Grace Hooper 超級芯片之間的互聯

在COMPUTEX 2023期間,NVIDIA宣布Grace Hopper超級芯片已經量產,并發布了基于此的DGX GH200超級計算機。NVIDIA DGX GH200使用了256組Grace Hopper超級芯片,以及NVLink互聯,整個集群提供高達144TB的可共享的"顯存",以滿足超大模型的需求。以下是一些數字,讓我們感受一下NVIDIA打造的E級超算系統的規模:

算力:1 exa Flops (FP8)

光纖總長度:150英里

風扇數量:2112個(60mm)

風量:7萬立方英尺/分鐘(CFM)

重量:4萬磅

顯存:144TB NVLink

帶寬:230TB/s

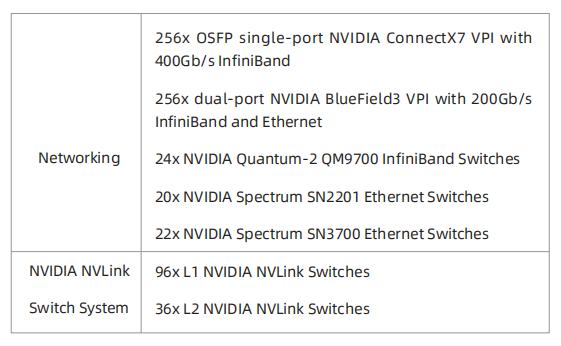

從150英里的光纖長度,我們可以感受到其網絡的復雜性。這個集群的整體網絡資源如下:

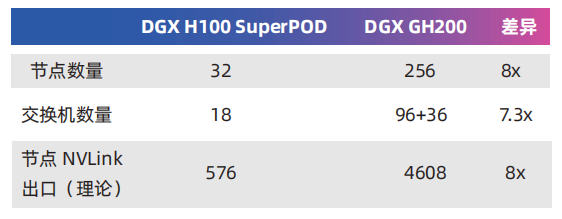

由于Grace Hopper芯片上只有一個CPU和一個GPU,與DGX H100相比GPU的數量要少得多。要達到256個GPU所需的節點數大大增加,這導致NVLink Network的架構變得更加復雜。

NVIDIA DGX GH200 集群內的 NVLink 網絡架構

DGX GH200的每個節點有3組NVLink對外連接,每個NVLink Switch連接8個節點。256個節點總共分為32組,每組8個節點搭配3臺L1 NVLink Switch,共需要使用96臺交換機。這32組網絡還要通過36臺L2 NVLink Switch組織在一起。

與DGX H100 SuperPOD相比GH200的節點數量大幅增加,NVLink Network的復雜度明顯提高了。以下是二者的對比:

三、InfiniBand 擴大規模

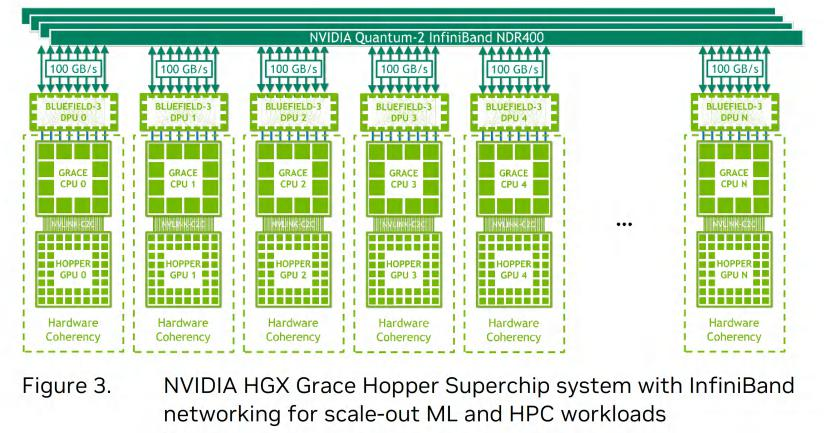

如果需要更大規模(超過256個GPU)的集群就需要引入InfiniBand交換機。對于Grace Hopper超級芯片的大規模集群NVIDIA建議采用Quantum-2交換機組網提供NDR 400 Gb/s端口。每個節點配置BlueField-3 DPU(已集成ConnectX-7),每個DPU提供2個400Gb/s端口,總帶寬達到100GB/s。理論上使用以太網連接也可以達到類似的帶寬水平,但考慮到NVIDIA收購Mellanox,傾向于使用InfiniBand是可以理解的。

NVIDIA BlueField-3 DPU

基于InfiniBand NDR400組織的Grace Hopper超級芯片集群有兩種架構。一種是完全采用InfiniBand連接,另一種是混合配置NVLink Switch和InfiniBand連接。這兩種架構的共同點是每個節點都通過雙端口(總共800Gbps)連接InfiniBand交換機,DPU占用x32的PCIe 5.0并由Grace CPU提供PCIe連接。它們的區別在于后者每個節點還通過GPU接入NVLink Switch連接,形成若干NVLink子集群。

很顯然混合配置InfiniBand和NVLink Switch的方案性能更好,因為部分GPU之間具有更大的帶寬以及對內存的原子操作。例如,NVIDIA計劃打造超級計算機Helios,它將由4個DGX GH200系統組成,并通過Quantum-2 InfiniBand 400 Gb/s網絡組織起來。

四、從 H100 NVL 的角度再看 NVLink

在GTC 2023上,NVIDIA發布了專為大型語言模型部署的NVIDIA H100 NVL。與H100家族的其他兩個版本(SXM和PCIe)相比,它具有兩個特點:首先,H100 NVL相當于將兩張H100 PCIe通過3塊NVLink橋接連接在一起;其次,每張卡都具有接近完整的94GB顯存,甚至比H100 SXM5還要多。

根據NVIDIA官方文檔的介紹H100 PCIe的雙插槽NVLink橋接延續了上一代的A100 PCIe,因此H100 NVL的NVLink互連帶寬為600GB/s仍然比通過PCIe 5.0互連(128GB/s)高出4倍以上。H100 NVL由兩張H100 PCIe卡組合而成,適用于推理應用高速NVLink連接使得顯存容量高達188GB以滿足大型語言模型的(推理)需求。如果將H100 NVL的NVLink互連視為縮水版的NVLink-C2C,這有助于理解NVLink通過算力單元加速內存訪問的原理。

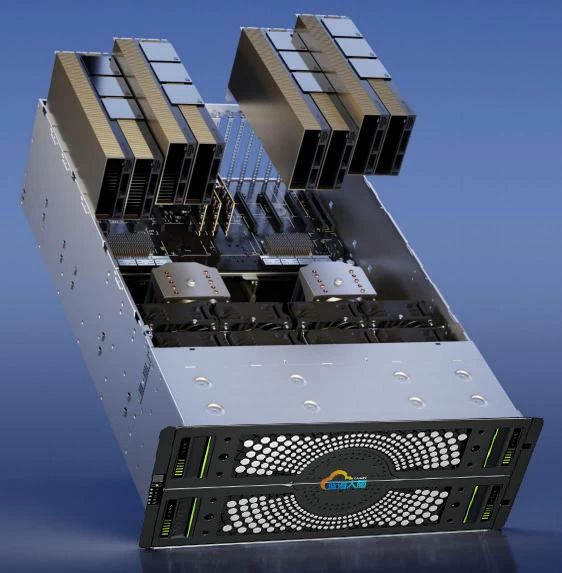

藍海大腦高性能大模型訓練平臺利用工作流體作為中間熱量傳輸的媒介,將熱量由熱區傳遞到遠處再進行冷卻。支持多種硬件加速器,包括CPU、GPU、FPGA和AI等,能夠滿足大規模數據處理和復雜計算任務的需求。采用分布式計算架構,高效地處理大規模數據和復雜計算任務,為深度學習、高性能計算、大模型訓練、大型語言模型(LLM)算法的研究和開發提供強大的算力支持。具有高度的靈活性和可擴展性,能夠根據不同的應用場景和需求進行定制化配置。可以快速部署和管理各種計算任務,提高了計算資源的利用率和效率。

總結

在計算領域,CPU和GPU是兩個關鍵的組件其在處理數據和執行任務時具有不同的特點和復雜性。隨著計算需求的增加,單一的CPU或GPU已經無法滿足高性能計算的要求。因此,多元算力的結合和算存互連、算力互連的重要性日益凸顯。

作為計算機系統的核心,CPU具有高度靈活性和通用性,適用于廣泛的計算任務。它通過復雜的指令集和優化的單線程性能,執行各種指令和處理復雜的邏輯運算。然而隨著計算需求的增加,單一的CPU在并行計算方面的能力有限,無法滿足高性能計算的要求。

GPU最初設計用于圖形渲染和圖像處理,但隨著時間的推移,其計算能力得到了極大的提升,成為了高性能計算的重要組成部分。GPU具有大規模的并行處理單元和高帶寬的內存,能夠同時執行大量的計算任務。然而,GPU的復雜性主要體現在其并行計算架構和專業化的指令集,這使得編程和優化GPU應用程序更具挑戰性。

為了充分利用CPU和GPU的優勢,多元算力的結合變得至關重要。通過將CPU和GPU結合在一起,可以實現任務的并行處理和分工協作。CPU負責處理串行任務和控制流,而GPU則專注于大規模的并行計算。這種多元算力的結合可以提高整體的計算性能和效率,并滿足不同應用場景的需求。

算存互連是指計算單元和存儲單元之間的高速互聯,而算力互連是指計算單元之間的高速互聯。在高性能計算中,數據的傳輸和訪問速度對整體性能至關重要。通過優化算存互連和算力互連,可以減少數據傳輸的延遲和瓶頸,提高計算效率和吞吐量。高效的算存互連和算力互連可以確保數據的快速傳輸和協同計算,從而提高系統的整體性能。

CPU和GPU在計算領域扮演著重要的角色,但單一的CPU或GPU已經無法滿足高性能計算的需求。多元算力的結合、算存互連和算力互連成為了提高計算性能和效率的關鍵。通過充分利用CPU和GPU的優勢,并優化算存互連和算力互連,可以實現更高水平的計算能力和應用性能,推動計算技術的發展和創新。

審核編輯 黃宇

-

cpu

+關注

關注

68文章

10889瀏覽量

212386 -

gpu

+關注

關注

28文章

4760瀏覽量

129131 -

算力

+關注

關注

1文章

1003瀏覽量

14882 -

大模型

+關注

關注

2文章

2503瀏覽量

2919

發布評論請先 登錄

相關推薦

CPU、GPU與算存互連的復雜比較與重要性分析

CPU、GPU與算存互連的復雜比較與重要性分析

評論