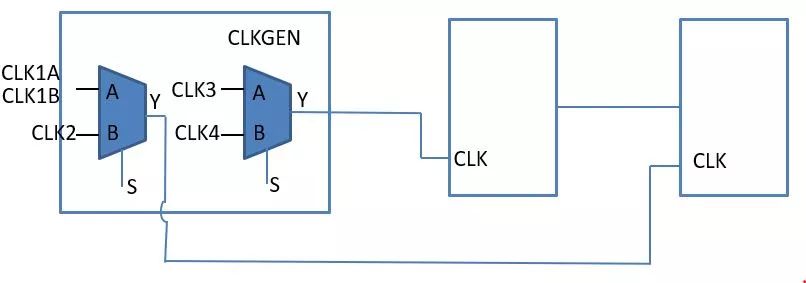

Clock定義指令

Clock分為兩大類(lèi),一類(lèi)是root clock,其定義指令是 create_clock ;另外一類(lèi)是generated clock,其定義指令是 create_generated_clock 。在做設(shè)計(jì)約束時(shí),如何選擇合適的約束指令和指令option是非常關(guān)鍵的,這將直接影響到工具的行為,如果選擇有誤,將會(huì)讓工具的行為不符合自己的預(yù)期。

create_clock ** option淺析**

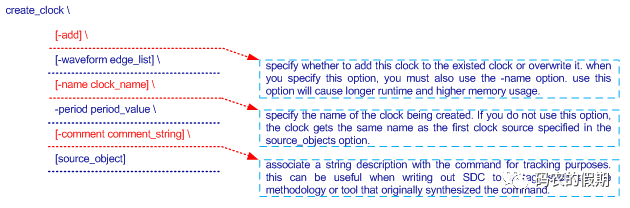

圖1 create_clock介紹

如圖1中所示,列出了create_clock的所有option以及其詳細(xì)的解釋。在這些當(dāng)中加“[]”的為可選項(xiàng),其它的為必選項(xiàng)。其中比較關(guān)鍵的-add,推薦大家最好是都要加上,防止PAD/port共用,造成clock被覆蓋;-name,推薦大家一定要加上,杜絕系統(tǒng)自動(dòng)分配命名。

create_generated_clock option淺析

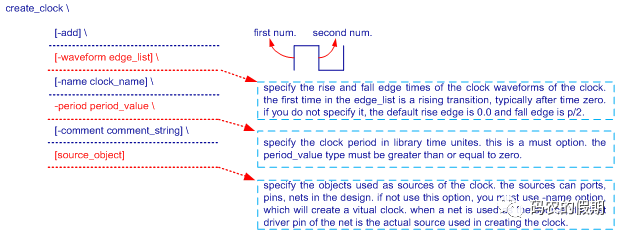

圖2 create_generated_clock options

如圖2所示,列出了create_generated_clock的所有option以及詳細(xì)解釋?zhuān)┐蠹覅⒖肌T谶@些當(dāng)中,用“}”包起來(lái)的可以看做是一組參數(shù),有類(lèi)似的功能。接下來(lái),重點(diǎn)跟大家探討下create_generated_clock中的一些option的使用區(qū)別。

multiply_by/duty_cycle詳解

首先說(shuō)下multiply_by選項(xiàng),其意思是倍頻多少,主要應(yīng)用在PLL的倍頻clock的輸出點(diǎn)的clock的定義,如果其master clock的duty cycle不是50%,然而,經(jīng)過(guò)PLL之后,duty cycle往往都是設(shè)計(jì)成50%輸出,所以可以配合-duty_cycle選項(xiàng)改變定義的clock的duty cycle。

divide_by/edges詳解

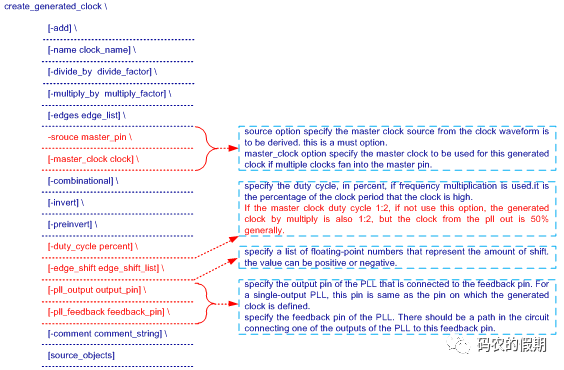

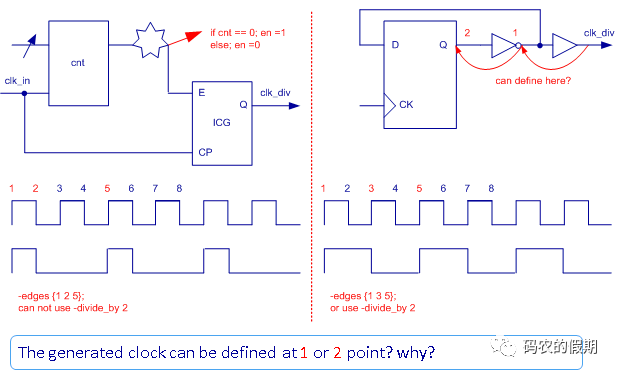

divider_by表示除頻的意思,例如最常見(jiàn)的2分頻電路可以用-divide_by 2定義,如圖3右中波形所示。但是有時(shí),design設(shè)計(jì)的divider可能是采用ICG抹掉時(shí)鐘邊沿的方式實(shí)現(xiàn)的,如圖3左所示。這時(shí)經(jīng)過(guò)divider之后出來(lái)的波形并不是標(biāo)準(zhǔn)的2分頻波形,這時(shí)候就不能直接采用-divider_by 2的方式定義分頻之后的clock,因?yàn)槿绻捎昧薲ivide_by的方式定義了,那么其工具認(rèn)知的行為波形,跟design實(shí)際輸出的波形是不符的,如果分頻后的時(shí)鐘,應(yīng)用在falling edge觸發(fā)的DFF當(dāng)中,可能就會(huì)造成工具timing check錯(cuò)誤。(此處不詳細(xì)解釋了,大家可自己畫(huà)波形思考)

圖3 divide_by/edges options

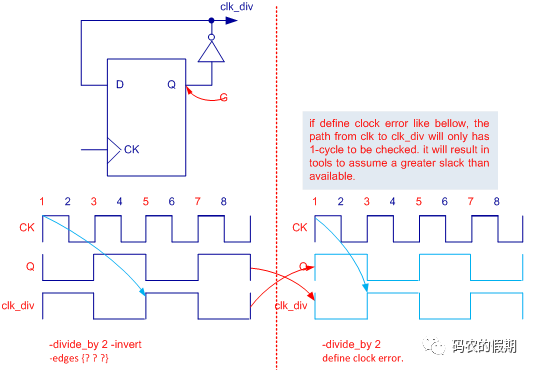

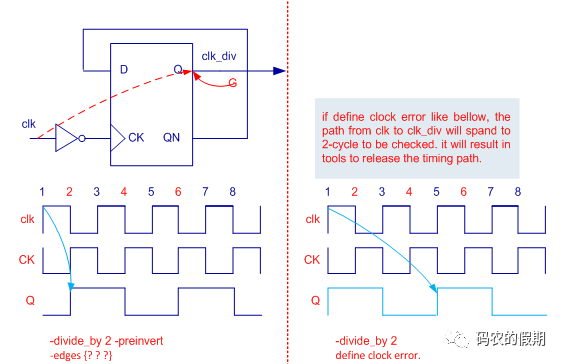

invert/preinvt/edge_shift詳解

-invert/preinvert分別表示:先定義clock后clock取反還是先clock取反后定義clock。我通過(guò)兩個(gè)例子跟大家解釋一下。如圖4所示,將剛才圖3右中clock的定義點(diǎn)修改到register的Q-pin上,如果繼續(xù)使用-divide_by 2的方式定義此clock,那么工具認(rèn)為的DFF/Q的波形應(yīng)該是圖4右所示的。但是實(shí)際上,分析可以知道,design輸出的clock波形應(yīng)該是圖4左所示的波形。

工具在做setup timing分析時(shí),是從launch DFF的觸發(fā)沿到capture DFF的下一個(gè)觸發(fā)沿之間的時(shí)間,所以基于錯(cuò)誤的clock定義之后,工具的timing check行為將變成圖4右藍(lán)色箭頭所示的行為。但是實(shí)際design預(yù)期的行為應(yīng)該是圖4左藍(lán)色箭頭的行為。從圖中對(duì)比可以看出,工具timing check與designer預(yù)期不符。如果要正確的在DFF/Q pin上定義clock,應(yīng)該加上-invert選項(xiàng)(即-divide_by 2 -invert)。

圖4 invert option示例

雖然在圖4示例中,工具的行為跟designer預(yù)期不符,但是分析可知,此時(shí)是加緊了工具的行為,即變得悲觀了,可能結(jié)果是浪費(fèi)一些PPA,但是不至于design最終行為出錯(cuò)。但是如果出現(xiàn)如圖5所示的情況就不一樣了。如果是按照?qǐng)D5所示的分頻設(shè)計(jì),我們同樣在DFF/Q pin上定義2分頻的clock,同樣僅使用-divide_by 2的方式,那么定義完之后,工具認(rèn)為的clock波形是如圖5右所示的情況,而design實(shí)際的波形應(yīng)該是圖5左所示的情況。這時(shí)工具如果繼續(xù)按照?qǐng)D5右藍(lán)色箭頭去做setup timing check,很明顯是放松了對(duì)整個(gè)design的行為約束,這樣導(dǎo)致的后果將是,最終timing收斂完成之后,行為跟實(shí)際design的行為不符,完全沒(méi)有達(dá)到預(yù)期的timing約束程度,導(dǎo)致整個(gè)design失敗。如果design如圖5中所示,我們想在DFF/Q pin上正確的定義clock,需要加上-preinvert選項(xiàng)(-divide_by 2 -preinvert)。

圖5 preinvert option示例

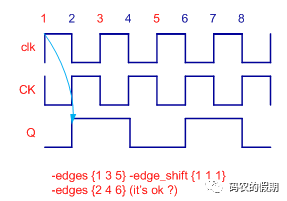

在圖4,圖5中的clock定義,上面講到的都是如果采用-divide_by的方式如何正確的定義,那么能不能采用-edge的方式來(lái)定義呢?以圖5為例,可以替換成-edge并且配合-edge_shift的方式來(lái)定義,其定義方式如圖6所示。但是,此處需要注意,-edge_shift,其后面list列表中的數(shù)目要跟-edge中l(wèi)ist數(shù)目完全一致,并且,-edge_shift后面list中的number可以為正,可以為負(fù),如果為正,則表示右移,為負(fù)則表示左移,其是float類(lèi)型的,表示右移/左移多少個(gè)時(shí)間單位。

圖6 edge_shift option示例

圖6中的定義,那么能不能直接用-edges {2 4 6}的方式呢?以及圖4中的示例,能不能替換為-edges的方式定義呢?可以自己思考一下。

敲黑板,劃重點(diǎn)

在此可以跟大家分享兩條基本原則,有助于分析clock定義是否合理。采用create_generated_clock定義的clock,其一:繼承的mater clock的edge一定要正確;其二:跟master clock之間的實(shí)際通路一定要物理上存在,并且要通。總結(jié)起來(lái)就是,clock定義要按照實(shí)際design來(lái)定義,不能想當(dāng)然,如果在不清楚如何使用option時(shí),可以先手畫(huà)波形圖,然后按照?qǐng)D再去選擇option的使用。

-

分頻器

+關(guān)注

關(guān)注

43文章

447瀏覽量

49997 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2000瀏覽量

61227 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6431 -

dff

+關(guān)注

關(guān)注

0文章

26瀏覽量

3424

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Stm32_Clock_Init函數(shù)如何定義

介紹一下STM32L151的clock tree

基于Stm32_Clock_Init()函數(shù)的流水燈設(shè)計(jì)

什么是Clock Tree

探討一下深度學(xué)習(xí)在嵌入式設(shè)備上的應(yīng)用

請(qǐng)教一下各位標(biāo)準(zhǔn)單元庫(kù)中clock buffer的設(shè)計(jì)很復(fù)雜嗎

探討軟件定義未來(lái)醫(yī)療的新藍(lán)圖

DC/DC評(píng)估篇 損耗探討-定義和發(fā)熱

深入探討軟件定義架構(gòu)及其意義

怎樣通過(guò)設(shè)置clock group來(lái)確認(rèn)各個(gè)時(shí)鐘之間的關(guān)系?

時(shí)序分析基本概念介紹<generate clock>

探討下clock的基本定義(上)

探討下clock的基本定義(上)

評(píng)論