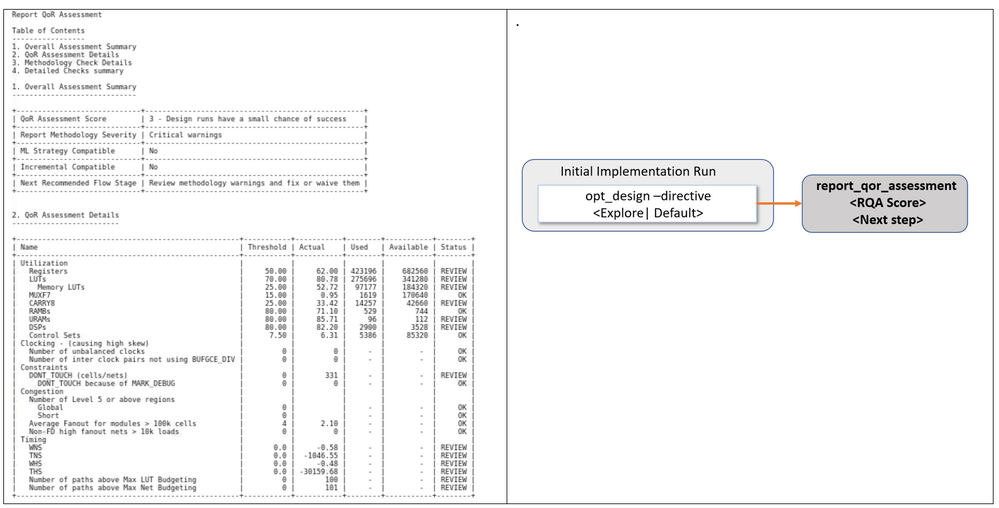

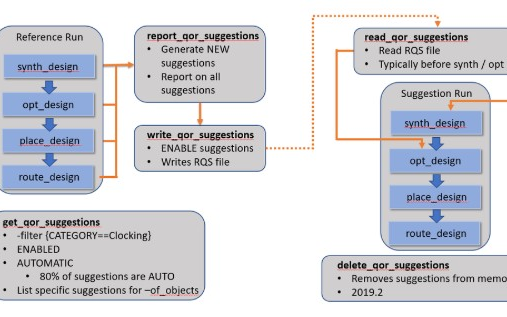

在先前博文在 Vivado 中利用 report_qor_suggestions 提升 QoR和利用 RQA 和 RQS 實現設計收斂中,我們了解了“Report QOR Suggestions (RQS)”(QoR 建議報告)如何借助時鐘設置、使用率、擁塞和時序建議來幫助達成設計收斂。

在本篇博文中,我們來聊聊“RQS_CLOCK-12”時鐘設置建議以及它如何幫助達成時序收斂。

要求:

掌握如何生成和應用report_qor_suggestions

基本掌握 CLOCK_LOW_FANOUT 約束。

RQS_CLOCK-12:

RQS_CLOCK-12 建議屬于專為 UltraScale 和 UltraScale+ 器件生成的自動增量式友好建議。

它使用“CLOCK_LOW_FANOUT”屬性,并將該屬性分配給時鐘信號線或者一組寄存器,由全局時鐘緩沖器根據其負載數目來驅動。

1. 將該屬性應用于時鐘信號線時,全局時鐘緩沖器的負載將被約束并放置到單個時鐘區域內。

2. 將該屬性應用于一組寄存器時,在 opt_design 期間創建的現有全局時鐘緩沖器的基礎上,還會并行復制一個全新的全局時鐘緩沖器。新全局時鐘緩沖器的負載僅適用于該屬性應用到的各組寄存器,并約束到單個時鐘區域。

現在我們來看看 RQS_CLOCK-12 建議如何應用 CLOCK_LOW_FANOUT 來降低時鐘偏差,進而幫助設計達成時序收斂。

假設已布線的設計中存在如下兩個場景,其中存在錯誤的時鐘偏差,導致從寄存器到全局緩沖器的控制管腳 (CE/CLR) 的路徑上存在時序違例。

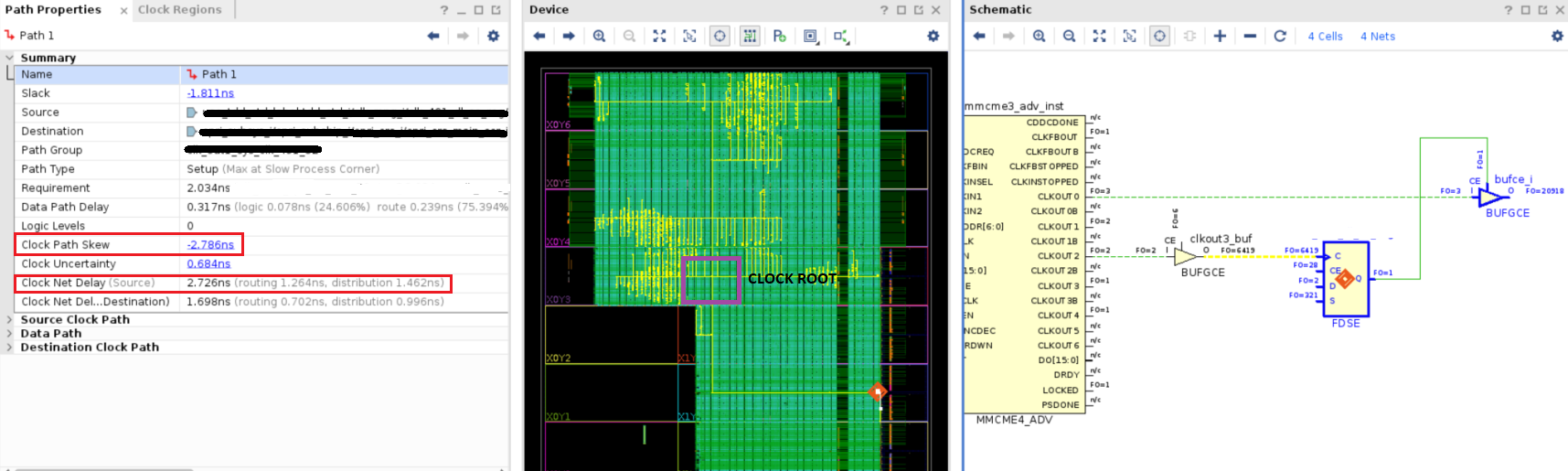

場景 1:

在這條時序收斂失敗的路徑中,時鐘緩沖器 BUFGCE1 (clockout3_buf)、寄存器及其驅動程序 BUFGCE2 (bufce_i) 全都布局在同一個時鐘區域內。驅動寄存器的 BUFGCE1 存在高扇出 (6419),且負載導致其時鐘信號線遍布整個器件,如圖高亮所示。

該工具所選的 CLOCK_ROOT 位置遠離驅動它的全局時鐘緩沖器,導致時鐘信號線延遲過高且時鐘偏差過高。

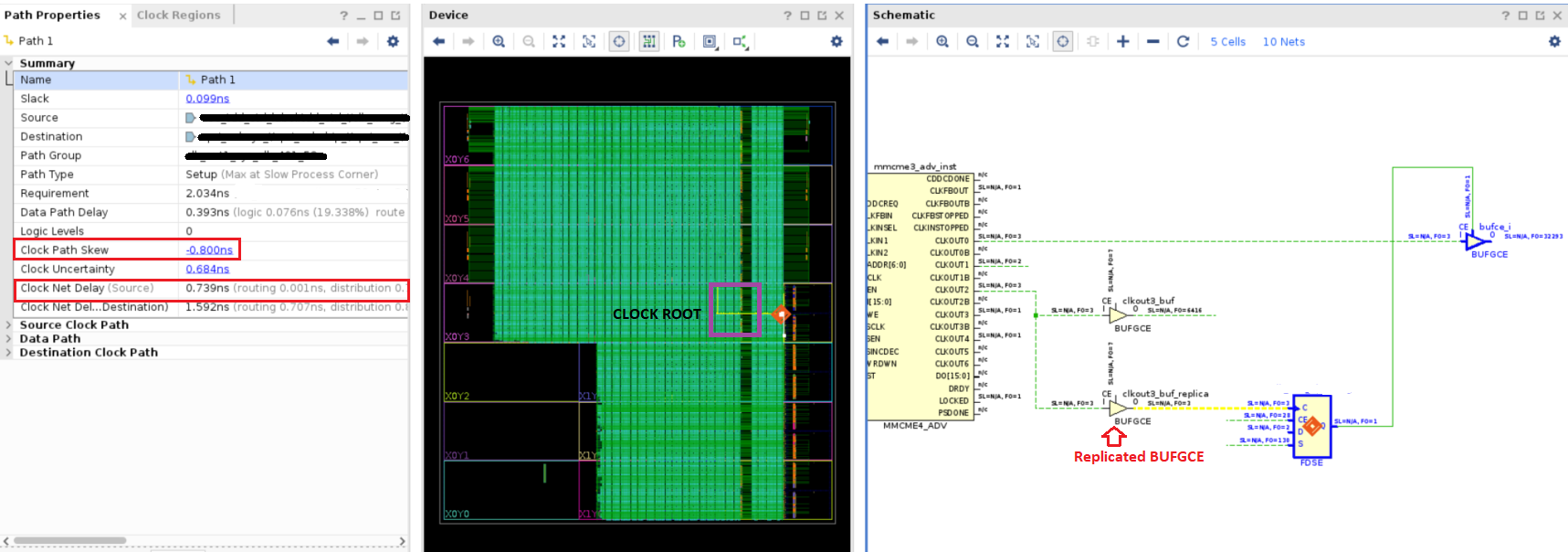

場景 1 的解決辦法:

對寄存器應用 CLOCK_LOW_FANOUT,這樣即可復制 opt_design 期間創建的原始 BUFGCE1 以創建新的 BUFGCE (clkout3_buf_replica),且僅將其用于驅動此關鍵寄存器。這樣將把信號線約束到單個時鐘區域內,從而減少時鐘信號線延遲。

并且,由于時鐘源和負載都位于相同時鐘區域內,CLOCK_LOW_FANOUT 會強制將 clock root(時鐘根)包含在相同時鐘區域內,從而幫助降低時鐘偏差。

對關鍵寄存器應用 CLOCK_LOW_FANOUT 后的板級原理圖:

在 opt_design 的 BUFG 最優化階段,在為 CLOCK_LOW_FANOUT 屬性創建的全局時鐘緩沖器上應該會顯示一條消息。

例如:

INFO: [Opt 31-1077] Phase BUFG optimization inserted 1 global clock buffer(s) for CLOCK_LOW_FANOUT.

語法:

set_property CLOCK_LOW_FANOUT TRUE [get_cells ]

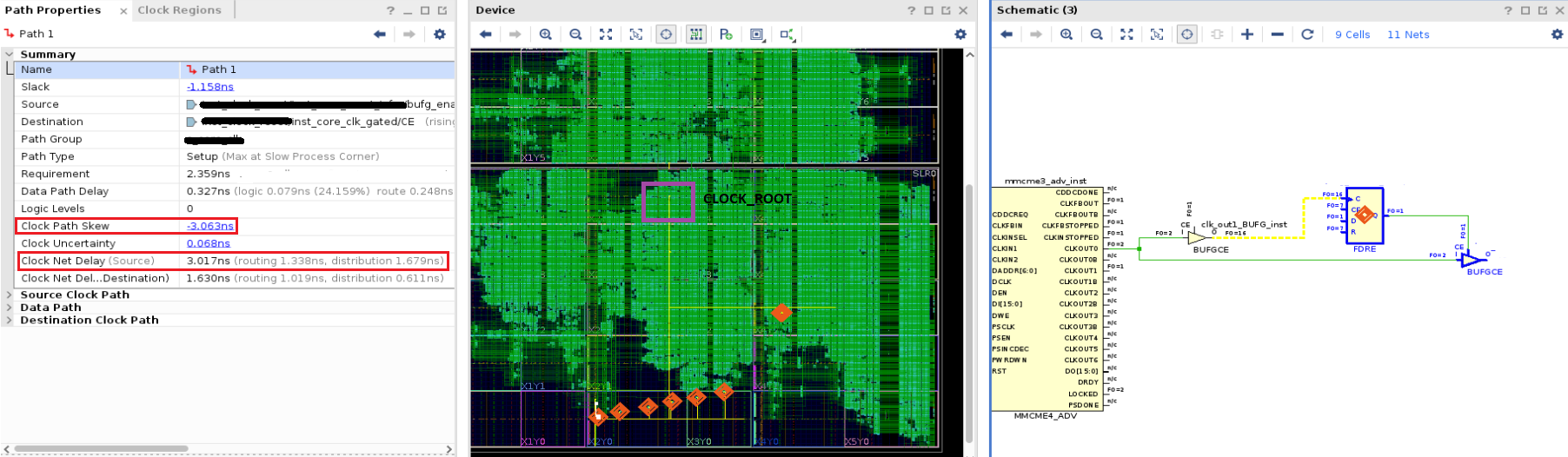

場景 2:

在這條時序收斂失敗的路徑中,時鐘緩沖器 BUFGCE1 (clkout1_BUFG_inst)、寄存器及其驅動程序 BUFGCE2 同樣全都布局在同一個時鐘區域內。BUFGCE1 驅動寄存器的扇出較低 (16),但負載分布于多個時鐘區域(以紅色標記)。由此導致該工具所選的 CLOCK_ROOT 不同于驅動它的全局時鐘緩沖器,進而導致時鐘信號線延遲過高且時鐘偏差過高。

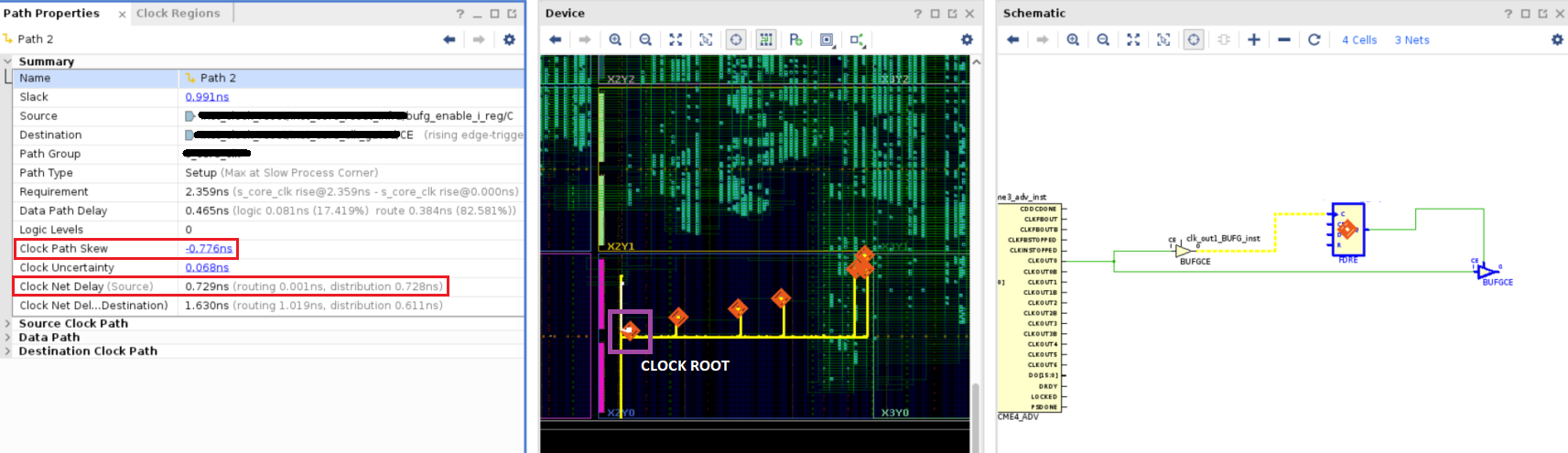

場景 2 的解決辦法:

當 BUFGCE1 扇出較低 (

現在,時鐘源和負載都位于相同時鐘區域內,因此 CLOCK_LOW_FANOUT 會強制將 clock root 包含在相同時鐘區域內,從而幫助降低時鐘偏差。

對時鐘信號線應用 CLOCK_LOW_FANOUT 后的板級原理圖:

語法:

set_property CLOCK_LOW_FANOUT TRUE [get_nets ]

總結

在本篇博文中,我們學習了 2 個設計示例,其中演示了如何生成 RQS_CLOCK-12 建議以將 CLOCK_LOW_FANOUT 屬性應用于由全局時鐘緩沖器直接驅動的寄存器或時鐘信號線。

-

寄存器

+關注

關注

31文章

5355瀏覽量

120531 -

緩沖器

+關注

關注

6文章

1922瀏覽量

45514 -

時序

+關注

關注

5文章

389瀏覽量

37349

發布評論請先 登錄

相關推薦

如何在實現流程中將RQA與RQS結合使用的設計示例

UltraFast設計方法時序收斂快捷參考指南

EM模型仿真中的收斂誤差

單點無法收斂后繼續HB掃描

如何進行時序收斂,即如何確保生成的內核工作在2.5GHz

美國banner邦納Q60VR3AF2000

HarmonyOS實戰——Clock組件基本使用

MCU ID的相關資料推薦

Report QoR Suggestions助力解決Vivado設計問題

AD9517-3: 12-Output Clock Generator with Integrated 2.0 GHz VCO Data Sheet

單片機 STC11L02E-35I - 讀取 MCU ID,然后通過串口發送

在Vivado中利用Report QoR Suggestions提升QoR

Linux clock子系統是什么

RQS設計收斂建議ID RQS_CLOCK-12

RQS設計收斂建議ID RQS_CLOCK-12

評論