中斷優先級

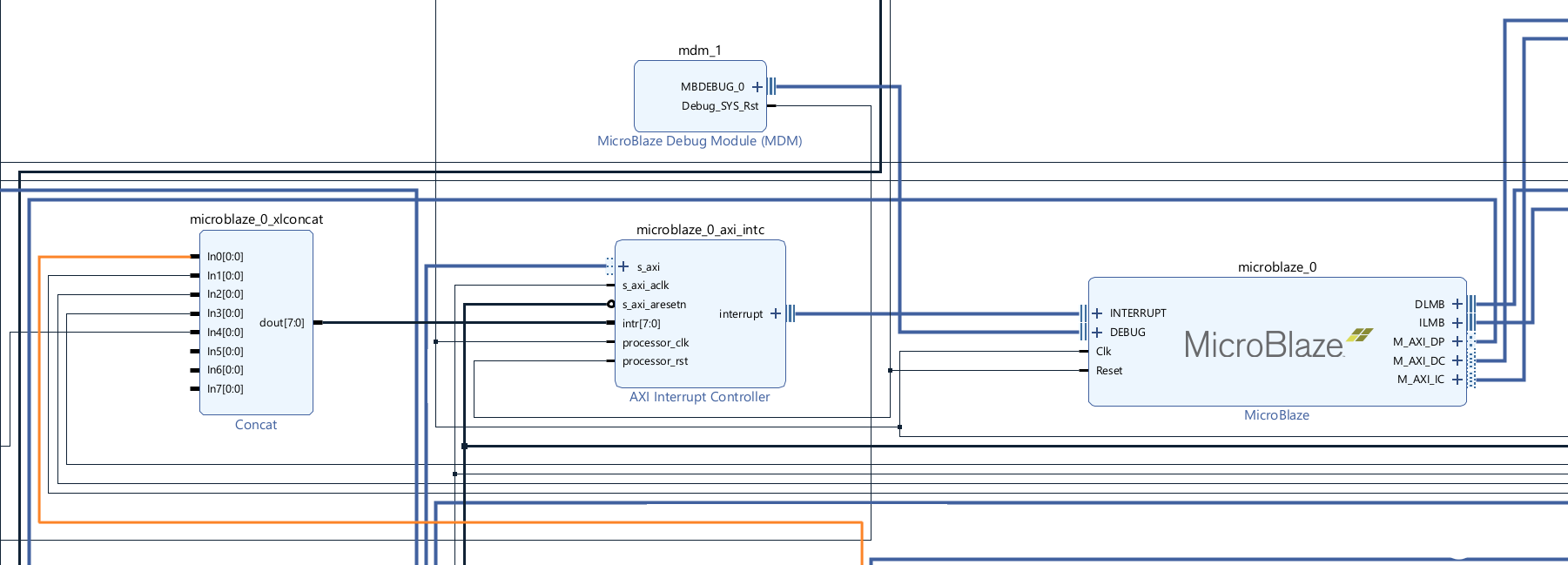

AXI Interrupt Controller支持中斷優先級。 在Vivado Block Design中, bit-0連接的中斷優先級最高, 越靠近bit-0的中斷優先級最高。

AXI Interrupt Controller的手冊pg099中的描述如下:

Priority between interrupt requests is determined by vector position. The least significant bit (LSB, in this case bit 0) has the highest priority.

Intr(0) is always the highest priority interrupt and each successive bit to the left has a corresponding lower interrupt priority.

中斷嵌套

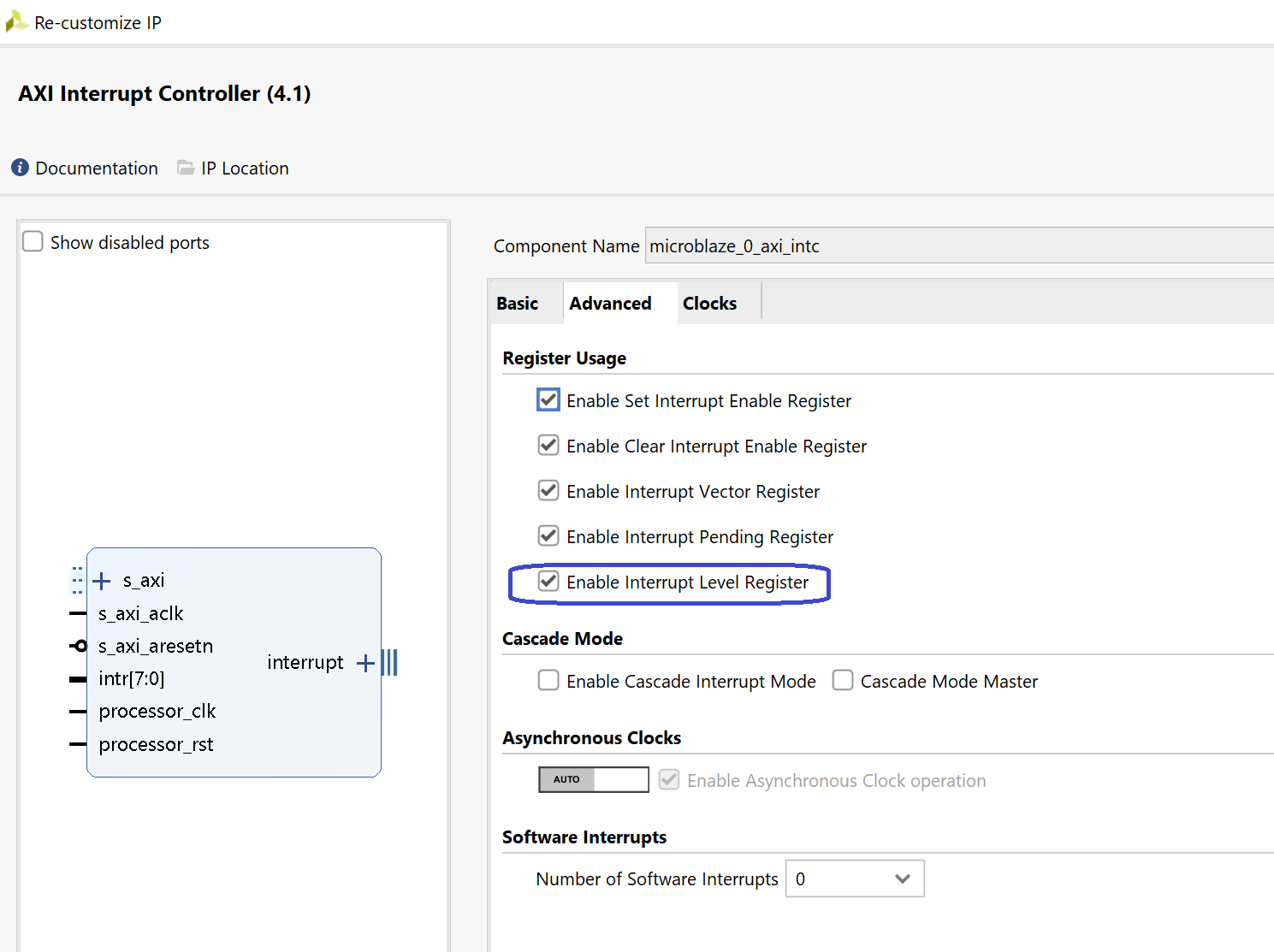

要使用中斷優先級,通常也要使能中斷嵌套(Nested Interrupts)。在Vivado Block Design中, 配置AXI Interrupt Controller時,在“advanced”選項中,要選擇“Interrupt Level Register” 。

AXI Interrupt Controller的手冊pg099中的描述如下:

Nested Interrupts

The core provides support for nested interrupts, by implementing an Interrupt Level

Register. This can be used by software to prevent lower priority interrupts from occurring

when handling an interrupt, thus allowing interrupts to be enabled during interrupt

handling to immediately take a higher priority interrupt. Software must save and restore

the Interrupt Level Register and return address.

Because the processor jumps directly to the unique Interrupt vector address to service a

particular interrupt when using fast interrupt mode, the user interrupt service routine code itself must save and restore the Interrupt Level Register and Return Address in this case. In

normal interrupt mode, this is handled by the software driver.

選擇“Interrupt Level Register” 后,中斷處理代碼會保存和恢復r14,并且在進入設備的ISR之前會使能中斷。 具體代碼請查看XIntc_DeviceInterruptHandler( )。

Xintc.h中的說明如下:

For nested interrupts, XIntc_DeviceInterruptHandler saves

microblaze r14 register on entry and restores on exit. This is

required since compiler does not support nesting. It enables

Microblaze interrupts after blocking further interrupts from

the current interrupt number and interrupts below current

interrupt priority by writing to Interrupt Level Register of

INTC on entry. On exit, it disables microblaze interrupts and

restores ILR register default value(0xFFFFFFFF)back. It is

recommended to increase STACK_SIZE in linker script for nested

interrupts.

本文轉載自:博客園

審核編輯:湯梓紅

-

amd

+關注

關注

25文章

5469瀏覽量

134192 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121467 -

中斷

+關注

關注

5文章

898瀏覽量

41513 -

AXI

+關注

關注

1文章

127瀏覽量

16631

發布評論請先 登錄

相關推薦

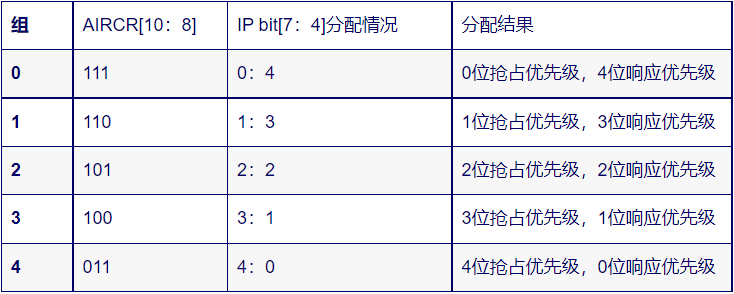

stm32的中斷優先級基本原理介紹

STM32中斷使用NVIC中斷優先級管理

2.FreeRTOS中斷優先級和任務優先級

AMD Xilinx AXI Interrupt Controller中斷優先級

AMD Xilinx AXI Interrupt Controller中斷優先級

評論