本應(yīng)用筆記介紹了使用外部微處理器參考振蕩器(RO) 的 TH7122x收發(fā)器。它提出了一個基于皮爾斯拓撲的典型微處理器時鐘振蕩器和參考信號所需的典型電平。

TH7122x 具有可編程 R 和 N 分頻器,并且芯片不提供任何數(shù)據(jù)同步或時鐘恢復(fù)信號。因此,只有它們的范圍限制了分頻器的設(shè)置、信道間隔的頻率考慮和最大參考頻率。EVB7122x評估板通常使用 7.1505 MHz晶振作為參考振蕩器,因為這是使用 R 和 N 計數(shù)器的整數(shù)值在發(fā)射和接收中調(diào)諧 315、433.92、868.3 和 915 MHz 的良好折衷方案。這使它具有獨特的功能,即可以通過板上的跳線設(shè)置這些頻率。

在使用內(nèi)部參考振蕩器的可編程模式下,參考頻率可以從 3 MHz 到 12 MHz。由于 R 計數(shù)器的范圍是 4 到 1023,因此頻率必須具有以下限制:

4leq 壓裂{f_ {RO}}{f_ {R}}leq 1023

其中 fR 是通道間隔或參考頻率,fRO 是晶體振蕩器的頻率。另外,請記住 VCO 的頻率可以表示為:

f_ {VCO}=Ncdot f_ {R} = N cdot frac{f_ {RO}}{R}

如果向 RO 輸入(引腳 10)提供外部參考,則頻率范圍為 1 MHz 至 16 MHz。這完全屬于幾乎所有微處理器參考的范圍,因此微處理器和 TH7122x 可以使用相同的晶體。在許多應(yīng)用中,這可以顯著節(jié)省成本。晶體容差必須適合收發(fā)器應(yīng)用的頻率要求,這一點很重要。如果在 ASK 模式下使用,容差通常并不重要,在大多數(shù)情況下,50 ppm 或 100 ppm 的晶體應(yīng)該足夠了。但是,對于 FSK 操作,中心頻率通常必須在中心頻率的 10 kHz 至 20 kHz 范圍內(nèi),因此容差應(yīng)至少為 20 ppm。大多數(shù)標(biāo)準(zhǔn)微處理器晶體規(guī)定為 50 ppm。

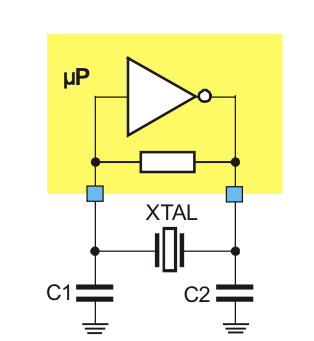

基于皮爾斯拓撲的典型微處理器時鐘振蕩器如圖 1 所示:

反相器的輸出從地擺動到 VCC,輸入通常也是如此。可以將 TH7122x 的 RO 引腳直接連接到振蕩器輸出,但電平遠高于收發(fā)器要求的電平,如果它們在PCB上相距一定距離,高電平時鐘信號可能會輻射諧波或耦合時鐘信號進入附近的走線。

向 TH7122x 提供參考信號的一種簡單方法是使用圖 2 中的電路:

C2/C3 分壓器為 TH7122x 的引腳 10 提供交流耦合,并被選擇以提供所需的電平。C1、C2 和 C3 的串聯(lián)組合決定了晶體上的負載。

當(dāng) TH7122x 與外部參考一起使用時,B 字中的ROMIN 和 ROMAX電流設(shè)置應(yīng)設(shè)置為 0。這將關(guān)閉參考振蕩器幅度調(diào)節(jié)。

審核編輯:湯梓紅

-

mcu

+關(guān)注

關(guān)注

146文章

17149瀏覽量

351216 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3428瀏覽量

106004 -

振蕩器

+關(guān)注

關(guān)注

28文章

3832瀏覽量

139096 -

分頻器

+關(guān)注

關(guān)注

43文章

447瀏覽量

49913

發(fā)布評論請先 登錄

相關(guān)推薦

使用的TH7122和TH71221收發(fā)器的窄帶FSK應(yīng)用分析

基于TH7122和TH71221集成電路的高速數(shù)據(jù)通信技術(shù)

振蕩器基礎(chǔ)知識

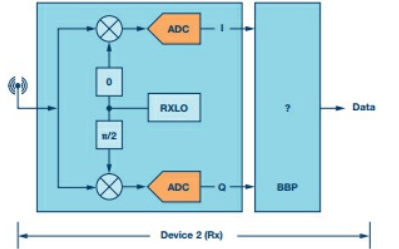

什么是用于RF收發(fā)器的簡單基帶處理器?

用于Zynq 7000 GTX收發(fā)器的LVDS振蕩器指定電壓擺幅是多少?

STM32的外部振蕩器 精選資料分享

微處理器的外部結(jié)構(gòu)是怎樣構(gòu)成的

微處理器監(jiān)控電路和RS-232收發(fā)器交叉選型表

基于RF收發(fā)器的基帶處理器

如何使用RF收發(fā)器實現(xiàn)簡單的基帶處理器

淺談微處理器的發(fā)展歷程

使用經(jīng)濟振蕩器為8051微處理器提供時鐘

淺談外部微處理器參考振蕩器(RO)的TH7122x收發(fā)器

淺談外部微處理器參考振蕩器(RO)的TH7122x收發(fā)器

評論