既然RTL是以寄存器行為為基礎,那么就必須先了解寄存器是什么,并且掌握使用寄存器做設計需要注意的事項。

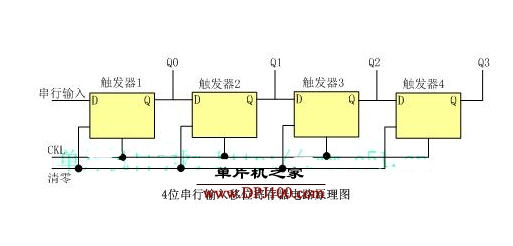

寄存器從字面看,就是一個容器,將可能隨時發生變化的數據存起來,確保變化不會影響到保存的數據。這個行為與“數字電路設計”中提到的D觸發器行為一致,一般來說由輸入數據信號D、輸出數據信號Q以及邊沿觸發信號CLK組成。其實就是D觸發器(D Flip-Flop,簡稱DFF)。

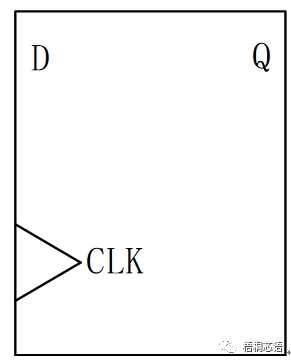

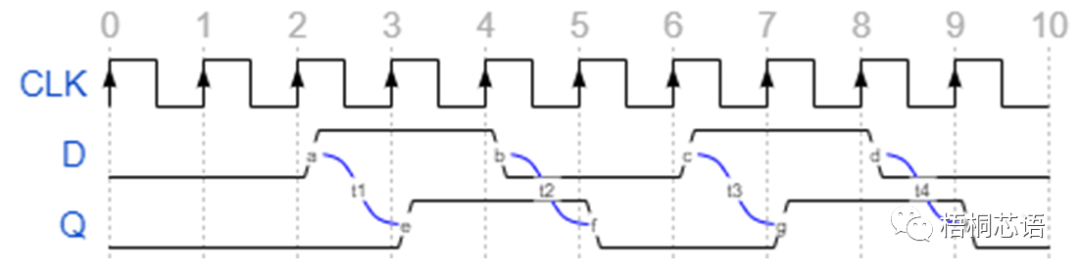

下圖所示是一個上升沿觸發寄存器常見的電路元件圖形,其中CLK輸入有個箭頭的形狀,表示邊沿觸發。其工作行為,由時序圖所示,當CLK上升沿觸發電路狀態的變化,則D端輸入的信號被采集并輸出到Q端。如果沒有CLK上升沿觸發電路,則輸出信號Q保持不變。以波形圖t1變化為例,第2個CLK上升沿后,D端數據發生變化,但變化并不會直接傳輸到Q的輸出上,而必須等到第3個CLK上升沿,D端的變化才會被更新到Q的輸出。

常用的寄存器類型

實際在設計電路時,寄存器主要有以下幾種類型:

- 上升沿觸發寄存器

- 下降沿觸發寄存器

- 帶異步復位(高電平有效)的上升沿觸發寄存器

- 帶異步置位(高電平有效)的上升沿觸發寄存器

- 帶異步復位(高電平有效)的下降沿觸發寄存器

- 帶異步置位(高電平有效)的下降沿觸發寄存器

- 帶異步復位(低電平有效)的上升沿觸發寄存器

- 帶異步置位(低電平有效)的上升沿觸發寄存器

- 帶異步復位(低電平有效)的下降沿觸發寄存器

- 帶異步置位(低電平有效)的下降沿觸發寄存器。

雖然寄存器種類很多,而且多數一般的標準單元庫[1]都會涵蓋這些寄存器類型。但考慮到電路的可靠性,以及可測試性設計(參考可測試性設計部分)的需要, 建議在設計電路時只使用帶異步復位或異步置位(低電平有效)的上升沿觸發寄存器 。

所謂異步復位或異步置位,就是當該信號有效時,Q端輸出立刻輸出為低電平或高電平,而不用邊沿信號驅動。

-

寄存器

+關注

關注

31文章

5343瀏覽量

120368 -

RTL

+關注

關注

1文章

385瀏覽量

59785 -

D觸發器

+關注

關注

3文章

164瀏覽量

47915 -

異步復位

+關注

關注

0文章

47瀏覽量

13314 -

CLK

+關注

關注

0文章

127瀏覽量

17171

發布評論請先 登錄

相關推薦

寄存器變量

移位寄存器的原理

GPIO寄存器

寄存器是什么 掌握使用寄存器做設計需要注意的事項

寄存器是什么 掌握使用寄存器做設計需要注意的事項

評論