狀態機往往是FPGA 開發的主力。選擇合適的架構和實現方法將確保您獲得一款最佳解決方案。

FPGA 常常用于執行基于序列和控制的行動, 比如實現一個簡單的通信協議。對于設計人員來說,滿足這些行動和序列要求的最佳方法則是使用狀態機。狀態機是在數量有限的狀態之間進行轉換的邏輯結構。一個狀態機在某個特定的時間點只處于一種狀態。但在一系列觸發器的觸發下,將在不同狀態間進行轉換。理論上講,狀態機可以分為Moore 狀態機和Mealy 狀態機兩大類。它們之間的差異僅在于如何生成狀態機的輸出。Moore 狀態機的輸出僅為當前狀態的函數。典型的例子就是計數器。而Mealy 狀態機的輸出是當前狀態和輸入的函數。典型的例子就是Richards 控制器.

定義狀態機

當需要定義一個狀態機時,首先要繪制一張狀態圖。狀態圖可用來顯示狀態、狀態間的轉換和狀態機的輸出。圖1 顯示了Moore 狀態機的狀態圖(左)和Mealy 狀態機的狀態圖(右)。

如果您要在物理組件中實現這些狀態圖(工程師在FPGA問世之前就是這么做的),首先就得生成當前狀態和后續狀態表,然后生成實現狀態機所需的邏輯。不過由于我們將使用FPGA來實現設計,因此我們可以直接從狀態轉換圖開始工作。

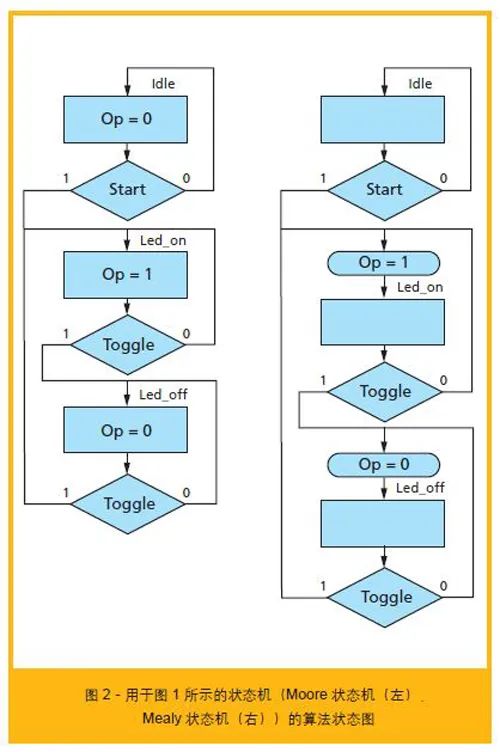

算法狀態圖

雖然有許多狀態機是使用圖1 所示的狀態圖方法進行設計的,但另外還有一種描述狀態機行為的方法,這就是算法狀態圖法。ASM 圖(圖2)在外觀上更加接近軟件工程流程圖。它由三個基本部分構成:

1. 狀態框。它與狀態名稱有關,并包含Moore 狀態輸出列表。

2. 決策框。如果檢驗某條件為真,則進行下一狀態的判斷。

3. 條件輸出框。讓狀態機根據當前狀態和輸入描述Mealy輸出。

一些工程師認為,如果使用VHDL 等硬件描述語言,則采用ASM 格式進行描述的狀態機更易于映射到實現方案中。

MOORE 和MEALY:應該選擇哪個?

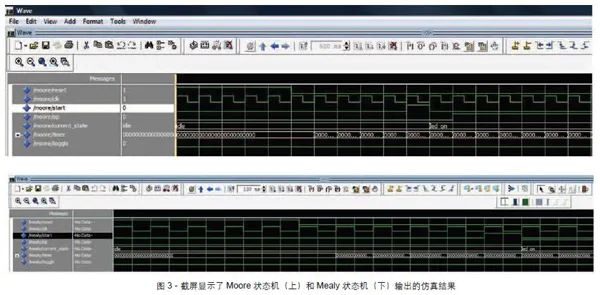

實現Moore 狀態機還是Mealy 狀態機,取決于狀態機需要實現的功能,以及特定的反應次數要求。兩種狀態機之間的最大差別在于狀態機如何對輸入做出反應。在輸入和設置的適當輸出之間,Moore 狀態機一般有一個時鐘周期的延遲。這就意味著Moore 狀態機無法對輸入變化立即做出反應,這點在圖3中可以清楚地看到。而Mealy 狀態機則能夠立即對輸入做出反應,這通常意味著:實現相同的函數,Mealy 狀態機比Moore狀態機需要更少的狀態。Mealy 狀態機的不足之處就是在與另一個狀態機進行通信時,如果輸出出乎意料地嚴重依賴于其它事件的序列或時序,就可能會發生紊亂情況。

當然,并非只能使用單純的Moore狀態機或Mealy 狀態機,也可以將這兩種狀態機混合使用,從而更有效地實現所需的函數。比如說,用于接收RS232 串行數據的狀態機就可以是混合機。

實現狀態機

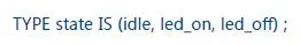

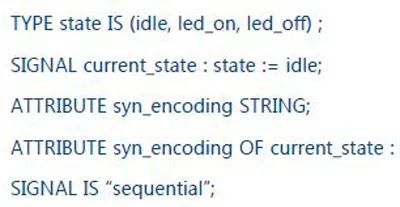

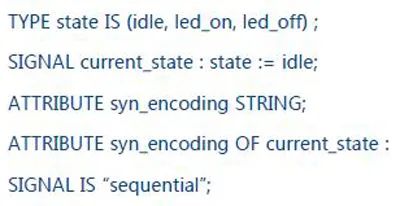

使用VHDL 這樣的高級語言,可以輕松地直接從狀態圖實現狀態機。VHDL 支持多種枚舉類型,方便您定義實際的狀態名稱。舉例如下:

上面的類型定義對應的是圖1 中所示的狀態圖,即用于在按下按鈕時切換發光二極管開/ 關的狀態機。

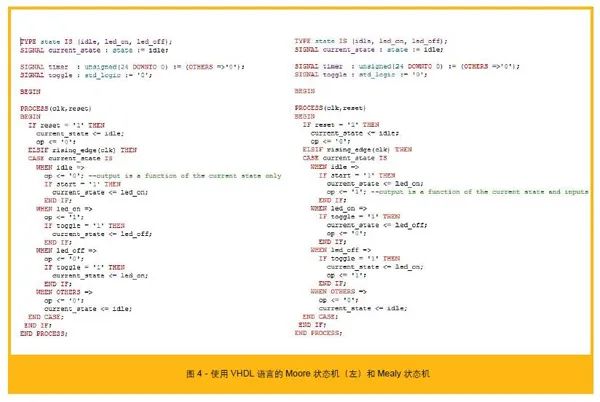

實現狀態機有許多種方法,可分為兩類基本方法。第一類基本方法就是一次性將所有內容集成到單個進程中。第二類基本方法是雙進程法,將組合邏輯和順序邏輯分開。

一般來說,大多數工程師都傾向于實現單進程狀態機。與傳統上講授的雙進程法相比,這種方法具有以下優勢:

? 可以避免組合過程中信號覆蓋不完全造成的閉鎖風險。

? 狀態機的輸出與時鐘保持同步。

? 通常比雙進程實現方案更容易調試。

無論您決定采用哪一種方法來實現狀態機,都需要使用CASE 語句來評估下一狀態的判定和任何輸出,如圖4 所示。該圖并行比較了使用單進程法的Moore 狀態機( 左) 和Mealy 狀態機(右)。

狀態機編碼

狀態變量存儲在觸發器中,使用下一時鐘邊緣上的下一狀態進行更新(即使沒有狀態變化也是如此)。如何使用觸發器來表示狀態值具體取決于狀態的數量和是否選擇用某種特定的方法來管理綜合工具。狀態編碼最常見的三種類型是:

? 順序碼——狀態編碼遵循傳統的狀態二進制序列。

? 格雷碼——除了狀態編碼使用格雷碼,且狀態編碼串

之間只有一個位變化外,其它基本與順序編碼方法類似。

? 獨熱碼——這種方法在狀態機中為每一種狀態分配一個觸發器。只有一個觸發器當前設置為高位,其余均設置為低位。故稱為“獨熱”。

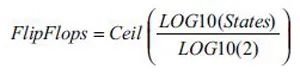

順序編碼和格雷編碼都需要一定數量的觸發器,可以通過下列等式來確定:

相比之下,獨熱編碼法所需的觸發器數量和狀態數量一樣多。

狀態編碼的自動分配取決于狀態機所包含的狀態數量。同時還需要考慮您選擇使用的綜合工具。您可以根據下列經驗法則來選取編碼方法:

? 順序:少于5 種狀態。

? 獨熱:5-50 種狀態。

? 格雷:多于50 種狀態。

一般情況下您不必去考慮使用哪一種狀態編碼方法,而是讓綜合引擎工具確定合適的實現方案,只在選擇的方法出現問題時進行考慮。但是,如果您要全盤自行掌控,并定義狀態編碼方法,也沒必要手動操作,只需使用狀態編碼為每一種狀態設定常數即可。相反地,可以使用代碼中的一個屬性來驅動綜合工具,從而選擇特定的編碼方法。具體如下所示:

其中“sequential”也可以是“gray”和“onehot”。您還可以通過結合使用“safe”屬性來確保在狀態機進入非法狀態時能夠恢復到有效狀態。

另外,您也可以使用syn_encoding 屬性直接定義狀態編碼的值。例如,假設您想要使用下列狀態編碼法來對三態狀態機進行編碼:Idle = “11,” led_on = “10,” led_off = “01(與較傳統的順序“00”、“01”和“10”不同):

前面給出的等式可確定狀態機實現方案所需的觸發器數量。由于不是所有的狀態機都是2 的冪次方,因此某些狀態在設計中將不會用到。實現狀態機的工程師必須負責確保未使用的狀態在設計中得到妥善處理。可以采用幾種適用于多種設計的基本技巧來實現這一目標。對于高度可靠的安全關鍵型設計,則需要采用其它更高級的技巧。(參見Xcell 雜志第73 期刊登的深度文章《在關鍵任務系統中使用FPGA》。該文章著重闡述狀態機保護問題。)

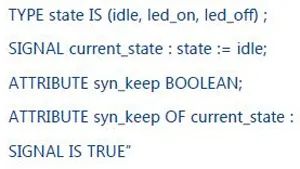

不過對于大多數應用來說,只需要確保狀態機能夠妥善地處理未使用的狀態并在進入非法狀態時能夠正確地恢復。要做到這一點有兩種主要的方法。第一種方法是使用綜合工具實現一個安全的狀態機。綜合工具通常會插入額外的邏輯,用于檢測非法狀態并將狀態機返回到有效狀態。第二種方法是加強對實現邏輯的控制,聲明所有2 的冪次方狀態機的狀態,并使用另一屬性來確保即便是在沒有入口條件下,2 的冪次方狀態機的狀態也不會被優化掉。這意味著除非出錯(單粒子翻轉等),狀態機內部的任何條件都不會進入狀態。下面的代碼顯示了通過使用屬性以防止清除未使用的狀態。

簡而言之,安全高效的狀態機設計對于任何使用FPGA的工程師而言都是一項重要技能。選擇Moore 狀態機、Mealy

狀態機還是混合機取決于整個系統的需求。無論選擇哪種類型的狀態機,充分掌握實現方案所需的工具和技巧,將確保您實現最佳解決方案。

有你想看的精彩 至芯科技-FPGA就業培訓來襲!你的選擇開啟你的高薪之路!7月12號北京中心開課、歡迎咨詢! 至芯科技奮斗的小孩之verilog 基礎語法 基于matlab FPGA verilog的FIR濾波器設計

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、互分享、相互幫助、叫上小伙伴一起加入吧

點個在看你最好看

原文標題:如何在FPGA中實現狀態機

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603319

原文標題:如何在FPGA中實現狀態機

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Simulink中的狀態機建模方法 Simulink數據可視化與分析功能

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區別?

如何在FPGA中實現狀態機

關于SMU狀態機的問題求解

在Verilog中實現Moore型和Mealy型狀態機的方法簡析

C語言實現狀態機設計的技巧與策略

嵌入式編程,如何用 C 語言實現狀態機設計?

關于FX3使用4個線程進行FPGA到USB的數據傳輸-狀態機設置的問題求解

什么是有限狀態機?如何解決傳統有限狀態機「狀態爆炸」問題?

Verilog狀態機+設計實例

如何在FPGA中實現狀態機

如何在FPGA中實現狀態機

評論