OSC-1無源晶振基礎

引言:晶振全稱為晶體振蕩器,其作用在于產生原始的時鐘頻率,在電路中用作時間或頻率的基準源,這個頻率經過頻率發生器的倍頻或分頻后就成了系統中各種不同的總線頻率、時鐘周期。

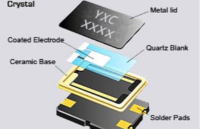

1.無源晶振的等效電路

如圖1-1所示,石英晶體的壓電諧振現象可以用等效電路來模擬,等效電路包括靜態電容C0、動態電容C1、諧振電阻R1、以及動態電感L1,等效電路圖如圖:

圖1-1:無源晶振等效模型

靜態電容C0

靜態電容C0是指晶體兩引腳之間的電容,以水晶為介質,由兩個金屬電極形成的電容,和晶片電極面積(晶體體積)大小和頻率大小呈正比。靜電容C0太高會產生較大的副波,影響頻率穩定性。在實際測數據中,C0值控制在2pF上下時,晶振的輸出穩定性可以得到保障。

如果負載電容CL很大,靜態電容C0的改變對頻率變化的影響很小,頻率更加穩定,所以負載高,遠端相位噪聲好;相反,如果負載電容CL很小,靜電容C0的微小變化就會造成頻率的明顯變化,但近端相位噪聲好,容易調整頻率,晶振容易起振。

動態電容C1

動態電容C1表征振蕩能力,與晶片電極面積(或晶體體積)和頻率大小呈正比。

諧振電阻R1

諧振電阻R1表示晶體在固有諧振頻率下的等效阻抗,與Q值成反比,而Q值是由生長的水晶料品質決定的。

朝著無源晶振越來越小型化,諧振電阻R1也會增大,負載電容CL會降低。

內阻RR和ESR

RR:晶振內阻/晶振電阻,是晶振本身的電阻值。RR越大,起振需要的功耗大,如果激勵電平不變,內阻過大會造成起振困難。

ESR:表征能耗,與Q值成反比。Q值是由生長的水晶料品質決定的,Q值越高,固有頻率則越穩定。

動態電感L1

動態電感L1表征振動質量,與頻率大小成反比。

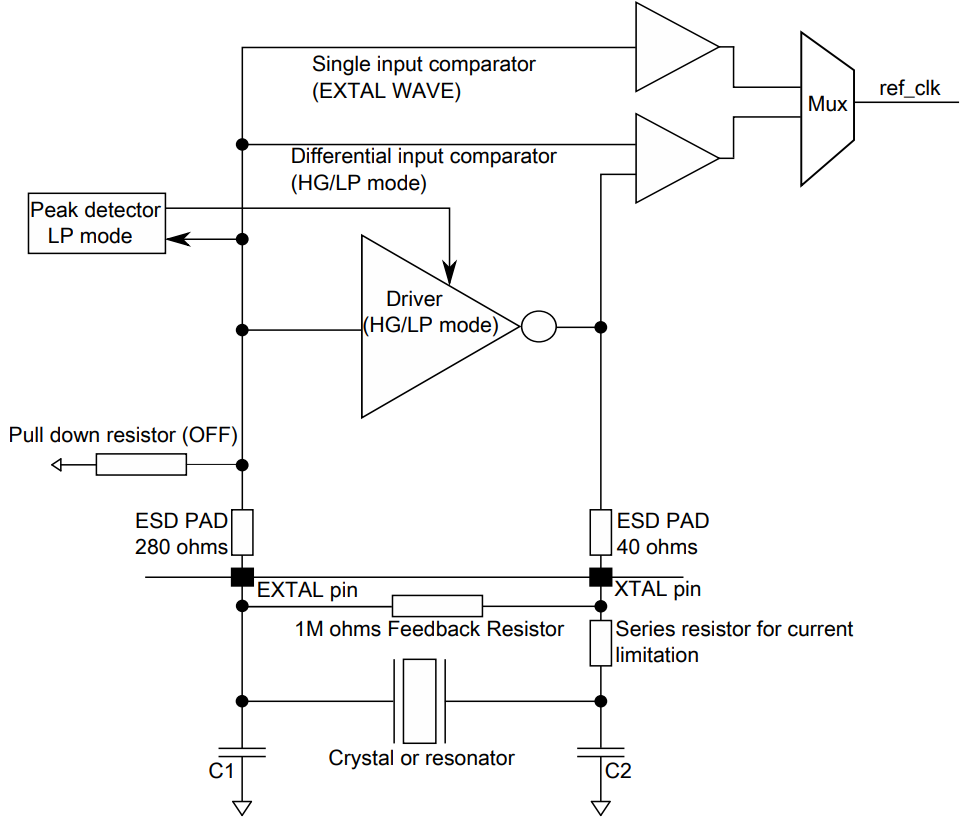

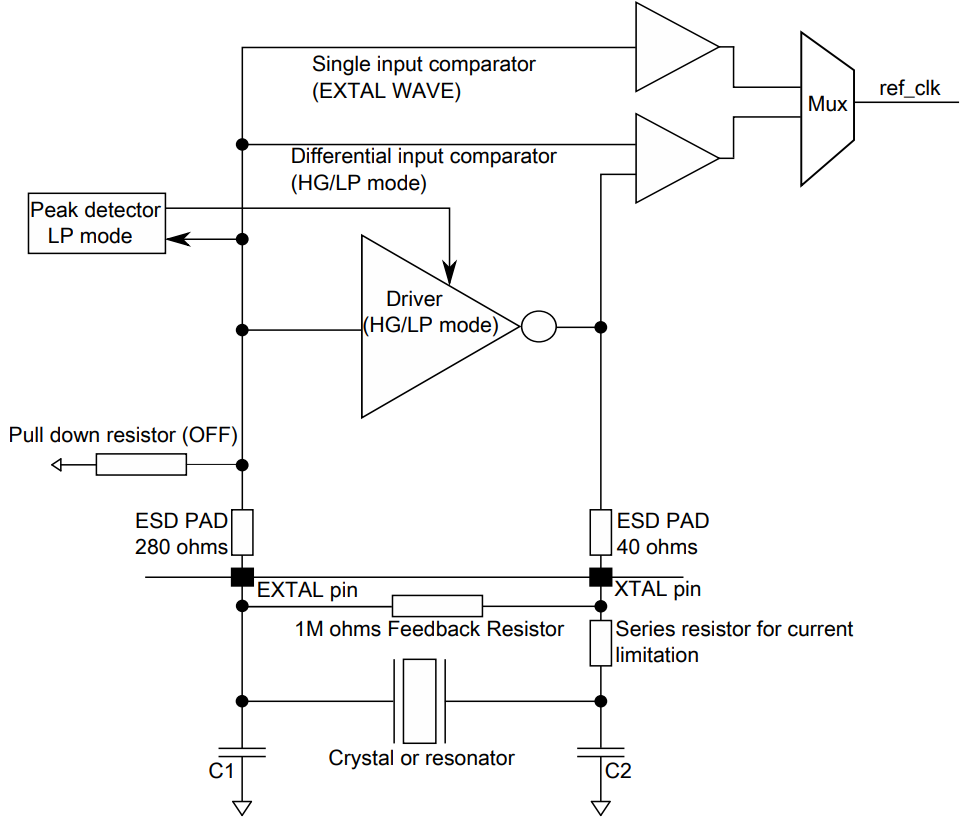

2.無源晶振的電路結構

無源晶振由于自身無法輸出頻率,需要搭配外部放大電路輸出頻率。在并聯型振蕩器電路中,皮爾斯電路是射極接地的并聯振蕩電路,工作有效且穩定。

如圖1-2,皮爾斯振蕩器Pierce Oscillator由晶振、芯片內部的反相放大器(Amp)、匹配電容C1和C2、以及電阻RF和Rd組成。

圖1-2:無源晶振的典型結構

其中反相部分形成一個放大電路Amp,驅動電流從XTAL流出,經過晶體自身從EXTAL流入,因此C1也叫Cg,C2叫Gd。

負載電容CL

負載電容是設計晶體電路最為重要的參數之一,在串聯諧振型電路中,不需要負載電容。晶體的頻率會根據串聯的電容電抗而改變,但在并聯型諧振電路中必不可少。

CL的值大,遠端相位噪聲好,如果過大,則會難調整到標稱頻率,不易起振。CL的值小,近端相位噪聲好,容易調整頻率,容易起振。晶體時鐘的負載電容(CL)建議為8pF ~ 20pF。

如果晶體兩端的等效電容和標稱負載電容存在差異,晶體輸出的頻率將會和標稱工作頻率產生偏差,叫做頻偏。所以為了更接近晶體的負載電容CL,使晶體輸出的頻率則越精準,電路需要增加匹配電容CL1、CL2并考慮電路的雜散電容Cstray。電容器CL1和CL2靠近晶體XTI和XTO引腳,CL1和CL2可以由以下公式(公式1是通用公式,公式2是精確公式,建議使用公式2)來確定:

其中CL是總的負載電容,CL1和CL2是匹配電容,Cs(Cstray)包括XTI/XTO引腳和PCB的寄生電容,通常預估為3 ~ 8pF。

反饋電阻RF

反饋電阻RF有內置和外置兩種,圖1-2所示為外置,有的則是內置于主芯片中,此時晶振兩端就不需要再加反饋電阻RF。

芯片Xin和Xout內部一般是施密特反相器,反相器不能驅動晶體振蕩,需要并聯一個電阻,即RF。電阻完成輸出信號反向180度反饋到輸入端進行負反饋,構成負反饋放大電路(Amp)。如果沒有加RF,晶振電路也可能會起振,但存在不起振或者停振的風險,反饋電阻RF需要確保晶振啟動并保持其穩定,通常RF推薦值為1MΩ-2MΩ。

小結:

1:配合IC內部形成負反饋

2:防止晶體被過分驅動

3:降低諧振阻抗,容易啟動

4:電阻影響波形的脈寬

限流電阻Rd

外部限流電阻Rd作用是限制晶振電路的驅動大小,防止晶體被過分驅動,導致晶體老化或者早期失效,并且阻尼電阻Rd還可以用于抑制電磁干擾輻射。

Rd太小,晶振會承擔太多功耗;Rd太大,電路起振條件不能滿足,晶振無法正常工作。Rd的值不大,通常推薦值為0Ω-33Ω。根據主芯片的晶振波形幅度要求值,可以通過調整Rd的大小來調整晶振輸出波形的振蕩幅度。

小結:

1:降低激勵功率防止損壞

2:限制振蕩幅度。

-

放大器

+關注

關注

143文章

13617瀏覽量

213837 -

無源晶振

+關注

關注

1文章

835瀏覽量

16023 -

晶振

+關注

關注

34文章

2887瀏覽量

68153 -

等效電路

+關注

關注

6文章

292瀏覽量

32796

發布評論請先 登錄

相關推薦

無源晶振的等效電路講解 無源晶振的電路結構介紹

無源晶振的等效電路講解 無源晶振的電路結構介紹

評論