7月5日起,「DPU與智能網卡技術公開課」陸續開講,主講開源DPU、內生安全智能網卡與DPU云化裸金屬。

芯粒是小型模塊化芯片,可以組合形成完整的片上系統 (SoC)。它們被設計用于基于芯粒的架構,其中多個芯粒連接在一起以創建單個復雜的集成電路。與傳統的單片 SoC 相比,基于芯粒的架構具有多項優勢,包括提高性能、降低功耗和提高設計靈活性。Chiplet 技術相對較新,半導體行業的許多公司正在積極開發。

Chiplet 是一種新型芯片,為設計復雜的 SoC 鋪平了道路。Chiplet 可以被視為樂高積木的高科技版本。一個復雜的功能被分解成一個小模塊,然后是可以非常有效地執行單個特定功能的芯粒。因此,使用芯粒的集成系統可以包括:數據存儲、信號處理、計算和數據流管理,構建稱為“芯粒”。

Chiplet 是封裝架構的一部分,它可以定義為一塊物理硅片,通過使用封裝級集成方法將 IP(知識產權)子系統與其他 chiplet 封裝在一起。可以說,chiplet 技術在單個封裝或系統中集成了多種電氣功能。

利用芯粒技術,工程師可以通過將不同類型的第三方 IP 組裝到單個芯片或封裝中來快速且經濟高效地設計復雜芯片。這些第三方 IP 可以是 I/O 驅動程序、內存 IC 和處理器內核 。

chiplets 的想法起源于 DARPA CHIPS(Common Heterogeneous Integration and IP)項目。由于最先進的 SoC 并不總是適合小規模應用,因此為了提高整體系統的靈活性,CHIP 計劃尋求創建一種新的 IP 重用范例,即 chiplet。

雖然當今大多數電子設備中的計算機技術在很大程度上仍由傳統芯片組主導,但隨著時間的推移,這種趨勢似乎很明顯會發生變化。許多專家認為,隨著這些先進技術的發展,專用芯粒將成為消費設備的普遍特征。有許多可靠且更便宜的技術可用于設計芯粒。

摩爾定律是英特爾聯合創始人戈登摩爾于 1965 年做出的預測,即微芯片上的晶體管數量大約每兩年翻一番,從而導致計算能力呈指數級增長并降低成本。Chiplet 技術可以看作是擴展摩爾定律并延續半導體行業提高性能和降低成本的趨勢的一種方式。

芯粒技術可以幫助擴展摩爾定律的一種方式是允許創建更復雜和更強大的 SoC,而無需將所有必要的組件安裝到單個單片芯片上。通過將復雜的 SoC 分解成更小的模塊化芯粒并將它們連接在一起,可以繼續擴大晶體管和其他組件的數量,而不會達到單個芯片的物理極限。這有助于跟上摩爾定律預測的性能改進和成本降低的步伐。

如今,異構芯粒集成市場增長更加迅速。AMD 的 Epyc 和英特爾的 Lakefield 等不同的微處理器采用芯粒設計和異構集成封裝技術進行大量生產。

01.芯粒歷史

芯粒的概念已經存在了幾十年,但近年來作為應對縮小傳統單片 IC 挑戰的一種方式獲得了更多關注。隨著摩爾定律的不斷推進,單片IC的尺寸和復雜度顯著增加,導致成本更高,制造難度更大。基于芯粒的設計為這些挑戰提供了一個潛在的解決方案,它允許公司使用更小、更專業的芯粒,這些芯粒可以輕松組合并組裝成一個完整的系統。

“Chiplet”這個詞相對較新,只使用了大約五年左右。它最初是由密歇根大學的研究人員和科學家創造的,當時他們開始研究改進計算機芯片設計、效率和功能的方法。這個詞是“chip”和“petite”的組合,可以翻譯成“小”的意思。因此,Chiplet 是一種非常小的計算機芯片,用于高科技設備,可執行比傳統 CPU 芯片更復雜的任務。它在過去幾年發展迅速,許多專家認為,由于其增強的功能,它將開始取代消費設備中的傳統芯片組。

2007 年 5 月,DARPA(國防高級研究計劃局)啟動了首個用于異構芯粒的COSMOS(硅基復合半導體材料)。DARPA 啟動了CHIPS,其目的是用芯粒制造模塊化計算機。它還涉及不同的集成標準、IP 塊和可用的設計工具。

02.市場預測

芯粒市場預計在未來幾年將經歷顯著增長。根據 MarketsandMarkets 發布的一份報告,到 2025 年,該市場的價值預計將達到 57 億美元。這表示從 2020 年到 2025 年的復合年增長率 (CAGR) 為 18.9%。

根據 Transparency Market Research 發布的一份報告,到 2031 年,芯粒市場的價值預計將達到 472 億美元。這代表 2021 年至 2031 年的復合年增長率為 23.9%。該預測考慮了對高性能計算和數據分析不斷增長的需求,以及電子設計中模塊化和定制化的增長趨勢。

這些數據表明,芯粒市場有望在未來幾年實現有希望的增長。芯粒是小型模塊化芯片,可以組合成更大、更復雜的片上系統 (SoC)。與傳統的單片芯片相比,它們具有許多優勢,包括提高性能、節省成本和設計靈活性。這些因素,加上對高性能計算和數據分析的需求不斷增長,可能會在未來幾年推動芯粒市場的增長。

03.芯粒的好處以及為什么芯粒更好?

與傳統的單片處理器設計相比,芯粒具有多項重要優勢。它們可以快速、輕松地定制和升級,從而減少開發時間和成本。也許最重要的是,芯粒通過使用針對特定任務優化的專用處理元件來提高性能。例如,如果您的設備中的 AI 應用程序需要高處理能力,您可以用專為 AI 任務設計的芯粒取代傳統 CPU。

除了這些性能優勢外,芯粒還可以降低處理器的尺寸和功率要求。通過將多個單獨的功能整合到單個單元中,它們消除了對傳統芯片所需的大部分布線、冷卻基礎設施和其他組件的需求。這降低了制造成本,并允許更小的設備設計,非常適合智能手機或 AR/VR 耳機等移動設備。

芯粒提供的靈活性還提供了重要的設計和開發優勢。由于可以輕松定制和升級,chiplet 使制造商能夠快速適應不斷變化的市場條件或新技術發展。它們還通過減少設計和制造定制 SoC 所需的步驟來簡化生產過程。

chiplet 技術允許制造商使用更小、更專業的 chiplet 而不是單個單片芯片來完成某些任務,從而有助于提高產量并降低成本。這有助于提高產量,因為它降低了芯片制造過程的復雜性,從而可以減少出現的缺陷數量并提高可用芯片的整體產量。此外,由于芯粒可以單獨設計和制造,因此可以更輕松地優化每個特定芯粒的制造過程,從而進一步提高產量。

芯粒有助于降低成本的另一種方式是允許制造商使用混合搭配方法來創建 SoC。制造商不必為每個新產品從頭開始設計和制造新芯片,而是可以使用現有芯粒的組合來創建所需的 SoC,這樣可以更快、更具成本效益。這對于需要將產品快速推向市場并且需要能夠快速更改其 SoC 以滿足不斷變化的市場需求的公司來說尤其有用。

04.芯粒挑戰

chiplets技術面臨以下挑戰:

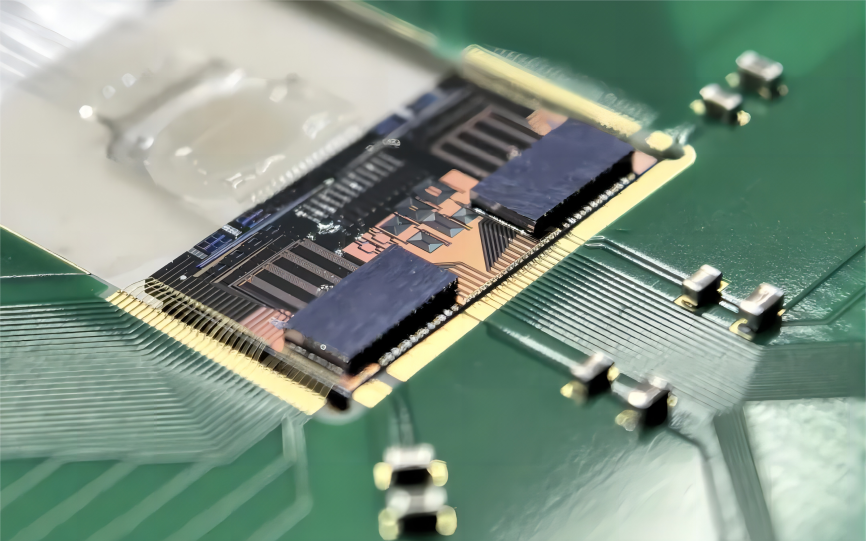

首要的挑戰是確保 chiplet 模式的低成本和高可靠性,它基于先進的封裝技術。封裝技術是chiplet關注的焦點。從 TMSC 向封裝的積極轉變以及 InFo 和 CoWos 等其他封裝技術的發展也可以看出其意義。

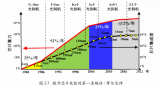

第二個挑戰是以經濟的產品率保持良好的產品質量。雖然,Chiplet 是認證產品,但仍然存在良率問題。如果在 SiP 中的一個 chiplet 硅芯片中發現問題,整個 chiplet 系統的成本就會更高。下圖中的圖表描述了相對于芯片面積的成品率百分比。

另一個突出的挑戰是測試覆蓋率。由于多個芯粒嵌入在一起,每個芯粒可以連接到有限數量的引腳。一些芯粒在引腳之外變得不可訪問,這導致芯片測試出現問題 。

05.芯粒標準

雖然芯粒帶來了許多挑戰,尤其是在商業應用和可擴展性方面,但它們為當今一些最緊迫的芯片設計問題提供了一個有前途的解決方案。隨著持續的發展和創新,我們可以期待很快看到芯粒的更廣泛使用 。

隨著 chiplet 技術的發展勢頭越來越強勁,業內許多大公司開始涉足是很自然的。GlobalFoundries 和三星是走在這一趨勢前沿的兩家主要公司,各自致力于開發自己的解決方案來應對芯粒挑戰。英特爾、AMD、高通、Arm、臺積電和三星正在合作定義基于芯粒的 CPU 的新標準。這就催生了UCIe 。

UCIe ( Universal Chiplet Interconnect Express )的推動者群體相當龐大,其中包括 AMD、Arm、Intel 和 Qualcomm,芯片廠臺積電和三星(以及 Intel),芯片封裝公司 Advanced Semiconductor Engineering,以及云計算提供商 Google、Microsoft、和Meta。

已經開發了芯粒標準化工作來幫助解決與這些連接的性能相關的問題。其中包括改進熱管理、降低功耗和減少延遲。它們還可以通過增加流經這些連接的數據流量來幫助提高芯片間通信和集成的效率。

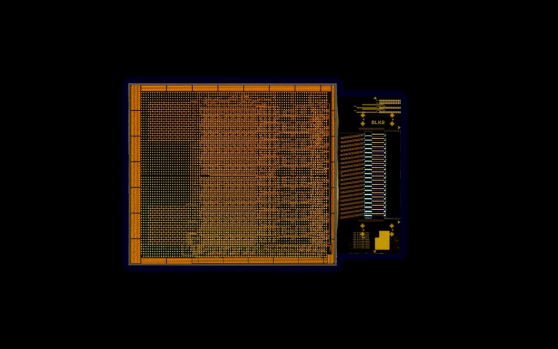

Chiplet 標準化工作正在進行中,目前有許多不同的標準用于芯片之間的接口。例如,加速器緩存一致性互連 (CCIX) 應該是 SoC 芯粒的未來標準。多個芯片包含在同一個芯片封裝中,它們一起充當一個大的單芯片。為了讓最終用戶能夠輕松混合和匹配芯粒組件,UCIe 1.0 規范提供了完整的標準化芯片到芯片互連,包括物理層、協議棧、軟件模型和合規性測試。

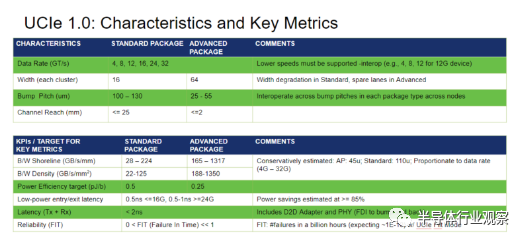

下表顯示了 UCIe 1.0 的特性和關鍵矩陣。UCIe 標準涵蓋芯粒設計的物理層、物理層和協議層。這些標準還定義了芯粒應如何連接在一起以相互通信。UCIe 1.0 版定義了兩個不同的性能級別以適應不同的封裝選項:標準和高級。

在標準封裝方案中,芯粒之間定義了 25 毫米間距的 16 條數據通道。而在先進封裝中,允許有 64 個數據通道和 2mm 的空間 。UCIe 1.0 標準基本上是為 2D 和 2.5D 芯片封裝定義的,而不是像即將推出的 Foveros Direct 這樣的 3D 直接芯片到芯片技術。隨著 3D 芯片封裝變得可用,該標準將需要更新,以便考慮到可能的附加功能和更高的密度。  ?

?

芯粒標準化的最大挑戰之一是確保芯片可以設計為與各種中介層設計和標準一起使用。在這方面已經取得了一些進展,包括多個組織努力為芯粒接口編寫標準化規范。然而,隨著越來越多的公司采用這些類型的技術,確保兼容性可能會變得越來越困難。有興趣實施這些技術的公司需要密切關注 chiplet 標準化工作的現狀,以最大限度地提高成功的機會。

06.芯粒的未來

芯粒技術是一種模塊化設計方法,涉及創建小型、獨立的芯片或“芯粒”,這些芯片可以組合起來創建更大的系統。每個芯粒都旨在執行特定功能,通過組合不同的芯粒,公司可以創建滿足其特定需求的定制解決方案。Chiplet 技術有可能徹底改變電子元件的設計和制造方式,因為它允許更高效和更具成本效益的生產過程,并能夠創造更專業和定制化的產品。

芯粒技術有幾個關鍵優勢。首先,它允許更靈活和可擴展的設計。通過使用芯粒,公司可以混合和匹配不同的組件,以創建適合其特定性能和功率要求的解決方案。這可以帶來更高效和更具成本效益的制造流程,因為它允許公司創建針對其特定需求優化的產品。

其次,芯粒技術有助于提高電子設備的性能。通過使用芯粒,公司可以創建針對特定任務優化的解決方案,從而實現更快、更高效的性能。此外,chiplet 技術有助于降低功耗,因為它可以更有效地利用資源。

最后,chiplet 技術具有加速電子行業創新的潛力。通過支持創建更專業化和定制化的產品,chiplet 技術可以引領新技術和創新技術的發展。

很難預測 chiplet 技術的確切未來,因為它將取決于許多因素,包括技術進步、市場需求和個別公司的戰略。然而,芯粒技術有可能徹底改變處理器和其他電子元件的設計和制造方式。通過允許公司混合和匹配不同的芯粒來創建定制產品,芯粒技術可以帶來更高效和更具成本效益的制造過程。它還可以允許創建更專業和定制的產品,因為公司可以選擇最能滿足其性能和功率要求的特定芯粒。

審核編輯:劉清

-

微處理器

+關注

關注

11文章

2272瀏覽量

82605 -

片上系統

+關注

關注

0文章

186瀏覽量

26842 -

SoC芯片

+關注

關注

1文章

616瀏覽量

34969 -

3D芯片封裝

+關注

關注

0文章

2瀏覽量

5491 -

chiplet

+關注

關注

6文章

434瀏覽量

12609 -

芯粒

+關注

關注

0文章

59瀏覽量

143

原文標題:Chiplet,必然的選擇

文章出處:【微信號:算力基建,微信公眾號:算力基建】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

國內首款2Tb/s 3D集成硅光芯粒成功出樣,華為、英偉達等巨頭爭相布局

知存科技邀您相約第二屆集成芯片和芯粒大會

集成芯片與芯粒技術詳解

Imec牽頭啟動汽車芯粒計劃

強勢入局芯粒技術鏈 東方晶源PanSys產品重磅發布

北極雄芯“啟明 935”系列芯粒成功交付流片

芯德科技揚州晶圓級芯粒先進封裝基地項目封頂

英特爾OCI芯粒在新興AI基礎設施中實現光學I/O(輸入/輸出)共封裝

英特爾突破技術壁壘,推出全新硅光集成OCI芯粒

英特爾實現光學IO芯粒的完全集成

原粒半導體與超摩科技達成戰略合作

國信光電子創新中心發布首款2Tb/s硅光互連芯粒

為什么選擇將AMBA CHI用于芯粒呢?

芯粒的好處以及為什么芯粒更好?

芯粒的好處以及為什么芯粒更好?

評論