現代邏輯設計中,時序邏輯設計是核心,而寄存器又是時序邏輯的基礎,下面將介紹幾種常見的寄存器的Verilog設計代碼供初學者進行學習理解。

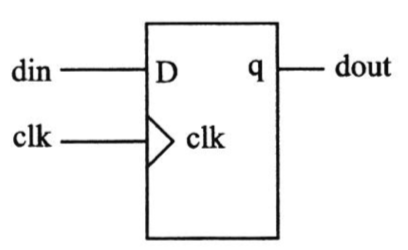

1、簡單寄存器

基本寄存器

module dff(clk, din, dout)

input clk;

input din;

output dout;

reg dout;

always @ (posedge clk)begin

dout <= din;

end

endmodule

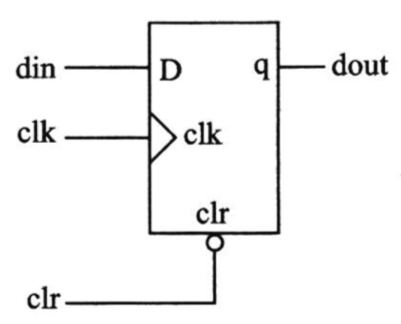

2、異步復位寄存器

異步復位寄存器

module dff(clk, rst_n, din, dout);

input clk;

input rst_n;

input din;

output dout;

reg dout;

always @ (posedge clk or negedge rst_n)begin

if(! rst_n)dout <= 1'b0;

else dout <= din;

end

endmodule

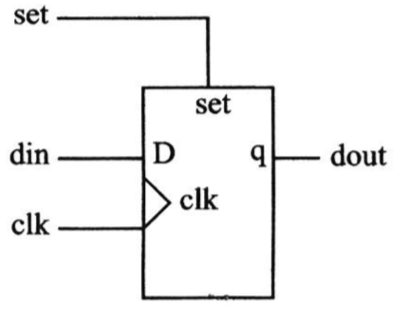

3、帶異步置位的寄存器

異步置位寄存器

module dff(clk, set, din, dout);

input clk;

input din;

input set;

output dout;

reg dout;

always @ (posedge clk or posedge set)begin

if(set) dout <= 1'b1;

else dout <= din;

end

endmodule

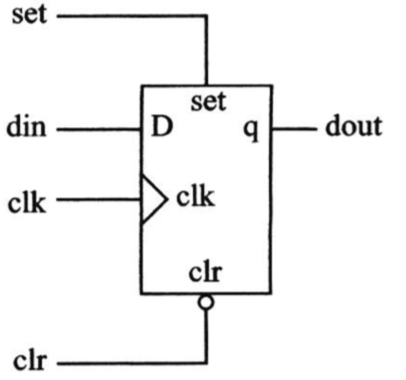

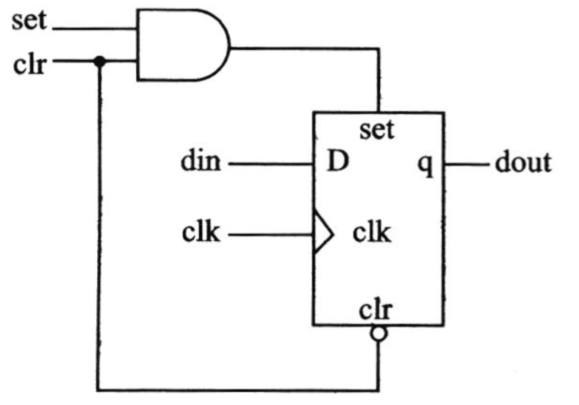

4、既帶異步復位又帶異步置位的寄存器

異步復位和置位寄存器

異步復位和置位寄存器(復位優先級高)

module dff(clk, rst_n, set, din, dout);

input clk;

input din;

input rst_n;

input set;

output dout;

reg dout;

always @ (posedge clk or negedge rst_n posedge set)begin

if(! rst_n) dout <= 1'b0;

else if(set) dout <= 1'b1;

else dout <= din;

end

endmodule

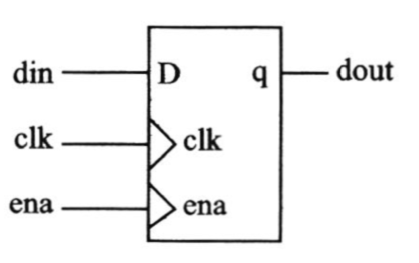

5、同步使能功能的寄存器

帶同步使能的寄存器

module dff(clk, ena, din, dout);

input clk;

input din;

input ena;

output dout;

reg dout;

always @ (posedge clk) begin

if(ena) dout <= din;

end

endmodule

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603387 -

寄存器

+關注

關注

31文章

5343瀏覽量

120368 -

Verilog

+關注

關注

28文章

1351瀏覽量

110100 -

時序邏輯

+關注

關注

0文章

39瀏覽量

9163 -

異步復位

+關注

關注

0文章

47瀏覽量

13314

發布評論請先 登錄

相關推薦

Verilog寄存器初始化沒有復位引腳

寄存器培訓教程

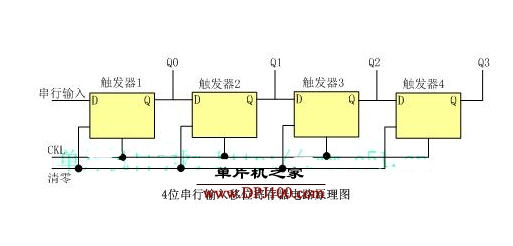

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途

寄存器變量

移位寄存器的原理

Verilog設計寄存器

Verilog設計寄存器

評論