SpinalHDL是基于Scala全新的硬件描述語言,解決了不少Verilog等傳統HDL語言的痛點,可以快速的完成某些IP的開發,和完美的融入現有的開發流程。

誠然SpinalHDL的學習路線是比較陡峭的。另外在團隊協作中,你可以要求你的同伴對Verilog,VHDL語言進行掌握,但是不能要求他們也掌握SpinalHDL,Chisel這些語言,所以你的代碼怎么安排別人接手也是一個問題。但是這并不妨礙我們采用SpinalHDL來快速驗證我們某個想法是否是合理的,快速驗證某個架構是否合理。

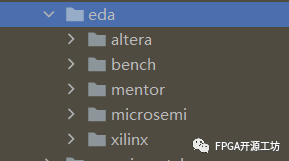

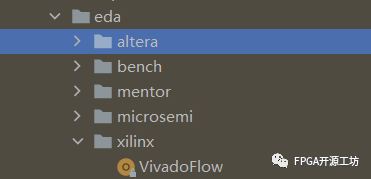

在SpinalHDL的lib里面有一個eda目錄,里面有Xilinx,Altera等公司的一套工具庫。

我們以Xilinx的為例來說明怎么利用里面的工具庫來驗證我們的代碼能夠跑的頻率和占用的資源。

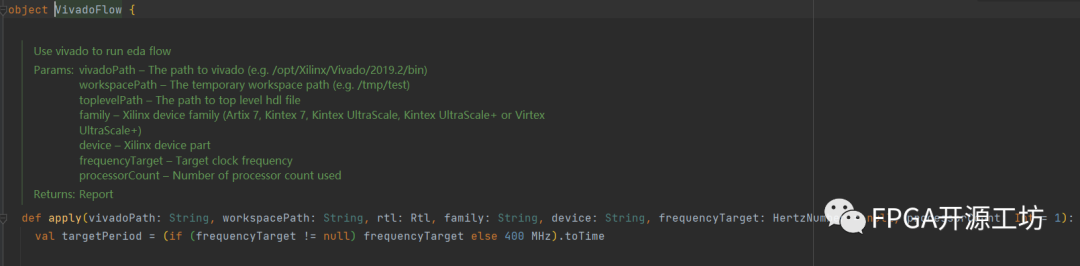

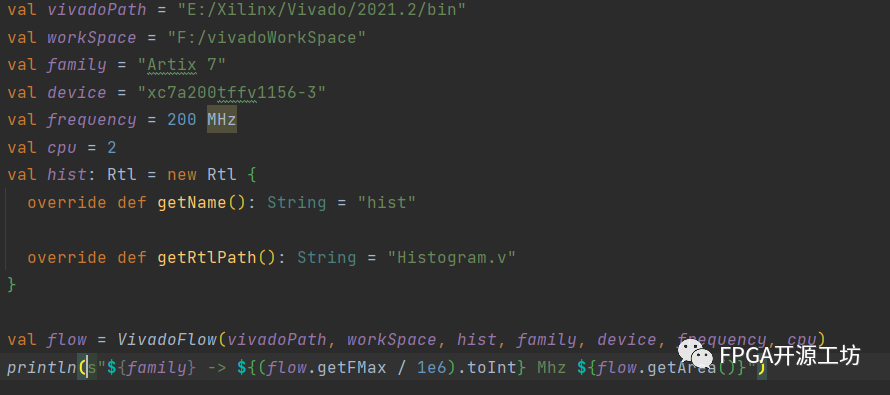

可以看到里面只有一個VivadoFlow的文件,在VivadoFlow里面需要我們指定Vivado的路徑,工作目錄,以及RTL,目標器件,頻率等一系列參數

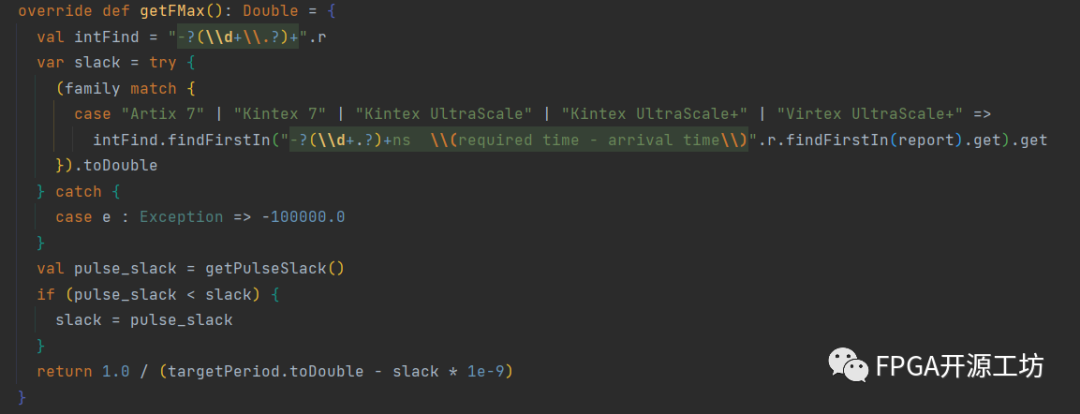

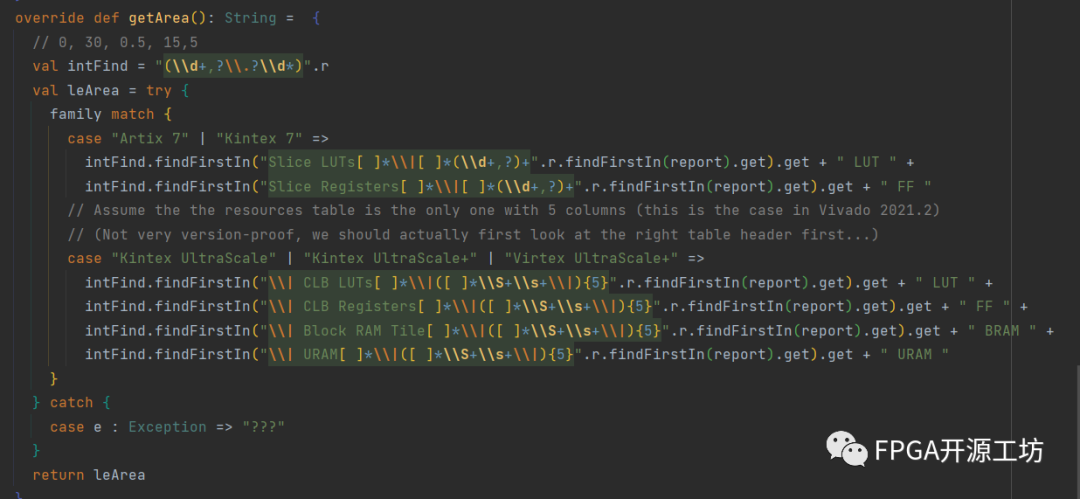

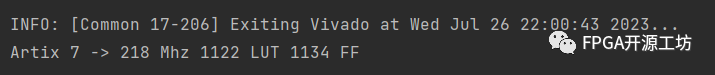

之后便可以獲取到當前RTL能夠跑到的最大頻率和所需的資源了。可以看到A7和K7返回的是利用的LUT和FF,而KU,VU等器件把BRAM和URAM的資源利用也得到了。

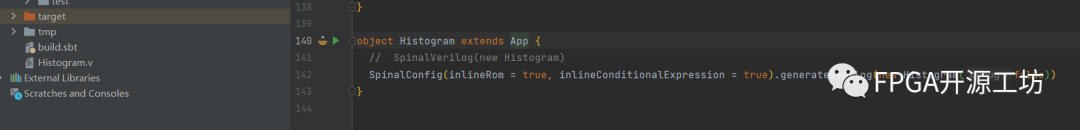

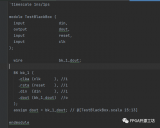

通過一個直方圖均衡化的例子來說明這個VivadoFlow如何評估資源的消耗。

通過上面的代碼指明vivado的路徑,工作路徑,以及目標器件和頻率就可以愉快的開始等著頻率和資源的利用報告了。

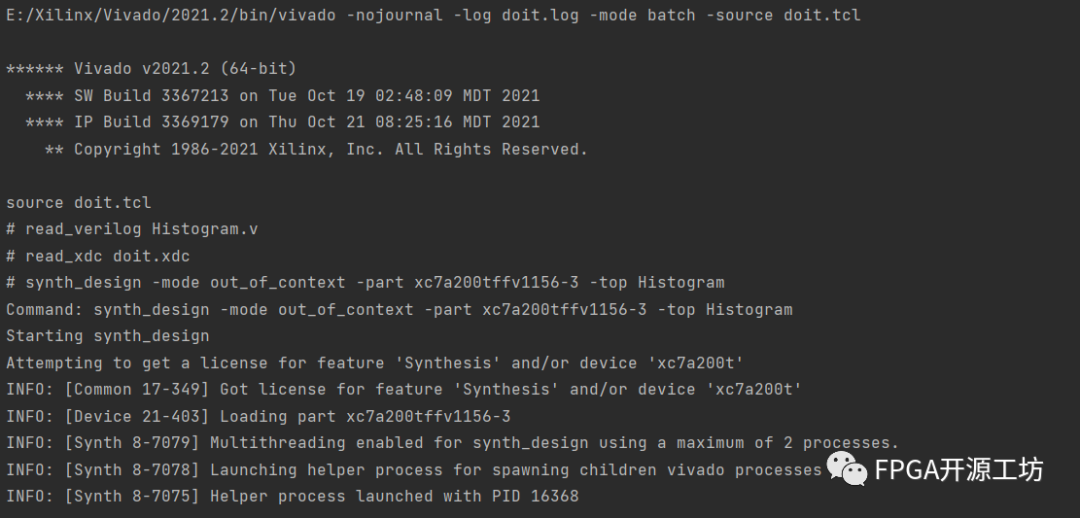

可以看到IDEA的窗口已經開始打印相關的log了。

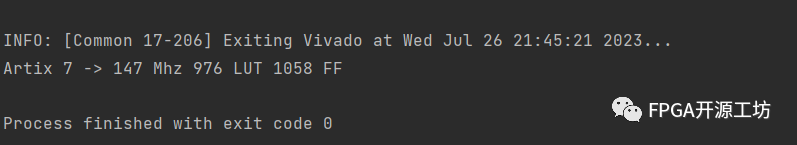

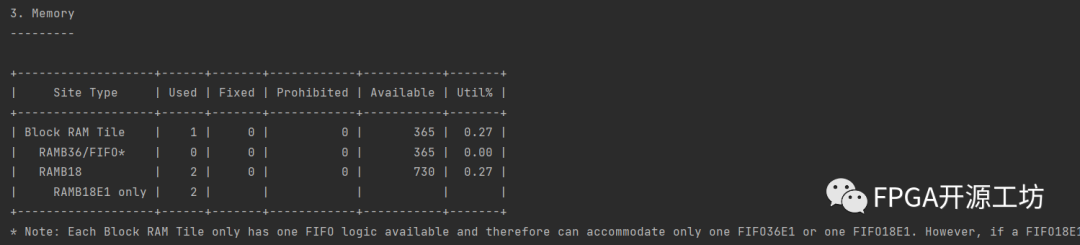

可以看到實際能夠跑到的頻率只有147M,資源利用了976個LUT,1058個FF,因為選了A7的器件,所以BRAM的利用并沒有輸出。但是可以在中間日志中看到。

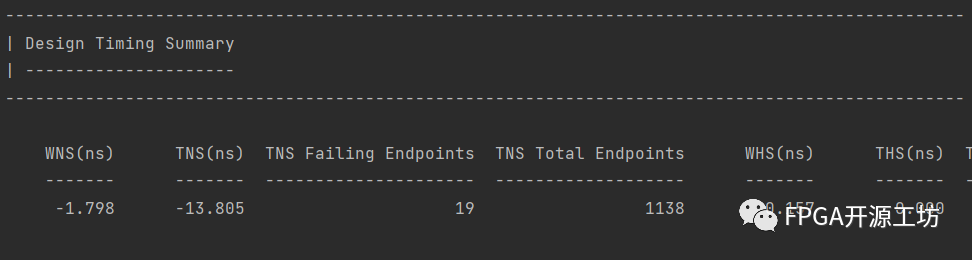

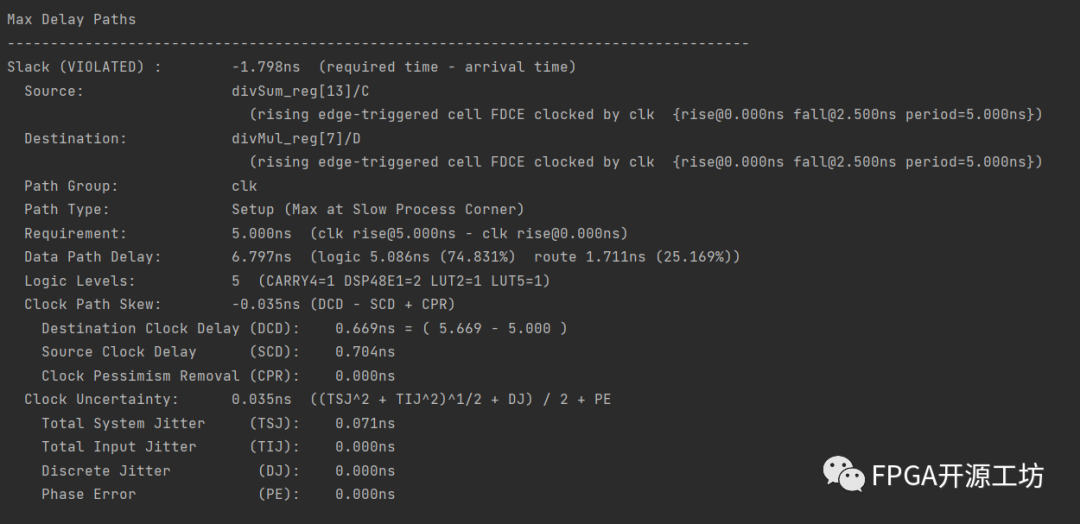

我們在之前設置的目標頻率是200MHz,但是經過評估之后只能跑到147M,說明我們還需要優化下現在的代碼,繼續查看日志,可以看到建立時間不滿足。具體不滿足的地方在日志中也有輸出。

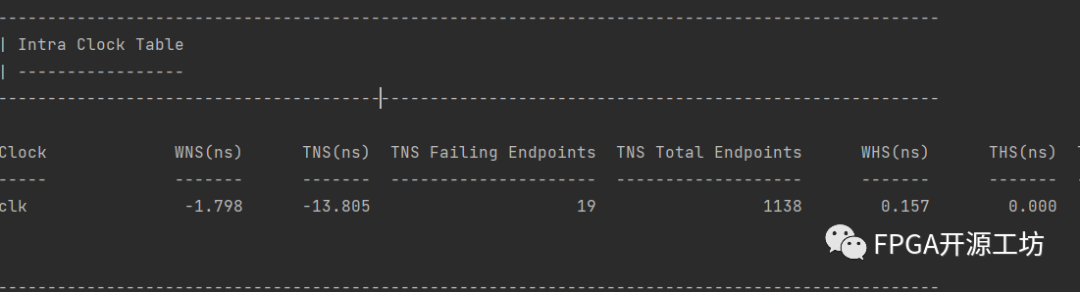

Intra 說明是同一時鐘下的,不存在跨時鐘的問題,當然這個在我們設計的時候已經確定了。

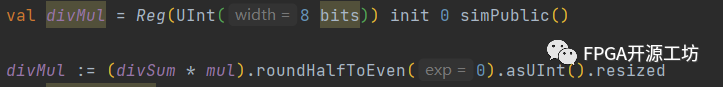

通過上面的日志可以確定是divSum和divMul之間的時序不滿足。這一部分是一個乘法和截尾操作。乘法被映射到DSP上,我們知道xilinx的DSP內部有幾級的寄存器,如果把這幾級寄存器給利用起來那么就可以提高時鐘頻率,所以可以通過打拍的方式,讓這幾個寄存器被DSP所吸收掉,從而達到時序收斂的目的。(PS:如果是異步復位的寄存器是不能被7系列的FPGA的DSP所吸收的)

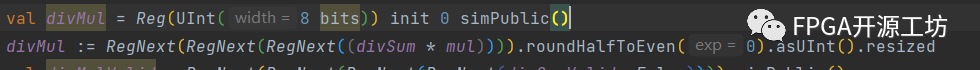

所以兩種不同的代碼如上。

經過評估后可以跑到218MHz,的確有性能上的提升。

這個只是一個很小的模塊,可以這樣很快完成設計上的探索。

當我們要進行不同實現方式的探索的時候,便可以這樣快速的完成,不斷的完善模塊的架構。

責任編輯:彭菁

-

開發

+關注

關注

0文章

370瀏覽量

40897 -

Verilog

+關注

關注

28文章

1351瀏覽量

110298

原文標題:SpinalHDL--快速評估代碼性能

文章出處:【微信號:FPGA開源工坊,微信公眾號:FPGA開源工坊】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何實現SpinalHDL 環境搭建

在SpinalHDL里實現優雅的添加待跟蹤波形信號

聊一聊SpinalHDL 1.6.1引入的blackbox inline功能

在SpinalHDL中關于casez的使用

在SpinalHDL中的代碼組織結構如何實現Component參數化設計呢

SpinalHDL是如何讓仿真跑起來的

如何在SpinalHDL里啟動一個仿真

SpinalHDL開發環境搭建步驟相關資料分享

SpinalHDL設計錯誤總結相關資料分享

基于Windows系統的SpinalHDL開發環境搭建步驟

從Verilog到SpinalHDL

SpinalHDL里如何實現Sobel邊緣檢測

SpinalHDL BlackBox時鐘與復位

SpinalHDL Simulation性能提升測試

spinalhdl轉Verilog可讀性 SpinalHDL開發流程

spinalhdl轉Verilog可讀性 SpinalHDL開發流程

評論