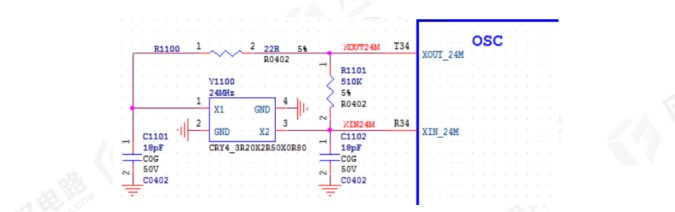

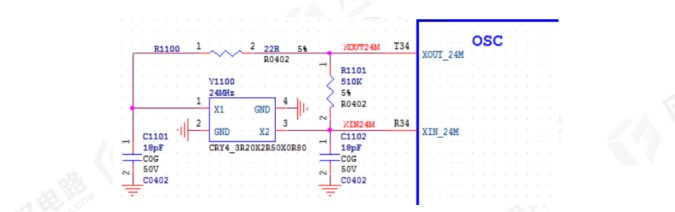

時鐘電路就是類似像時鐘一樣準確運動的震蕩電路,任何工作都是依照時間順序,那么產生這個時間的電路就是時鐘電路,時鐘電路一般是由晶體振蕩器、晶振、控制芯片以及匹配電容組成,如圖1所示。

圖1 時鐘電路

針對時鐘電路PCB設計有以下注意事項:

1、晶體電路布局需要優先考慮,布局整體緊湊,布局時應與芯片在同一層并盡量靠近放置,以避免打過孔,晶體走線盡可能的短,遠離干擾源,盡量遠離板邊緣;

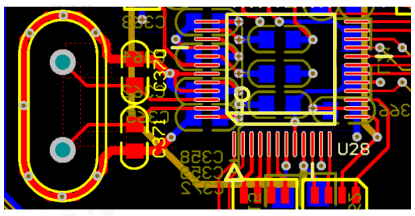

2、如果出現晶體電路在布局過程中與芯片放置在不同層的情況,應盡可能的讓靠近芯片,讓走線變短,并需要將晶體走線全程進行包地處理,以避免被干擾;

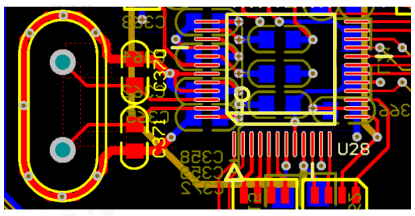

3、晶體以及時鐘信號走線需要全程包地處理,包地線每隔200-300mil至少添加一個GND過孔,并且必須保證鄰層的地參考面完整,如圖2所示;

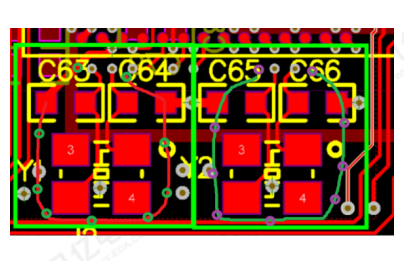

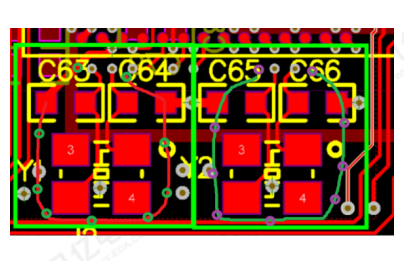

4、晶體的當前層可圍繞其進行GND走線形成地環,在地環放置GND過孔,連接到相鄰的GND平面層,用以隔離噪聲,如圖3所示。

圖2 晶體布局布線

圖3 晶振布局布線

4、時鐘走線Xin與Xout以及晶體下方投影區域禁止任何走線,避免噪聲耦合進入時鐘電路;

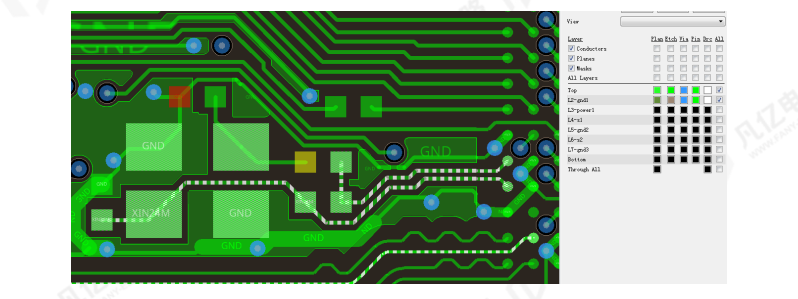

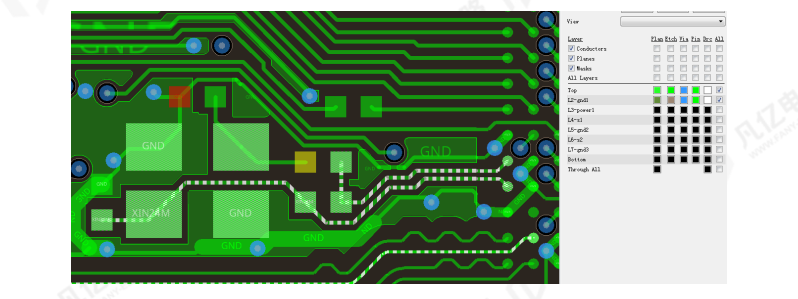

6、晶體下面相鄰層必須保證完整的參考平面,避免出現跨分割現象,有助于隔離噪聲,保持晶體輸出,如下圖4所示。

圖4 第二層為完整的參考平面

聲明:

本文凡億教育原創文章,轉載請注明來源!投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:Clock時鐘電路PCB設計布局布線要求

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

相關推薦

本文分享了電子工程師在PCB設計方面的經驗,包括PCB布局、布線、電磁兼容性優化等內容,旨在幫助初學者掌握PCB設計的關鍵技術。

![的頭像]() 發表于

發表于 01-21 15:15

?99次閱讀

在電子產品設計中,PCB布局布線是重要的一步,PCB布局布線的好壞將直接影響

![的頭像]() 發表于

發表于 01-07 09:21

?310次閱讀

前期準備

?

PCB設計前要與原理設計、可靠性設計、電磁兼容設計、工藝結構溝通,

確

定PCB整體的外圍結構和接口布局。

?

與原理設計確認PCB網表和器件封裝。

發表于 12-26 16:51

常用的PCB設計規則

發表于 11-09 14:10

?89次下載

所提供的表格僅供參考,實際引腳定義可能會因不同的串行接口實現而有所不同。 具體引腳定義應參考相關硬件文檔或電路圖 。

三、串行接口PCB設計

1、串口一般用到的信號只有 RXD,TXD,GND 。

2

發表于 09-18 12:02

在PCB設計中,布局是一個非常重要的環節,它直接影響到電路的性能、可靠性和成本。以下是關于PCB布局的一些要點,這些要點將幫助您設計出高質量

![的頭像]() 發表于

發表于 09-02 14:48

?486次閱讀

。以下是它們之間的關系: PCB設計與PCB制板的關系 1. PCB設計: PCB設計是指在電子產品開發過程中,設計工程師使用專業的電子設計軟件創建

![的頭像]() 發表于

發表于 08-12 10:04

?582次閱讀

一站式PCBA智造廠家今天為大家講講晶振在PCB板上如何布局?PCB板時鐘晶振及相關元件布線原則。晶振布

![的頭像]() 發表于

發表于 07-08 09:45

?596次閱讀

是否滿足ESD或者EMI防護設計要求,撇開原理圖設計,PCB設計一般需要我們從PCB布局和PCB布線

![的頭像]() 發表于

發表于 06-12 09:49

?667次閱讀

針對時鐘電路PCB設計有以下注意事項:1、晶體電路布局需要優先考慮,布局整體緊湊,

發表于 06-11 10:24

?0次下載

PCB電源布線是印刷電路板設計中非常重要的一環。電源布線的好壞直接影響到電路的穩定性和性能。本文將介紹幾個

發表于 05-16 11:50

?2187次閱讀

BOSHIDA ?DC電源模塊的 PCB設計和布局指南 DC電源模塊的PCB設計和布局是一個關鍵的步驟,它直接影響到電源的性能和穩定性。下面是一些DC電源模塊的

![的頭像]() 發表于

發表于 03-05 14:30

?1354次閱讀

清寶PCB抄板今天為大家講講PCB設計高頻電路板布線要注意什么?高頻電路PCB

![的頭像]() 發表于

發表于 03-04 14:01

?508次閱讀

制造缺陷,提高產品的穩定性和可靠性。 而在PCB設計中,布局與布線是決定整個電路板性能、可靠性及制造成本的關鍵環節之一,所以本文將重點介紹其相關檢查項概述。 ? 一、

![的頭像]() 發表于

發表于 02-27 18:22

?1904次閱讀

缺陷,提高產品的穩定性和可靠性。

而在PCB設計中,布局與布線是決定整個電路板性能、可靠性及制造成本的關鍵環節之一,所以本文將重點介紹其相關檢查項概述。

一、

發表于 02-27 18:19

Clock時鐘電路PCB設計布局布線要求

Clock時鐘電路PCB設計布局布線要求

評論