異構IC封裝已經投入生產,并且越來越多的客戶正在 Amkor 以及其他外包半導體組裝和測試 (OSAT) 供應商和代工供應商處開發和驗證其產品。

這種新的多管芯實施例的基本原理已經得到充分記錄和討論。歸根結底,更多的系統內容正在轉移到軟件包本身中,從而在性能、成本和上市時間 (TTM) 方面帶來好處。由于較小的小芯片的產量更高,因此總硅成本可以降低。異質封裝還提供了使用混合硅工藝節點來進一步優化硅成本的機會。雖然異構 IC 封裝更昂貴,但積極的權衡/好處是較低的總硅成本和積極的 TTM 優勢。轉向異構方法需要在設計、IC 和封裝制造以及測試方面建立基礎設施。

隨著每個 OSAT 和代工廠提供自己的技術,支持小芯片和異構結構的 IC 封裝選項也不斷傳播。結果,術語變得相當混亂。值得慶幸的是,這些封裝結構比目前行業中存在的術語簡單得多。多芯片產品必須集成到一個功能單元中,這可以在傳統的 IC 封裝基板上完成,也可以通過使用更高密度的集成方法(即晶圓級多芯片模塊、超細線集成或兩者兼而有之)來完成。然后將該模塊附著到 IC 封裝基板上。

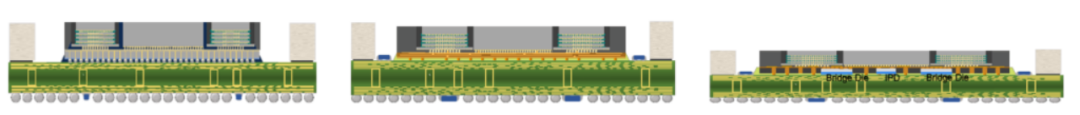

第一種選擇以歷史悠久的多芯片模塊 (MCM) 為代表,該模塊已投入生產數十年,現代設計趨向于在基板上采用更高的硅和無源密度。高密度集成方法的第二個選擇是創建集成芯片或小芯片的模塊,這需要芯片間接口的超細線路布線。如今,這些是 (A) 基于硅中介層的模塊 - 2.5D 硅通孔 (TSV)、(B) 基于高密度扇出 (HDFO) 多層再分布層 (RDL) 方法的模塊,或 (C) 具有橋接器的模塊,如圖 1 所示。

圖 1:a) 2.5D TSV(硅中介層,b)HDFO (S-SWIFT) RDL 中介層,c) 橋 (S-Connect)(RDL+ 橋)。

異構 IC 封裝設計

基于 HDFO 內插器的模塊已通過內部認證,是客戶產品,并且正在認證中。由于向小芯片的過渡剛剛開始,市場上使用 HDFO 內插器的不同設備的數量仍然有限。然而,市場正在發生變化,大多數已經在生產高端單片或 MCM 設備的先進封裝客戶要么正在積極驗證 HDFO 中介層,要么正在詢問,以期開始開發。

在包含HDFO模塊的產品的初始規劃階段,重要的是要了解每個設備都可能被視為“定制”。雖然認證范圍可能包括正在考慮的整體模塊和封裝尺寸,但每個器件都有獨特的挑戰。因此,幾乎每個新設備都有測試車輛的迭代。隨著越來越多的測試車輛(TV)成功完成,并且更多可能的設計空間品種通過認證,有可能直接進入產品認證階段,但目前強烈建議使用 TV。

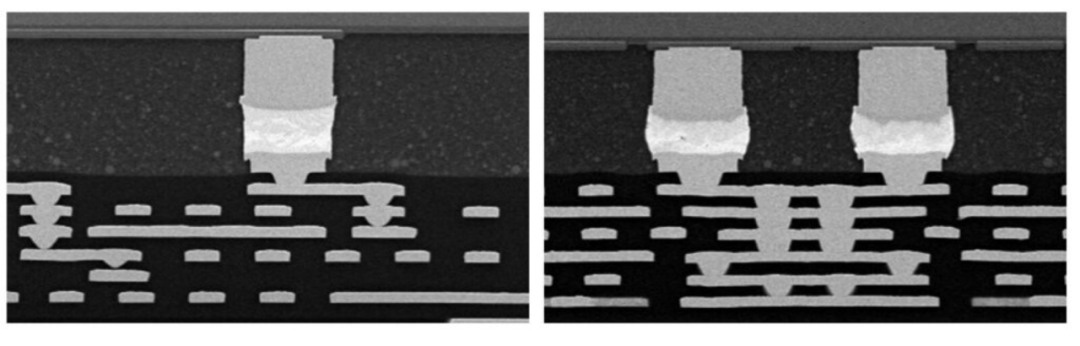

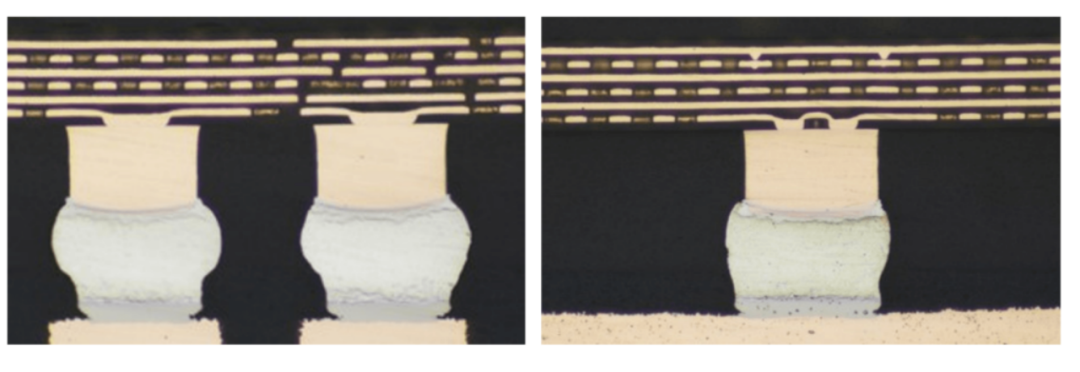

第一個通常使用TV。是菊花鏈芯片或至少是凸塊虛擬芯片,以允許發現模塊中多芯片布局的任何獨特特征。評估中介層載體和包覆成型晶圓級翹曲就是一個很好的例子。機械仿真可用于估計翹曲,但盡管可以模擬全晶圓級翹曲,但它對RDL中的金屬密度等也非常敏感。總是可以在模擬中確定趨勢,但最終評估需要通過實際TV來確定。由于TV的內部制造速度相對較快,因此可以快速根據真實數據校準模擬,以便在更改模型或者設備中的不同元素時可以了解趨勢。通過構建機械或菊花鏈TV,可以快速收集數據以了解任何工程工作需要集中在哪里。迄今為止,這已在許多TV結構中重復出現,并且是 Amkor 眾所周知的流程開發路徑。圖 2a 和 b 顯示了典型的TV方法。

圖 2a:連接到 HDFO 的測試車輛芯片。

圖 2b:連接到封裝基板的測試車輛 HDFO 模塊。

第二臺TV可以是另一個菊花鏈設備,或者在芯片中具有一些最小的功能或芯片封裝交互 (CPI) 測試結構。盡管芯片可能不具備完整的功能,但設計本身要么與功能設計類似,要么實際上就是功能設計。中介層 RDL 的設計通常在第一臺TV之前開始,因為芯片之間的小芯片接口仍然是客戶特定的。隨著設計規則的不斷改進,尋找最佳布線策略需要客戶和制造商之間的密切合作。根據產品的生產目標時間,可能會提供仍在開發中的更高級的設計規則,這將實現初始設計規則不允許的布線。每個客戶對設計流程都有自己的偏好。Amkor 嘗試滿足所有偏好,從僅接收中介層的成品圖形數據流 (GDS) 到管理整個設計流程。

HDFO 中介層設計流程通常從 Amkor 設計團隊在 Cadence(SIP/MCM 文件)或西門子 Expedition 中提供的入門數據庫開始。起始數據庫不是必需的,但會自動啟動標準設計規則和必要的設置,以與 Calibre 設計規則檢查 (DRC) 實現進行交互,從而節省時間。無論使用哪種電子設計自動化 (EDA) 工具,Amkor 還可以幫助設置這些參數。Calibre DRC 規則平臺可以由 Amkor 或客戶運行,因為它直接在從 EDA 工具導出的 GDS 上運行。

對于更大、更復雜的中介層,設計過程可能需要 4 到 12 周。自 Amkor 推出 SWIFT HDFO 技術以來,EDA 工具多年來得到了顯著改進。動態填充步驟的處理時間可能比大多數設計人員習慣的時間長得多,因此從一開始就預測生產計劃中的增加時間非常重要。這是由于設計中存在大量的引腳、跡線和形狀。脫氣通常是設計發布之前執行的最后操作,具體取決于所需的操作。Amkor 已開發出可以減少脫氣所需時間的方法,但對于大型設計,這可能需要數天的時間。

設計完成后,將其發布到 HDFO 生產線以啟動 RDL 構建過程。在制造第二臺TV的 HDFO 內插器時,通常會在第一臺TV上收集數據。這允許在第二臺TV上規劃任何所需的實驗設計 (DOE)。并非每個設備都需要 DOE,但這是至關重要的一步,以便在開始組裝第二臺TV之前可以標記并修復或改進。

第二個測試車輛通常用于封裝鑒定。HDFO 模塊已被證明非常堅固,通過了濕度敏感性測試 1 級 (MSL1) 和溫度循環、條件 C (TCC)(-65°C 至 +150°C)。一旦附著到基材上,更常見的是在 MSL 4 和溫度循環、條件 G(-40°C 至 +125°C)下進行評估,但使用壓力更大的 TCB(-55°C 至 125°C)進行 > 3000 個溫度循環也取得了成功。總體而言,就封裝可靠性而言,HDFO 已被證明是一種非常堅固的結構。針對大型封裝的標準高溫存儲 (HTS) 測試(150°C,1000 小時)和標準無偏高加速應力測試 (UHAST)(110°C,85% 相對濕度 (RH),264 小時)在封裝鑒定方面也未發現任何問題。

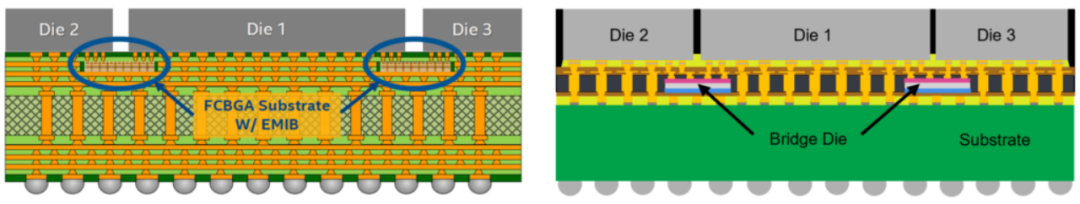

多年來,業界一直致力于研究利用橋接技術的方法。英特爾的嵌入式多芯片互連橋 (EMIB) 利用放置在有機基板內的橋來實現高密度布線,而無需使用硅中介層。Amkor 在這一領域的方法是將橋(硅或其他橋)嵌入到 HDFO 設計中,這為 HDFO 工具箱帶來了超高密度設計規則。Amkor 將此技術稱為 S-Connect。圖 3 顯示了這兩種設計技術的比較。

圖 3:(L) Intel EMIB(圖片由 Intel 提供)(R) Amkor S-Connect

與客戶和行業合作伙伴合作時,需要進行權衡分析,在硅中介層、有機 RDL HDFO 和 S-Connect 等橋接解決方案之間做出決定。使用橋的決定必須解決橋芯片(帶或不帶 TSV)和硅集成無源器件(如果有保證)的采購問題。最終客戶還考慮每個解決方案的整體生產準備情況和成熟度。硅中介層最為成熟,因為它們已進行大批量制造 (HVM) 多年,其次是已完成許多成功認證的有機 RDL 和 S-Connect。隨著系統變得更加復雜,集成的需求可能會迫使解決方案轉向橋接解決方案,例如 S-Connect。

橋梁技術的三個主要驅動因素。橋接技術通過包含用于小芯片到小芯片或芯片到芯片布線的基于硅的高密度布線橋,可以減少 RDL 數量,從而有可能降低系統成本。橋接技術還利用晶圓廠光刻技術,使布線密度低于 1 μm,從而有助于在硅頂部芯片上實現更精細的凸塊間距。最后,橋接技術的使用允許在同一 3D 位置(見圖 4)創造性地使用嵌入式硅集成無源器件 (IPD),直接放置在頂部芯片下方,以實現最佳功率傳輸。

HDFO 設計和制造可采用先芯片或后芯片配置。對于更簡單和更小的設計,芯片優先可能是合適的并且成本較低的方法。Amkor 的 S-Connect 設計主要路徑采用后芯片方法,以利用后芯片 HDFO 技術的專業知識,并盡量減少對客戶芯片的良率影響。

后模 S-Connect 結構由帶有預制高銅柱的基礎 RDL 組成。橋芯片和其他非橋芯片(包括 IPD)面朝上放置,并帶有較小的銅柱。晶圓被模制并平坦化以露出所有銅柱。芯片放置能力是一項關鍵的工藝要求,隨著任何給定產品中放置的面朝上橋芯片數量的增加,該能力變得更加復雜。然后使用有機 RLD 工藝(如 HDFO)執行額外的 RDL 處理,并提供用于芯片連接的芯片連接墊。然后通過第二次模具和模具研磨工藝完成晶圓上芯片組裝。然后將晶圓從載體上取下并翻轉進行背面處理,其中電鍍受控塌陷芯片連接 (C4) 銅柱。至此,模塊形成完成,并適合用于其他集成模塊的通用過程。

在考慮 S-Connect 而非其他形式的異構集成時,橋芯片采購是另一個關鍵方面。客戶可能要求橋接器還具有 TSV,以便為 I/O PHY 提供電源和接地。這些 TSV 承載橋芯片的采購和加工將使 S-Connect 模塊的晶圓級制造更加復雜。Amkor 擁有豐富的 TSV 工藝經驗,包括大量可供選擇的化學機械平坦化 (CMP)/背面鈍化配方,可最大程度地減少 TSV 軸承橋制備過程中所需的開發工作。

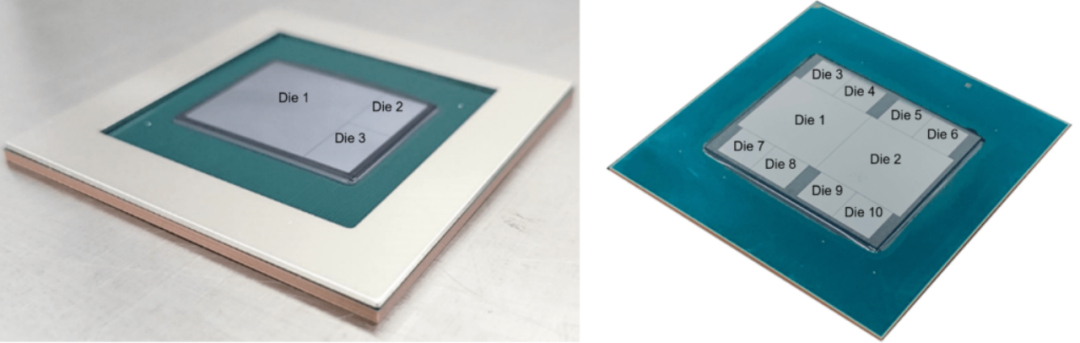

目前,有兩個內部TV用于 S-Connect 開發。三個芯片模塊的開發和內部鑒定已經完成,其中包括一個較大的芯片和兩個較小的芯片(如高帶寬內存 (HBM))。該模塊具有兩個橋芯片和多個測試芯片,用于模擬非 TSV 承載 IPD 芯片的放置。在更大規模上,模塊TV的開發正在使用 10 個頂部芯片和 10 個橋芯片。該演示針對的是非常大的模塊,這些模塊從硅橋芯片的使用中獲益最多。該TV預計將于 2023 年獲得可靠性結果。圖 4 顯示了兩臺 S-Connect 測試車輛。

圖 4:S-Connect 測試車輛的類型。

Amkor 一直在為異構集成的下一次發展做準備,我們相信,隨著需要更多集成,它將提供獨特的功能來增強 HDFO 和硅中介層解決方案。對于更大的中介層(>2500 mm2),橋接解決方案將有助于保持高良率,因為最高密度要求(以及最高的潛在良率損失)發生在橋上,而橋接已經具有極高的良率。

測試方法

自這些設計開始以來,Amkor 就一直為異構集成產品提供測試服務。設計和評估TV的系統方法使測試工程師能夠在產品投入使用之前針對設計的關鍵方面進行測試。

所有異構小芯片封裝都面臨一些共同的測試挑戰。小芯片互連完整性是一項重要的因素。向封裝內每個小芯片傳輸信號和電源需要在制造過程中進行仔細的布局、設計和測試。封裝材料類型影響小芯片和封裝級暴露的引腳之間的互連性能。這包括靜態連接質量、連續性、泄漏和瞬態交流時序、阻抗匹配和信號串擾。在精心設計的整體產品架構中,對產品所有功能方面的可測試性設計 (DFT) 訪問是一個重要的考慮因素。

由于小芯片溫度不均勻導致的熱梯度很常見。受控、管理和可重復的生產測試環境可確保為未來的產品設計迭代提供準確的反饋和一致的產量。

結論

使用 MCM 和古老的 2.5D TSV 硅中介層方法的異構集成已投入生產多年。向基于異構小芯片的集成的過渡才剛剛開始。

為了集成小芯片,典型的設計必須在芯片之間具有高帶寬接口,這通常需要精細的凸塊間距(≤55 μm)、高信號速率和短總線長度。HDFO 和 S-Connect 設計為這些集成提供了經濟高效的途徑。典型的設計小于 2500 mm2,但目前的趨勢是朝著更大尺寸和更高芯片數量發展。

對于較大的模塊,使用橋是有意義的。由于 RDL 產量,使用極細線 RDL 的大型模塊(>2500 mm2)成本會更高。使用極高產量的橋在芯片之間提供最精細的布線,并結合其他地方較低密度的 RDL,由于預期總產量較高,因此將是更好的經濟權衡。橋接封裝解決方案正在開發中,目標是在 2023 年和 2024 年獲得客戶資格。HDFO 小芯片集成已通過內部資格認證,HDFO 已準備好接受客戶參與和產品資格認證。針對異構集成產品的一流測試服務完善了整個制造過程。

-

芯片

+關注

關注

455文章

50817瀏覽量

423683 -

模塊

+關注

關注

7文章

2707瀏覽量

47477 -

封裝

+關注

關注

126文章

7903瀏覽量

142967

原文標題:異構IC封裝:構建基礎設施

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

開源基礎設施能力建設分論壇成功舉辦

智能駕駛所需的基礎設施

微軟貝萊德成立AI基礎設施投資基金

中科馭數:DPU是構建高效智算中心基礎設施的必選項

三星攜手紅帽成功構建全球首個CXL認證基礎設施

三星電子宣布成功構建其首個紅帽認證的CXL基礎設施

聯想全棧算力基礎設施發布 躋身中國第一陣營再啟新程

聯想發布全棧算力基礎設施新品

數字新時代的關鍵--IPv6 與數據基礎設施建設

異構IC封裝:構建基礎設施

異構IC封裝:構建基礎設施

評論