關(guān)鍵要點(diǎn)

關(guān)鍵要點(diǎn)

將復(fù)雜的電路理解為串聯(lián)和并行連接的組合。

線性的概念及其在電路分析中的應(yīng)用。

用來快速有效地表示等效電路的附加方法。

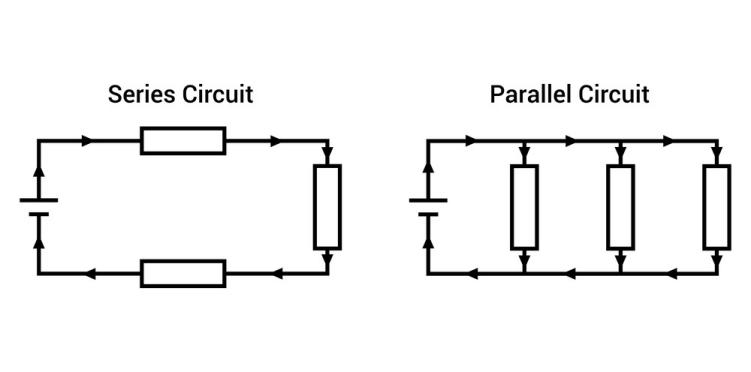

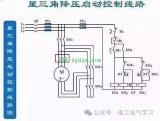

復(fù)雜電路包括串聯(lián)和并聯(lián)元件,在這里分別顯示

電路設(shè)計(jì)是一門廣泛的學(xué)科,它結(jié)合了許多數(shù)學(xué)分析和電磁學(xué)的方法。在該理論發(fā)展的早期,設(shè)計(jì)師會(huì)遇到電路的基本構(gòu)建模塊以及電路簡(jiǎn)化的入門協(xié)議。雖然這些是電路的基礎(chǔ),并且?guī)缀踹m用于任何電路,但還有很多情況需要更復(fù)雜的描述。復(fù)雜的電路提供了一個(gè)額外的挑戰(zhàn),因?yàn)樗鼈冃枰呒?jí)的技術(shù)才能得到一個(gè)可以通過人類或機(jī)器進(jìn)行分析的網(wǎng)絡(luò)。學(xué)習(xí)這些程序?yàn)樵O(shè)計(jì)師提供了更多的電路分析機(jī)制,并更全面地理解了網(wǎng)絡(luò)設(shè)計(jì)。

節(jié)點(diǎn)分析:串聯(lián)和并聯(lián)連接

節(jié)點(diǎn)分析:串聯(lián)和并聯(lián)連接

在任何新興工程師的工具箱中,等效電路簡(jiǎn)化都是最重要的解決方法之一。將復(fù)雜電路網(wǎng)絡(luò)簡(jiǎn)化為單一的代表性電路元件的能力是電路建模和分析的核心方法。首先,定義電路拓?fù)涞囊粋€(gè)基本方面十分重要:串聯(lián)和并聯(lián)。理解這些相關(guān)概念的最佳方法是跟蹤電流的流動(dòng):

串聯(lián):電流流經(jīng)電路中的元件時(shí),它們會(huì)連成一條線,沒有任何分支。換句話說,該特定電路或子電路中不存在分支電流路徑。在網(wǎng)絡(luò)分析方面,連續(xù)串聯(lián)的元件共享一個(gè)節(jié)點(diǎn)或參考點(diǎn)。

并聯(lián):電流從源頭分配到多個(gè)分支路徑上。對(duì)于任何有兩個(gè)端口的并聯(lián)元件,兩個(gè)節(jié)點(diǎn)都與其它并聯(lián)的兩個(gè)端口元件共通。

除了基礎(chǔ)電路之外, 幾乎很少有完全串聯(lián)或并聯(lián)的整體電路。相反, 大多數(shù)電路包含不同數(shù)量的串聯(lián)和并聯(lián)元件,以利用這兩種連接方法的不同性能特征。復(fù)雜的電路,或包含并聯(lián)和串聯(lián)元件的電路,更為常見。在分析方面,評(píng)估一個(gè)由串聯(lián)元件組成的電路通常比一個(gè)并行電路更直接,盡管這個(gè)規(guī)則有明顯的組件例外。大多數(shù)級(jí)數(shù)元素都是單個(gè)元素的總和——為了找到純級(jí)數(shù)網(wǎng)絡(luò)的阻力,只需添加循環(huán)中包含的值。平行元素的和不那么直觀:平行相加,取單個(gè)分量的倒數(shù)和的倒數(shù)。如所描述的串聯(lián)和并聯(lián)計(jì)算都適用于電阻器和電感器,但電容器是該框架的一個(gè)顯著的例外。雖然電容器確實(shí)有規(guī)律地和相互求和,但它們的應(yīng)用是交換的:串聯(lián)電容器相互求和,而傳統(tǒng)的并聯(lián)電容器相互求和。在分析電路時(shí),盡管有明顯的組件例外,評(píng)估由串聯(lián)元件組成的電路通常比并聯(lián)電路更為直觀。大多數(shù)串聯(lián)元件是各個(gè)元素的總和:要找到純串聯(lián)網(wǎng)絡(luò)的電阻,只需將循環(huán)內(nèi)包含的值相加即可。并聯(lián)元件的總和則不那么直觀:要進(jìn)行并聯(lián),需要對(duì)各個(gè)組件的倒數(shù)之和取倒數(shù)。上述串聯(lián)和并聯(lián)計(jì)算適用于電阻器和電感器,但電容器則例外。雖然電容器通常可以進(jìn)行常規(guī)的倒數(shù)求和,但它們的應(yīng)用是相反的:串聯(lián)電容器進(jìn)行倒數(shù)求和,而并聯(lián)電容器則進(jìn)行常規(guī)求和。

使用基爾霍夫定律進(jìn)行節(jié)點(diǎn)分析

使用基爾霍夫定律進(jìn)行節(jié)點(diǎn)分析

也可以從電壓和電流方面分析串聯(lián)和并行配置。串聯(lián)組件,作為同一分支,具有相同的電流,但在每個(gè)非源電路元件的電壓降,如基爾肖夫的環(huán)路定律概述。同時(shí),由于基爾肖夫的結(jié)規(guī)則,并聯(lián)組件具有相同的電壓,但有不同的電流,即進(jìn)入一個(gè)節(jié)點(diǎn)的總電流必須等于一個(gè)節(jié)點(diǎn)的總電流。更正式地說,串聯(lián)元件和并聯(lián)元件可以分別被描述為分壓器和分流器。這些電路操作根據(jù)組件的相對(duì)值提供電壓或電流的比例分布;例如,兩個(gè)相同的電阻會(huì)經(jīng)歷相同的電壓降(串聯(lián))或相同的電流(并聯(lián)),因?yàn)樗鼈兊碾娮铻?:1值。對(duì)于不同的值,較大(或最大)的元件代表電流或電壓的最大比例,反之亦然。在電路中,我們可以通過電壓和電流的角度來分析串聯(lián)和并聯(lián)配置。如基爾霍夫環(huán)路定律所述,串聯(lián)元件在同一電路中,擁有相同的電流,但每個(gè)非提供電流的電路元件都會(huì)產(chǎn)生一定的電壓降。與此同時(shí),并聯(lián)元件擁有相同的電壓,但由于基爾霍夫節(jié)點(diǎn)定律所示,不同的電流會(huì)進(jìn)入和流出節(jié)點(diǎn),使它們的電流不同。從更正式的角度講,串聯(lián)和并聯(lián)元件可以被描述為電壓分壓器和電流分流器,分別提供基于元件相對(duì)值的電壓或電流的比例分配;例如,兩個(gè)相同的電阻器在串聯(lián)時(shí)將經(jīng)歷相同的電壓降,而在并聯(lián)時(shí)將經(jīng)歷相同的電流,因?yàn)樗鼈兙哂?:1的電阻值。

復(fù)雜電路簡(jiǎn)化的構(gòu)建

復(fù)雜電路簡(jiǎn)化的構(gòu)建

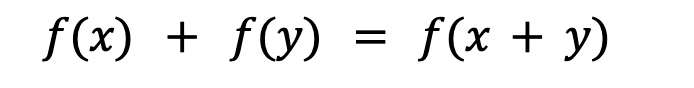

復(fù)雜性的話題需要與線性和疊加相結(jié)合。線性描述了系統(tǒng)的整體行為,即從輸入到輸出的映射,而疊加是線性系統(tǒng)的決定條件。為了保持疊加,系統(tǒng)必須在整個(gè)輸入范圍內(nèi)維持可加性和齊次性:可加性 :兩個(gè)單獨(dú)輸入的組合輸出與組合輸入的總和輸出相同。更常見的是,可以表示為等式:

*假設(shè)x和y是f域內(nèi)的元素。

齊次性:輸入端的標(biāo)量乘以某個(gè)值,等價(jià)于輸出端相應(yīng)標(biāo)量乘以該值。同樣,這需要一個(gè)更常見的等式:

f (sx) = sf (x)

*對(duì)于所有元素s,x在f的域內(nèi)。

回到一個(gè)電路的復(fù)雜性,疊加,特別是可加性特性,是一個(gè)系統(tǒng)的輸入和輸出之間的關(guān)系。復(fù)雜電路是并行元素和串聯(lián)元素的混合物,它們的解代表了這兩種連接方法的適當(dāng)貢獻(xiàn)。為了進(jìn)一步推動(dòng)這種關(guān)系,復(fù)雜電路代表了平行和串聯(lián)元件的組成,在非正式和數(shù)學(xué)上;在節(jié)點(diǎn)分析的背景下,電氣工程師參考疊加理論,以區(qū)分更一般和數(shù)學(xué)的疊加原理的彎曲。這兩個(gè)元素的組合形成了疊加原理的基礎(chǔ)并定義了一個(gè)線性系統(tǒng)。總體而言,線性的適用范圍有限,是對(duì)系統(tǒng)真實(shí)行為的簡(jiǎn)化,但在它適用的情況下,它是一種強(qiáng)有力的工具來建模。有利的是,線性系統(tǒng)可以用各種數(shù)學(xué)函數(shù)、變換和算子來分析,并且比非線性系統(tǒng)更容易求解。回到電路的復(fù)雜性,疊加原理,特別是可加性特性,是系統(tǒng)輸入和輸出之間的關(guān)系。如前所述,復(fù)雜電路是并聯(lián)和串聯(lián)元素的組合,并且它們的解決方案代表了兩種連接方法的結(jié)合。

評(píng)估不那么直觀的網(wǎng)絡(luò)

評(píng)估不那么直觀的網(wǎng)絡(luò)

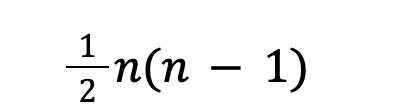

事實(shí)上,許多網(wǎng)絡(luò)可以通過串聯(lián)求和并行求和。人工分析應(yīng)緩慢而仔細(xì)地進(jìn)行,以確定兩個(gè)元素之間的關(guān)系,以及適當(dāng)?shù)捻樞颍栽谟?jì)算中保留串聯(lián)或并聯(lián)組件的性質(zhì)。然而,并不是每一種電路排列都易于串聯(lián)或并聯(lián)的識(shí)別,需要利用各種轉(zhuǎn)換來更好地說明電路內(nèi)的關(guān)系。一般來說,星形變換多邊形用于減少特定電路中的節(jié)點(diǎn)數(shù)量,盡管其實(shí)現(xiàn)有一個(gè)實(shí)際的限制,即元素的替換數(shù)量受到以下限制:

*對(duì)于n個(gè)元素?cái)?shù)。

最有用的情況是當(dāng)n = 3時(shí),因?yàn)檗D(zhuǎn)換后的網(wǎng)絡(luò)具有與原始網(wǎng)絡(luò)相同數(shù)量的元素,但也應(yīng)該提到其他值。使用小于3個(gè)元素的轉(zhuǎn)換將生成具有更少組件的模型,而使用大于3個(gè)元素的轉(zhuǎn)換將增加組件的總數(shù),同時(shí)減少節(jié)點(diǎn)數(shù)。前者的使用范圍有限,而后者只會(huì)使分析復(fù)雜化。回到特殊的n = 3的情況下,在一些情況下,設(shè)計(jì)師可能會(huì)遇到非正統(tǒng)的網(wǎng)絡(luò)結(jié)構(gòu)。雖然在捕獲的示意圖中不太常見,但它們?nèi)匀豢梢栽谌齻€(gè)元素的節(jié)點(diǎn)交點(diǎn)上找到,比如在橋中發(fā)現(xiàn)的那些元素。這些轉(zhuǎn)換的形式上是基于網(wǎng)絡(luò)的視覺形狀的Y-Δ(delta)或T-π(pi)轉(zhuǎn)換,它們利用組件之間的級(jí)數(shù)和并行關(guān)系來創(chuàng)建所有三個(gè)元素之間的比例。刪除節(jié)點(diǎn)允許將電路重新解釋為串聯(lián)或并聯(lián)連接,進(jìn)一步強(qiáng)調(diào)了在復(fù)雜電路分析中進(jìn)行變換的優(yōu)勢(shì)。

Δ-Y變換通常與三相電力系統(tǒng)有關(guān)

進(jìn)一步降低復(fù)雜性的等效電路模型

進(jìn)一步降低復(fù)雜性的等效電路模型

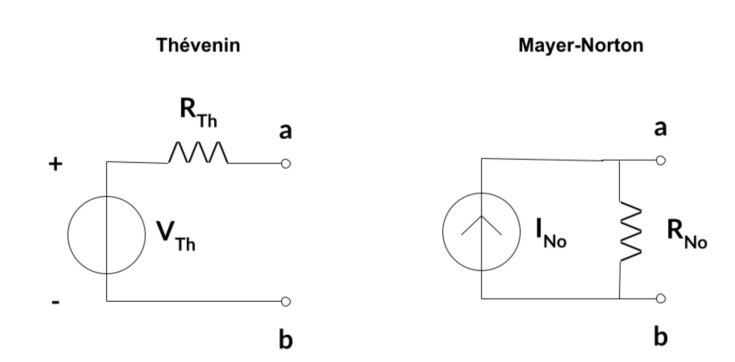

復(fù)雜電路的簡(jiǎn)化有時(shí)需要使用額外的算法來產(chǎn)生可工作的拓?fù)浣Y(jié)構(gòu)。最初為由電流源、電壓源和電阻器組成的線性直流電路設(shè)計(jì)的這兩種方法,可通常適用于固定頻率的線性交流電路:費(fèi)溫定律:將電路替換為一個(gè)等效電壓源和串聯(lián)電阻,測(cè)量開路電壓。將電路轉(zhuǎn)換為費(fèi)溫定理等效電路的三個(gè)步驟如下:

1. 確定等效電壓(Vth),即輸出端測(cè)量的電壓。通常,這是通過使用已知的源電壓和電壓分壓計(jì)算來確定留在輸出端的源電壓的分?jǐn)?shù)來實(shí)現(xiàn)的。注意,打開電路(其中負(fù)載與等效電路隔離)會(huì)導(dǎo)致某些支路沒有電流流動(dòng)。

2. 通過從輸出端子的電路來確定等效電阻(Rth)。這個(gè)電阻是通過假設(shè)所有電源的理想電阻,即電壓源的理想電阻為零,電流源的理想電阻為無窮大,并將它們分別替換為開路和短路。

3. 最后,費(fèi)溫等效電路可以用Vth的電壓源和Rth的串聯(lián)電阻來表示。

Mayer-Norton電路理論-用等效電流源和并聯(lián)電阻(從負(fù)載角度)替代電路。作為Thévenin等效性的對(duì)立面,實(shí)現(xiàn)Mayer-Norton等效電路需要遵循三個(gè)步驟:

1.通過在負(fù)載處短路終端來找到等效電流(Ino)。首先找到總電流(通常使用歐姆定律,但其他方法也可獲得更快的結(jié)果)。一旦找到總電流,則計(jì)算輸出短路電流。

2.與Thévenin等效電路一樣,通過用短路和開路替換源,從輸出端評(píng)估等效電阻。

3.從負(fù)載處觀察,Mayer-Norton等效電路顯示為電流源Ino和并聯(lián)電阻Rth。

Thévenin和Mayer-Norton代表一種雙重方法,通常在電子學(xué)中看到,其中任一使用互補(bǔ)的模式提供等效性。盡管線性電路只占工程師和設(shè)計(jì)師將遇到的拓?fù)浣Y(jié)構(gòu)的一小部分,因?yàn)榉峡蚣艿脑O(shè)備數(shù)量有限,但等效電路具有相關(guān)源的附加用例。通常,當(dāng)確定等效電壓或電流時(shí),電壓和電流源將被替換為短路和開路,但不能輕易忽略相關(guān)源。相反,設(shè)計(jì)師可以將測(cè)試源連接到輸出端,并計(jì)算所得到的電流或電壓。

兩種等效電路模型的比較。

復(fù)雜電路簡(jiǎn)化存在的目的是為工程師和設(shè)計(jì)師提供各種算法,以簡(jiǎn)化電路設(shè)計(jì)過程。能夠用簡(jiǎn)單的實(shí)踐方法測(cè)量廣泛網(wǎng)絡(luò)的響應(yīng),極大地提高了網(wǎng)絡(luò)分析的可讀性。此外,這些方法構(gòu)成了電子節(jié)點(diǎn)分析的基礎(chǔ),這對(duì)電路模擬非常必要。

Cadence的PCB設(shè)計(jì)和分析軟件提供了全面的設(shè)計(jì)和分析工具包,具備滿足最嚴(yán)格的板子規(guī)格的廣泛功能。對(duì)于布局,OrCAD PCB Designer提供了強(qiáng)大的功能,可以滿足當(dāng)今全功能板的需求,并推動(dòng)未來設(shè)計(jì)的創(chuàng)新。Cadence Allegro PCB Designer是一個(gè)完整的、高性能印制電路板設(shè)計(jì)套件。通過頂尖的技術(shù),它為創(chuàng)建和編輯復(fù)雜、多層、高速、高密度的印制電路板設(shè)計(jì)提供了一個(gè)交互式、約束驅(qū)動(dòng)的設(shè)計(jì)環(huán)境。它允許用戶在設(shè)計(jì)過程的任意階段定義、管理和驗(yàn)證關(guān)鍵的高速信號(hào),并能抓住今天最具挑戰(zhàn)性的設(shè)計(jì)問題。AllegroPCB Designer提高了設(shè)計(jì)效率和縮短設(shè)計(jì)周期,讓你的產(chǎn)品盡快進(jìn)入量產(chǎn)。

-

電路

+關(guān)注

關(guān)注

172文章

5947瀏覽量

172585 -

電路分析

+關(guān)注

關(guān)注

62文章

518瀏覽量

98864 -

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6678文章

2459瀏覽量

204912

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

射頻分析儀的技術(shù)原理和應(yīng)用場(chǎng)景

buck電路的穩(wěn)定性分析方法

用于動(dòng)態(tài)穩(wěn)定性分析的直流電機(jī)建模的簡(jiǎn)化方法

放大電路的基本分析方法有哪兩種

放大電路動(dòng)態(tài)分析的基本方法

對(duì)放大電路的分析方法介紹

受控電壓源在戴維南定理中的應(yīng)用

微變等效電路和小信號(hào)等效電路分析方法的區(qū)別

信號(hào)分析的方法有哪些

藍(lán)牙技術(shù)聯(lián)盟發(fā)布《2024年藍(lán)牙市場(chǎng)最新資訊》

電路仿真分析的方法步驟

含耦合電感的電路分析方法有哪些

放大電路有哪三種基本分析方法?舉例說明

對(duì)干如下所示復(fù)雜網(wǎng)絡(luò)的電路該如何分析?

復(fù)雜電氣電路圖的查看方式

技術(shù)資訊 | 復(fù)雜電路分析與簡(jiǎn)化方法

技術(shù)資訊 | 復(fù)雜電路分析與簡(jiǎn)化方法

評(píng)論