變量的賦值

在轉換中執行賦值時,所使用的值有明顯的區別。在下面的表達式中

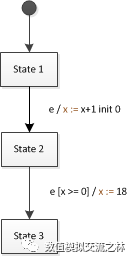

藍色部分表示引發事件(也就是常說的e)時的值,綠色部分表示執行所有激活鏈后將更新的值。對于以下狀態圖:

當處于狀態 1 并引發事件 e 時,執行將按如下方式發生:

- 轉到狀態 2,更新 x 的未來值。

- 檢查優先級為 1 的轉換,x 仍等于 0;無法進行過渡。

- 檢查優先級為 2 的轉換,該轉換為空且始終為 true;可以進行轉換,轉到狀態 4。

- 激活鏈結束,x 的未來值成為它的實際值,所以 x 的值變成 1,我們停留在狀態 4。

感興趣的小伙伴可以思考一下為什么是狀態4而不是狀態3

賦值更新激活鏈末尾的變量或離散輸出的值。因此,當相同的值被分配兩次時,就會出現問題,我們應該使用哪一個?

x 的值應該是 1 還是值 18?為避免狀態圖執行的歧義,禁止對激活鏈中的變量進行多次更新。為了打破鏈條,您必須為其中一個轉換添加一個觸發器:

這樣,狀態 2 和狀態 3 之間的轉換就不會直接進行;在重新更新變量 X 之前,必須在狀態 2 中引發事件 E。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

轉換器

+關注

關注

27文章

8742瀏覽量

147841 -

信號處理器

+關注

關注

1文章

254瀏覽量

25334 -

觸發器

+關注

關注

14文章

2003瀏覽量

61303 -

有限狀態機

+關注

關注

0文章

52瀏覽量

10363 -

AMESIM

+關注

關注

1文章

15瀏覽量

11743

發布評論請先 登錄

相關推薦

什么是有限狀態機呢

在嵌入式,機器人領域,由于多的復雜邏輯狀態,我們編寫程序的時候不得不考慮很多種情況,容易造成功能間的沖突。有限狀態機(finite-state machine),簡稱狀態機,是一種表示

發表于 12-20 06:51

基于VHDL的MTM總線主模塊有限狀態機設計

為了能夠更簡潔嚴謹地描述MTM總線的主模塊有限狀態機的狀態轉換,同時減少FPGA芯片功耗,提高系統穩定性,文中在分析MTM總線結構和主模塊有限狀態機模型的基礎上,基于VHDL語言采

發表于 05-29 15:39

?20次下載

有限狀態機的建模與優化設計

本文提出一種優秀 、高效的 Verilog HDL 描述方式來進行有限狀態機設計 介紹了 有限狀態機的建模原則 并通過一個可綜合的實例 驗證了 該方法設計的

發表于 03-22 15:19

?1次下載

VHDL有限狀態機設計-ST

EDA的有限狀態機,廣義而言是指只要涉及觸發器的電路,無論電路大小都可以歸結為狀態機。有限狀態機設計在學習EDA時是很重要的一章。

發表于 06-08 16:46

?3次下載

初學者對有限狀態機(FSM)的設計的認識

有限狀態機(FSM)是一種常見的電路,由時序電路和組合電路組成。設計有限狀態機的第一步是確定采用Moore狀態機還是采用Mealy

發表于 02-11 13:51

?4359次閱讀

如何使用FPGA實現序列檢測有限狀態機

有限狀態機是絕大部分控制電路的核心結構, 是表示有限個狀態以及在這些狀態之間轉移和動作等行為的數學模型。有限狀態機是指輸出取決于過去輸入部分

發表于 11-04 17:17

?12次下載

有限狀態機設計是HDL Designer Series的關鍵應用

有限狀態機的設計是HDL Designer Series?工具的關鍵應用。 盡可能地對于設計人員編寫導致狀態機性能不佳的VHDL,可以使用HDL Designer用于生成VHDL的Series?工具

發表于 04-08 10:05

?6次下載

基于事件驅動的有限狀態機介紹

? 一、介紹 EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。 EFSM的設計

基于事件驅動的有限狀態機介紹

EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。

一個基于事件驅動的有限狀態機

EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。 EFSM的設計原則是:簡單!EFSM的使用者只需要關心:

有限狀態機變量賦值的一些小概念

有限狀態機變量賦值的一些小概念

評論