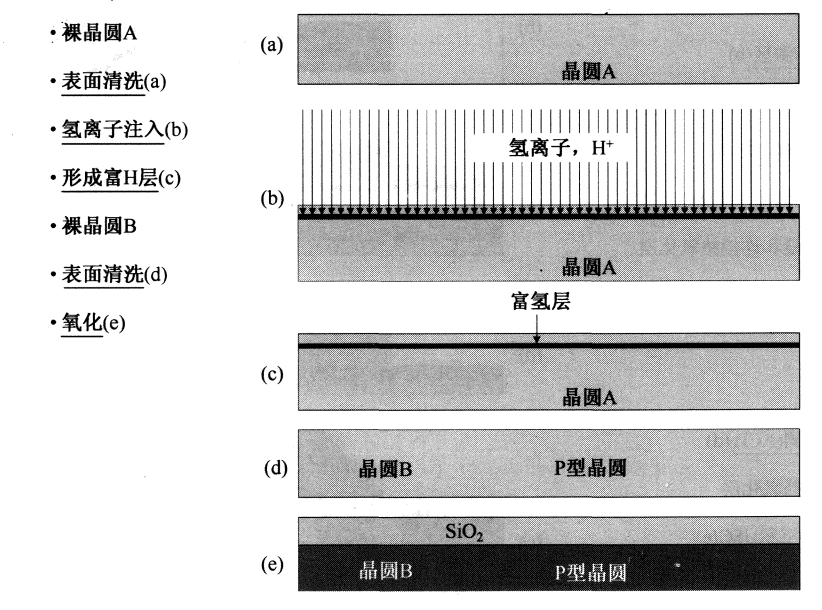

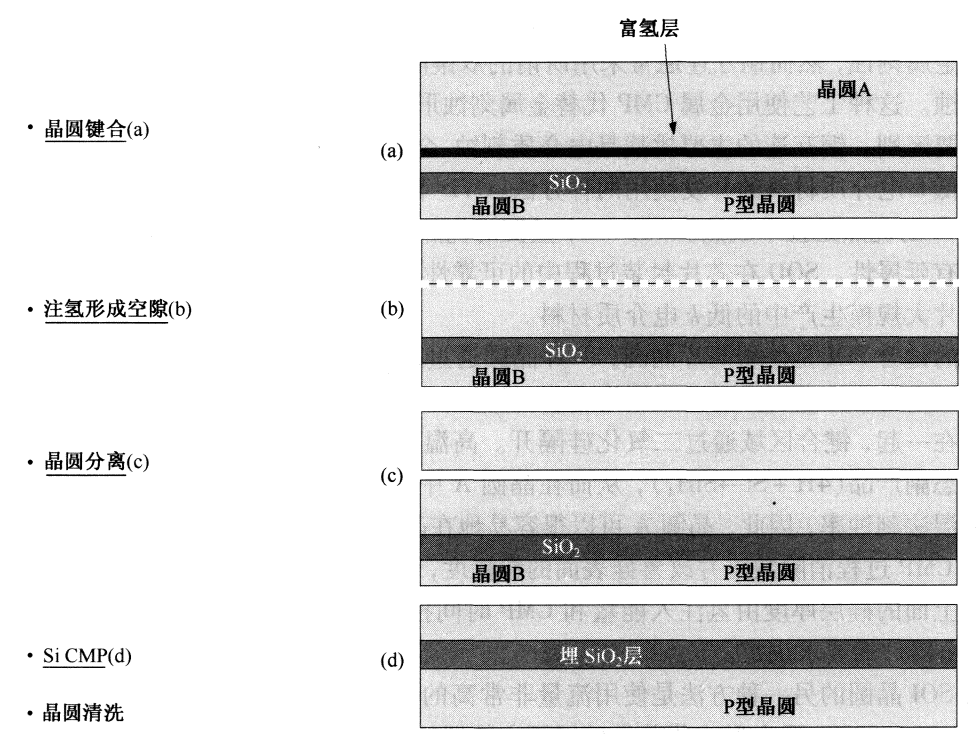

所謂的鍵合SOI是使用兩片晶圓,一片晶圓通過高電流氫離子注入在硅表面以下形成富氫層,另一片晶圓在硅表面生長二氧化硅層(見下圖)。然后,兩片晶圓面對面在高溫下擠壓并鍵合在一起,鍵合區域通過二氧化硅隔開。高溫條件下,晶圓A中的氫原子與硅原子反應形成氣態副產品(4H+SirSiH4),從而在晶圓A中形成空洞,形成的空洞使得富氫層具有非常高的濕法刻蝕率,因此,晶圓A可以很容易地在晶圓濕法刻蝕過程中和鍵合的晶圓分開。然后應用CMP過程消除缺陷并改善硅表面的粗糙度,使其非常平整和光滑(見下圖)。埋二氧化硅層上面的硅層厚度由氫注入能量和CMP時間控制。它的范圍從幾百納米到10納米左右,具體由器件的要求決定。

形成SOI晶圓的另一種方法是使用流量非常高的氧離子注入硅表面以下形成富氧層。通過高溫(大于1200攝氏度)退火形成薄單晶硅層下方的埋氧層。使用外延技術在晶圓表面生長外延硅,可以防止影響器件速度的氧污染。

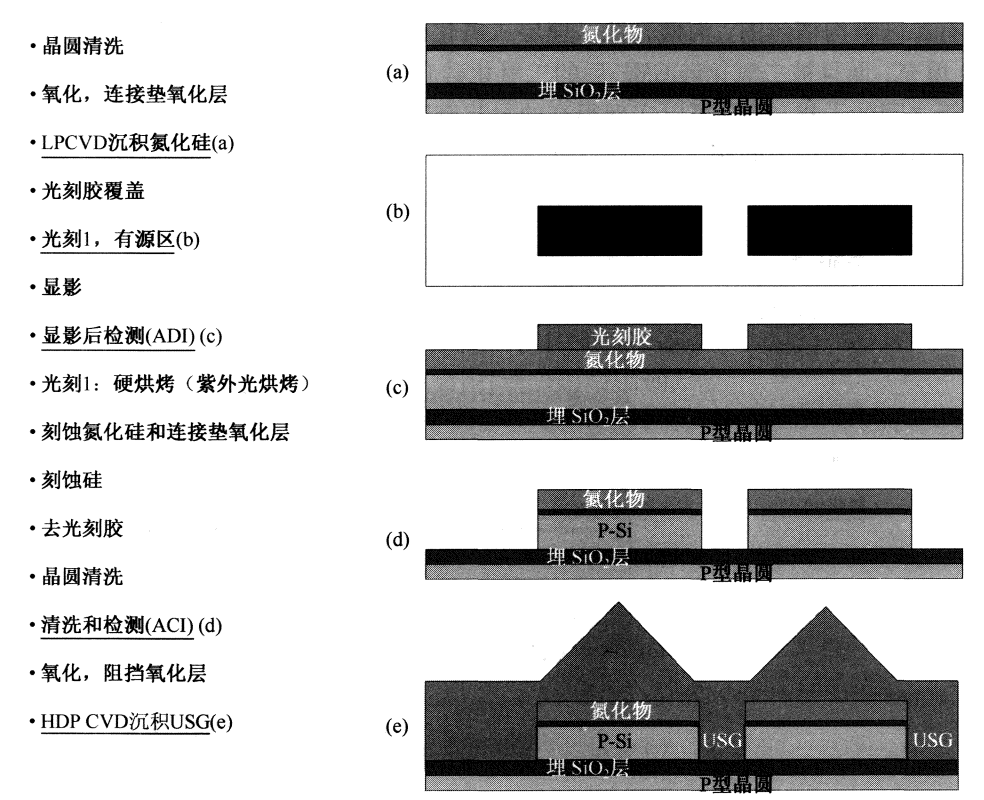

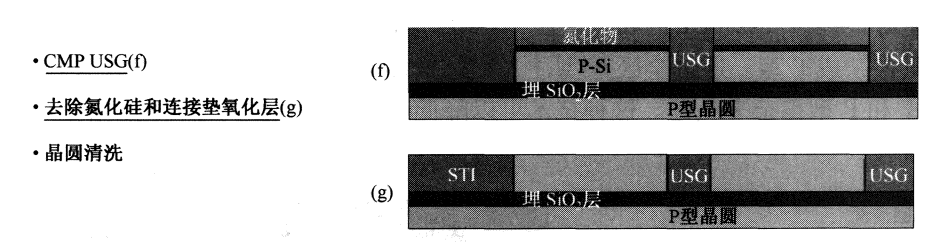

由于有源區被溝槽包圍,溝槽刻蝕了埋層二氧化硅,如圖下圖(d)所示。這樣器件就被溝槽CVD填充,而且被二氧化硅CMP后的二氧化硅介質完全隔離。這種完全隔離徹底消除了鄰近晶體管之間的干擾,并且可以實現很高的封裝密度,從而解決了隨著器件尺寸進一步縮小而形成的輻射誘發軟誤差問題。

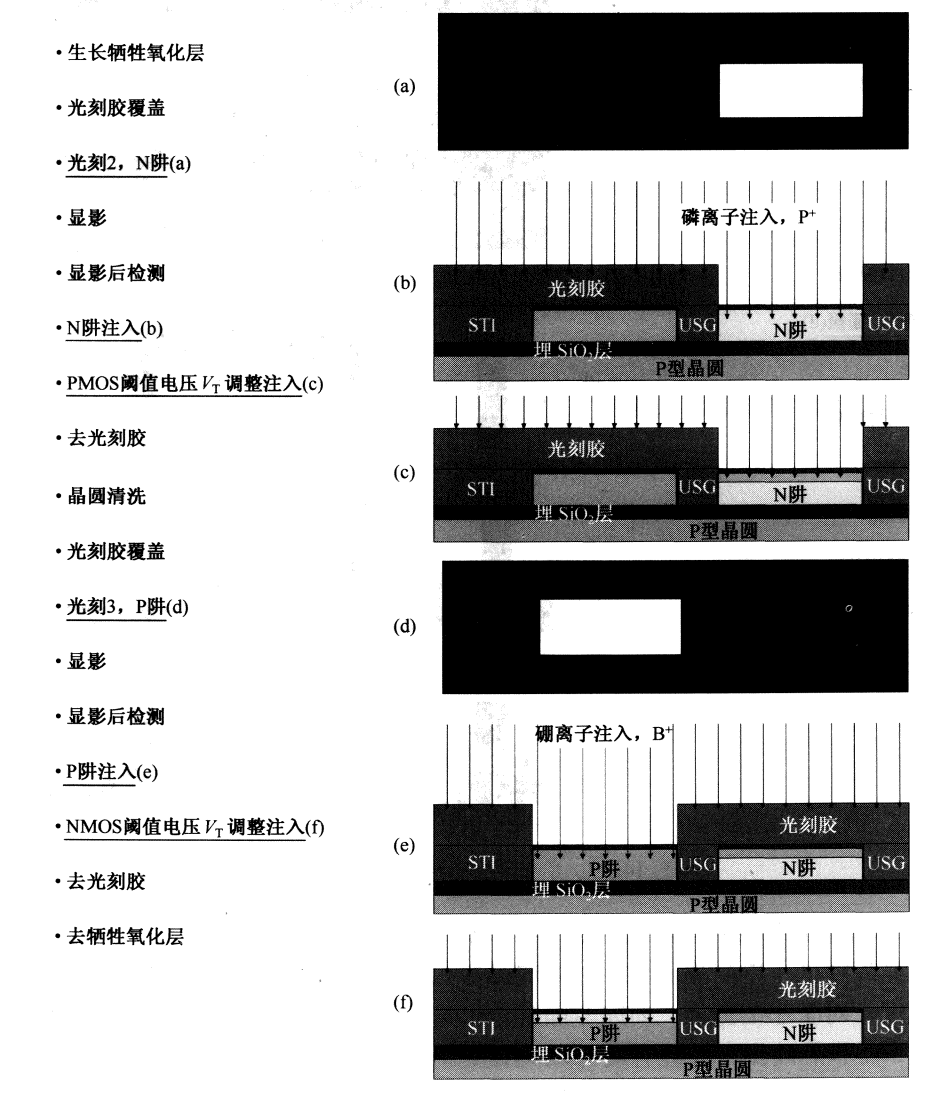

由于特征尺寸的縮小,N阱和P阱的結深都必須減小。因此,現有的高能量離子注入可以直接注入摻雜物而不再需要阱區形成中的擴散過程。通常需要不同能量水平的多次注入過程形成阱區。缺少了阱區形成的擴散過程(在這個過程中,高溫下離子熱擴散進入襯底),工程師可以使用相同的光刻版進行阱區和VT調整離子注入(見下圖).由于離子注入可以利用磁質譜儀精確地選擇所需的離子種類,所有注入過程都可以利用高能量、低電流的注入機在一道工序下完成。

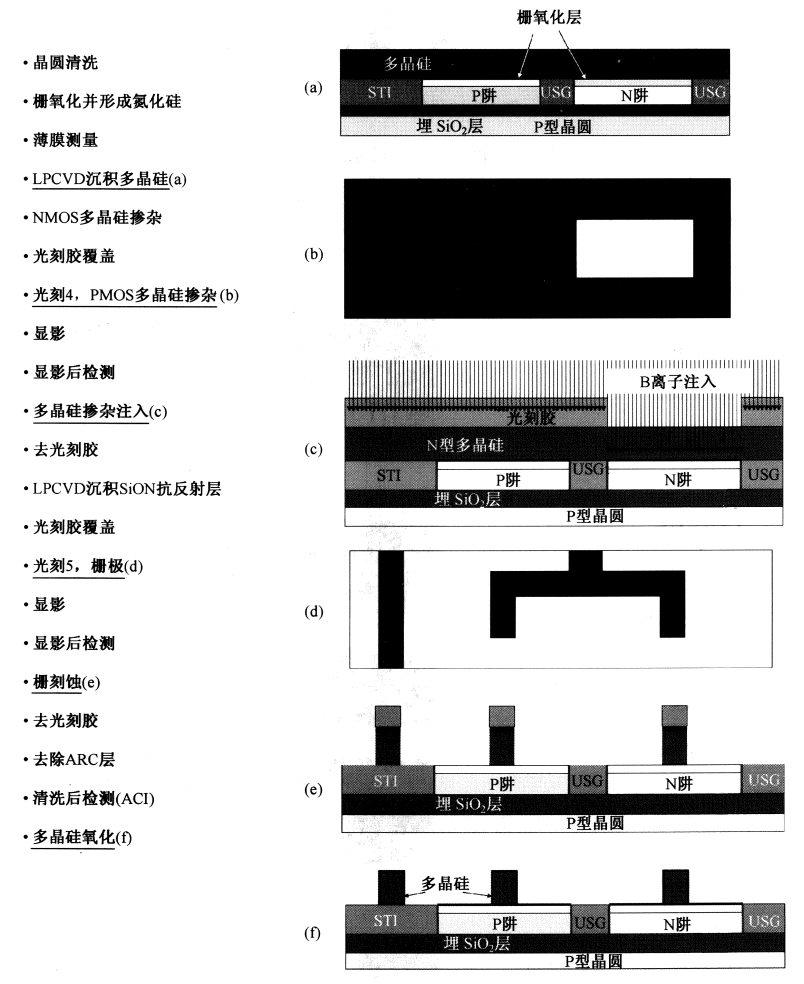

為了更好地控制MOSFET的閾值電壓,NMOS多晶硅柵需要重摻雜成N型,而PMOS多晶硅柵需要重摻雜成P型。通過全區N型注入和選擇性P型離子注入后,可以只利用一個光刻版實現N型和P型摻雜多晶硅。這種技術可以降低生產成本并提高器件的產量。

一些低k電介質材料的開發使用兩種方法:CVD和自旋電介質(S0D)。基于CVD低左電介質SiCOH的優點是技術成熟。SOD一個重要的優點是對如多孔二氧化硅低介電常數(k<2)的材料具有延展性。SOD在芯片封裝過程中的可靠性問題最終決定了CVDSiCOH成為先進集成電路芯片大規模生產中的低k電介質材料。

多晶硅由許多單晶硅單元組成,這種單元稱為晶粒。晶粒尺寸越大越好,因為大的晶粒形成小的晶粒晶界降低了電阻率。然而,大的晶粒尺寸可能會導致多晶硅刻蝕后側壁間隔層高的表面粗糙度。對于小的柵極,刻蝕非晶硅(a-Si)然后退火形成多晶硅。重摻雜多晶硅可以形成非晶硅,而非晶硅比多晶硅有更好的刻蝕輪廓控制。非晶硅退火后形成的多晶硅晶粒尺寸也較LPCVD沉積形成的多晶硅一致性好。柵極刻蝕后,等離子體注入引起的柵氧化層損壞可以通過退火過程中多晶硅氧化修復。

審核編輯:劉清

-

MOSFET

+關注

關注

147文章

7201瀏覽量

213625 -

半導體

+關注

關注

334文章

27515瀏覽量

219805 -

CMP

+關注

關注

6文章

151瀏覽量

26051 -

ICT技術

+關注

關注

0文章

44瀏覽量

10185 -

NMOS管

+關注

關注

2文章

121瀏覽量

5491

原文標題:半導體行業(一百九十四)之ICT技術(四)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

半導體行業之ICT技術介紹(四)

半導體行業之ICT技術介紹(四)

評論