AI芯片的技術(shù)架構(gòu)可以根據(jù)其設(shè)計(jì)方式和特點(diǎn)進(jìn)行分類。以下是幾種常見的AI芯片技術(shù)架構(gòu):

1. GPU(圖形處理器)架構(gòu):GPU最初是用于圖形渲染和游戲處理的,但由于其高度并行的特性,逐漸被應(yīng)用于深度學(xué)習(xí)計(jì)算。GPU架構(gòu)采用多個(gè)計(jì)算單元(CUDA核心)進(jìn)行并行計(jì)算,能夠高效地執(zhí)行浮點(diǎn)運(yùn)算和矩陣計(jì)算。NVIDIA的Tensor Core技術(shù)進(jìn)一步優(yōu)化了GPU的深度學(xué)習(xí)計(jì)算能力。

2. FPGA(現(xiàn)場可編程門陣列)架構(gòu):FPGA是一種可以根據(jù)需要編程和重新配置的硬件。AI芯片中的FPGA架構(gòu)允許開發(fā)者將深度學(xué)習(xí)模型轉(zhuǎn)換為硬件電路,以實(shí)現(xiàn)高度定制化和低功耗的計(jì)算。FPGA具有可重構(gòu)性,可以根據(jù)需要靈活調(diào)整電路結(jié)構(gòu)。

3. ASIC(專用集成電路)架構(gòu):ASIC是指專門為特定應(yīng)用設(shè)計(jì)和制造的定制芯片。AI芯片中的ASIC架構(gòu)基于特定的深度學(xué)習(xí)算法和網(wǎng)絡(luò)結(jié)構(gòu)進(jìn)行優(yōu)化,通過專用硬件實(shí)現(xiàn)高效計(jì)算和推理。ASIC通常能夠提供更高的性能和能效比,但研發(fā)和生產(chǎn)成本較高。

4. NPU(神經(jīng)網(wǎng)絡(luò)處理器)架構(gòu):NPU是專門為加速神經(jīng)網(wǎng)絡(luò)運(yùn)算而設(shè)計(jì)的硬件架構(gòu)。NPU具有高度并行的計(jì)算單元,并針對深度學(xué)習(xí)計(jì)算進(jìn)行了優(yōu)化,如卷積計(jì)算、矩陣乘法和張量處理等。NPU可實(shí)現(xiàn)高效的神經(jīng)網(wǎng)絡(luò)推理和訓(xùn)練。

5. DSP(數(shù)字信號處理器)架構(gòu):DSP廣泛應(yīng)用于信號處理和音頻處理領(lǐng)域,也被用于一些AI應(yīng)用。DSP架構(gòu)通過并行計(jì)算和高速運(yùn)算單元,支持復(fù)雜的算術(shù)運(yùn)算和信號處理操作,可加速深度學(xué)習(xí)推理任務(wù)。

這些AI芯片技術(shù)架構(gòu)都有各自的特點(diǎn)和優(yōu)勢,可以根據(jù)應(yīng)用需求選擇合適的架構(gòu)。同時(shí),一些AI芯片采用了混合架構(gòu),結(jié)合了多種硬件類型和優(yōu)化策略,以實(shí)現(xiàn)更靈活、高效的計(jì)算能力。

芯片的架構(gòu)是什么意思

芯片的架構(gòu)指的是芯片內(nèi)部的設(shè)計(jì)和組織方式,包括電路結(jié)構(gòu)、功能模塊、數(shù)據(jù)通路和控制單元等方面的內(nèi)容。芯片的架構(gòu)決定了芯片的性能、功能和能效等特性。

具體來說,芯片的架構(gòu)涉及以下幾個(gè)方面:

1. 功能模塊:芯片的架構(gòu)確定了芯片集成的各種功能模塊,如CPU核心、內(nèi)存控制器、輸入輸出接口等。不同的應(yīng)用需求可能需要不同的功能模塊組合。

2. 數(shù)據(jù)通路:芯片的架構(gòu)描述了數(shù)據(jù)在芯片內(nèi)部的流動路徑和處理過程。數(shù)據(jù)通路包括寄存器、運(yùn)算單元、數(shù)據(jù)緩存等,用于數(shù)據(jù)傳輸、運(yùn)算和存儲。

3. 控制單元:芯片的架構(gòu)中包含了控制單元,用于管理和協(xié)調(diào)芯片內(nèi)各個(gè)功能模塊的工作。控制單元負(fù)責(zé)指令解析、流水線調(diào)度、時(shí)序控制等任務(wù),確保芯片能夠按照預(yù)定流程進(jìn)行工作。

4. 性能特性:芯片的架構(gòu)直接影響了芯片的性能特性,如時(shí)鐘頻率、運(yùn)算能力、存儲容量等。合理的架構(gòu)設(shè)計(jì)可以提高芯片的性能,并滿足特定應(yīng)用場景的需求。

5. 能效特性:芯片的架構(gòu)也與芯片的能效密切相關(guān)。有效的架構(gòu)設(shè)計(jì)可以降低功耗,提高能效比,使芯片在給定的能耗下實(shí)現(xiàn)更高的性能。

芯片的架構(gòu)設(shè)計(jì)需要綜合考慮應(yīng)用場景、性能要求、功耗限制等多個(gè)因素。不同的架構(gòu)設(shè)計(jì)可以在不同的應(yīng)用領(lǐng)域中發(fā)揮優(yōu)勢,滿足不同的需求。

FPGA芯片定義及結(jié)構(gòu)

FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。

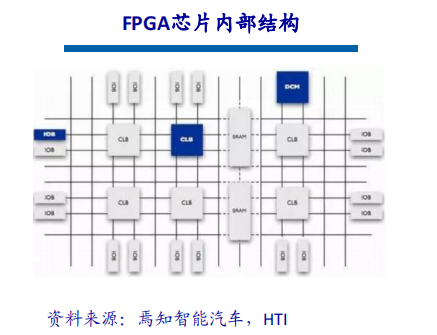

FPGA芯片主要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時(shí)鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊。目前主流的FPGA仍是基于查找表技術(shù)的,已經(jīng)遠(yuǎn)遠(yuǎn)超出了先前版本的基本性能,并且整合了常用功能(如RAM、時(shí)鐘管理和DSP)的硬核(ASIC型)模塊。

FPGA工作原理

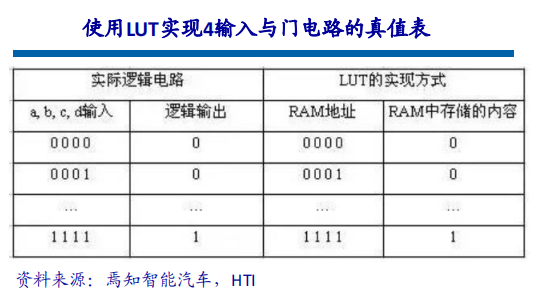

由于FPGA需要被反復(fù)燒寫,它實(shí)現(xiàn)組合邏輯的基本結(jié)構(gòu)不可能像ASIC那樣通過固定的與非門來完成,而只能采用一種易于反復(fù)配置的結(jié)構(gòu)。查找表可以很好地滿足這一要求,目前主流FPGA都采用了基于SRAM工藝的查找表結(jié)構(gòu),也有一些軍品和宇航級FPGA采用Flash或者熔絲與反熔絲工藝的查找表結(jié)構(gòu)。通過燒寫文件改變查找表內(nèi)容的方法來實(shí)現(xiàn)對FPGA的重復(fù)配置。

查找表(Look-Up-Table)簡稱為LUT,LUT本質(zhì)上就是一個(gè)RAM。目前FPGA中多使用4輸入的LUT,所以每一個(gè)LUT可以看成一個(gè)有4位地址線的RAM。當(dāng)用戶通過原理圖或HDL語言描述了一個(gè)邏輯電路以后,PLD/FPGA開發(fā)軟件會自動計(jì)算邏輯電路的所有可能結(jié)果,并把真值表(即結(jié)果)事先寫入RAM,這樣,每輸入一個(gè)信號進(jìn)行邏輯運(yùn)算就等于輸入一個(gè)地址進(jìn)行查表,找出地址對應(yīng)的內(nèi)容,然后輸出即可。

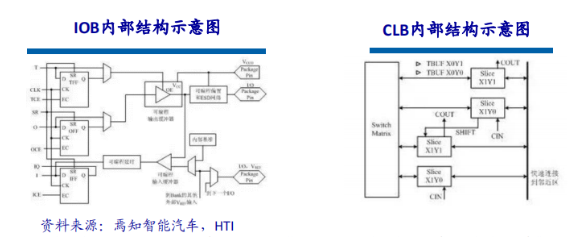

可編程輸入/輸出單元簡稱I/O單元,是芯片與外界電路的接口部分,完成不同電氣特性下對輸入/輸出信號的驅(qū)動與匹配要求。FPGA內(nèi)的I/O按組分類,每組都能夠獨(dú)立地支持不同的I/O標(biāo)準(zhǔn)。通過軟件的靈活配置,可適配不同的電氣標(biāo)準(zhǔn)與 I/O物理特性,可以調(diào)整驅(qū)動電流的大小,可以改變上、下拉電阻。目前,I/O口的頻率也越來越高,一些高端的FPGA通過DDR寄存器技術(shù)可以支持高達(dá)2Gbps的數(shù)據(jù)速率。

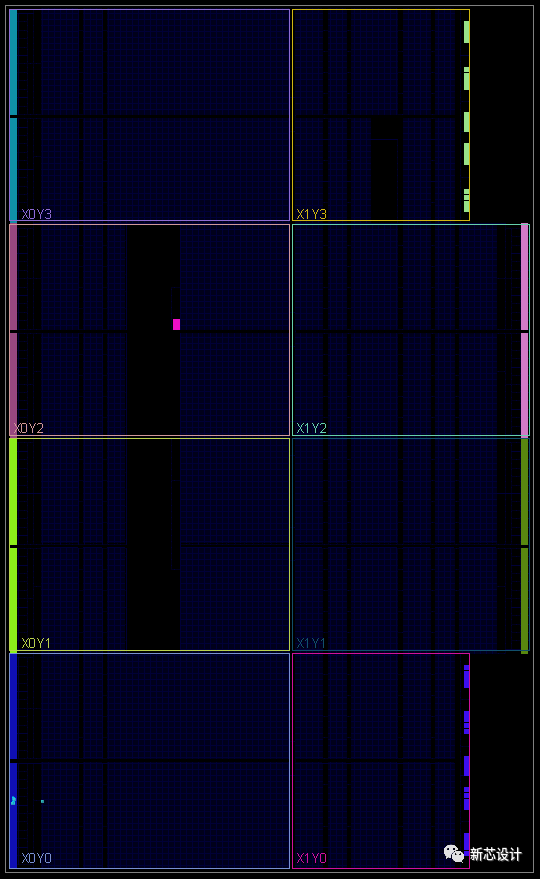

CLB是FPGA內(nèi)的基本邏輯單元。CLB的實(shí)際數(shù)量和特性會依器件的不同而不同,但是每個(gè)CLB都包含一個(gè)可配置開關(guān)矩陣,此矩陣由4或6個(gè)輸入、一些選型電路(多路復(fù)用器等)和觸發(fā)器組成。開關(guān)矩陣是高度靈活的,可以對其進(jìn)行配置以便處理組合邏輯、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多個(gè)(一般為4個(gè)或2個(gè))相同的Slice和附加邏輯構(gòu)成。每個(gè)CLB模塊不僅可以用于實(shí)現(xiàn)組合邏輯、時(shí)序邏輯,還可以配置為分布式RAM和分布式ROM。

自動駕駛的“芯”殺手

自動駕駛和高級駕駛輔助系統(tǒng)(ADAS)細(xì)分市場正在經(jīng)歷蛻變,對計(jì)算和傳感器功能提出了新的復(fù)雜需求。FPGA擁有其他芯片解決方案無法比擬的獨(dú)特優(yōu)勢,是滿足自動駕駛行業(yè)不斷發(fā)展變化的優(yōu)良選擇。FPGA是芯片領(lǐng)域的一種特殊技術(shù),一方面能夠通過軟件工具進(jìn)行反復(fù)多次配置,另一方面擁有豐富的IO接口和計(jì)算單元。因此,F(xiàn)PGA能夠根據(jù)應(yīng)用場景的具體需求,同時(shí)處理流水線并行和數(shù)據(jù)并行,天生具有計(jì)算性能高、延遲低、功耗小等優(yōu)勢。

FPGA具備高吞吐量、高能效以及實(shí)時(shí)處理等多項(xiàng)優(yōu)點(diǎn),非常契合自動駕駛所需要的技術(shù)需求。高級輔助駕駛系統(tǒng)(ADAS)、車載體驗(yàn)(IVE)應(yīng)用的標(biāo)準(zhǔn)和要求正在快速演變,系統(tǒng)設(shè)計(jì)人員關(guān)注的問題主要包括出色的靈活性和更快的開發(fā)周期,同時(shí)維持更高的性能功耗比。通過可重新編程的FPGA和不斷增多的汽車級產(chǎn)品相結(jié)合,支持汽車設(shè)計(jì)師滿足設(shè)計(jì)要求,在不斷變化的汽車行業(yè)中始終保持領(lǐng)先。

適應(yīng)性更強(qiáng)的平臺

對于自動駕駛芯片來說真正的價(jià)值在于計(jì)算引擎的利用率,即理論性能和實(shí)際性能之間的差異。FPGA包含大量的路由鏈路以及大量的小型存儲。這些資源的組合使設(shè)計(jì)人員能夠?yàn)槠溆?jì)算引擎創(chuàng)建定制的數(shù)據(jù)饋送網(wǎng)絡(luò),以獲得更高的利用水平。可編程邏輯為客戶提供了高度的靈活性,以適應(yīng)ADAS和自動駕駛等新興應(yīng)用領(lǐng)域不斷變化的需求。利用改進(jìn)的接口標(biāo)準(zhǔn)、算法創(chuàng)新和新的傳感器技術(shù),都需要適應(yīng)性強(qiáng)的平臺,不僅可以支持軟件更改,還可以支持硬件更改,而這正是FPGA芯片的優(yōu)勢所在。

FPGA芯片擁有可擴(kuò)展性。可拓展的芯片改變了可編程邏輯的數(shù)量,大多采用引腳兼容的封裝。這意味著開發(fā)人員可以創(chuàng)建單個(gè)ECU平臺來承載低、中、高版本的ADAS功能包,并根據(jù)需要通過選擇所需的最小密度芯片來縮放成本。

差異化解決方案

FPGA芯片允許開發(fā)人員創(chuàng)建獨(dú)特的差異化處理解決方案,這些解決方案可以針對特定應(yīng)用或傳感器進(jìn)行優(yōu)化。這對于ASSP芯片來說是無法實(shí)現(xiàn)的,即使是那些提供專用加速器的芯片,它們的使用方式也受到限制,而且基本上可以提供給所有競爭對手。例如Xilinx的長期客戶已經(jīng)創(chuàng)建了只有他們可以訪問的高價(jià)值IP庫,并且這些功能可以被公司的各種產(chǎn)品使用。從90nm節(jié)點(diǎn)開始,對于大批量汽車應(yīng)用,Xilinx的芯片就已經(jīng)極具成本效益,有超過1.6億顆Xilinx芯片在該行業(yè)獲得應(yīng)用。

編輯:黃飛

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603389 -

集成電路

+關(guān)注

關(guān)注

5388文章

11547瀏覽量

361828 -

asic

+關(guān)注

關(guān)注

34文章

1200瀏覽量

120506 -

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4771瀏覽量

100767 -

AI芯片

+關(guān)注

關(guān)注

17文章

1887瀏覽量

35021

發(fā)布評論請先 登錄

相關(guān)推薦

手把手教你設(shè)計(jì)人工智能芯片及系統(tǒng)--(全階設(shè)計(jì)教程+AI芯片FPGA實(shí)現(xiàn)+開發(fā)板)

AI發(fā)展對芯片技術(shù)有什么影響?

AI芯片熱潮和架構(gòu)創(chuàng)新有什么作用

AI芯片格局最全分析 精選資料分享

集成電路芯片AI低功耗設(shè)計(jì)的新方法

基于FPGA芯片的數(shù)據(jù)流結(jié)構(gòu)分析

AI芯片什么是AI芯片的架構(gòu)、分類及關(guān)鍵技術(shù)概述

為何AI需要新的芯片架構(gòu)?

fpga芯片架構(gòu)介紹

自動駕駛?cè)笾髁?b class='flag-5'>芯片架構(gòu)分析

ai芯片技術(shù)架構(gòu)有哪些?FPGA芯片定義及結(jié)構(gòu)分析

ai芯片技術(shù)架構(gòu)有哪些?FPGA芯片定義及結(jié)構(gòu)分析

評論