1、硬件描述語言HDL(Hardware Description Language)

硬件描述語言(HDL)是一種用形式化方法來描述數字電路和系統的語言。數字電路系統的設計者利用這種語言可以從上層到下層(從抽象到具體)逐層描述自己的設計思想,用一系列分層次的模塊來表示極其復雜的數字系統。然后利用電子設計自動化(以下簡稱為EDA)工具逐層進行仿真驗證,再把其中需要變為具體物理電路的模塊組合經由自動綜合工具轉換到門級電路網表。接下去再用專用集成電路(ASIC)或現場可編程門陣列(FPGA)自動布局布線工具把網表轉換為具體電路布線結構的實現。在制成物理器件之前,還可以用Verilog的門級模型(原語元件或UDP)來代替具體基本元件。因其邏輯功能和延時特性與真實的物理元件完全一致,所以在仿真工具的支持下能驗證復雜數字系統物理結構的正確性,使投片的成功率達到100%。目前,這種稱之為高層次設計(High-Level-Design)的方法已被廣泛采用。據統計,目前在美國硅谷約有90%以上的ASIC和FPGA已采用Verilog硬件描述語言方法進行設計。

硬件描述語言的發展至今已有近三十年的歷史,并成功地應用于設計的各個階段:建模、仿真、驗證 和綜合等。最近十多年來,用綜合工具把可綜合風格的HDL模塊自動轉換為具體電路發展非常迅速,大大地提高了復雜數字系統的設計生產率。在美國和日本等先進電子工業國,Verilog語言已成為設計數字系統的基礎。

對于FPGA新手應由淺入深學習:

(1)Verilog的基本語法,

(2)簡單的可綜合Verilog模塊與邏輯電路的對應關系,

(3)簡單的Verilog測試模塊和它的意義,

(4)如何編寫復雜的多層次的可綜合風格的Verilog HDL模塊,

(5)如何用可綜合的Verilog模塊構成一個可靠的復雜IP軟核和固核模塊,

(6)在開發工具建立自己的FPGA工程,實現簡單FPGA小例子。

2、Verilog HDL的歷史

2.1、什么是Verilog HDL

Verilog HDL是硬件描述語言的一種,用于數字電子系統設計。它允許設計者用它來進行各種級別的邏輯設計,可以用它進行數字邏輯系統的仿真驗證、時序分析、邏輯綜合。它是目前應用最廣泛的一種硬件描述語言。據有關文獻報道,目前在美國使用Verilog HDL進行設計的工程師大約有10多萬人,全美國有200多所大學教授用 Verilog 硬件描述語言的設計方法。在我國臺灣地區幾乎所有著名大學的電子和計算機工程系都講授Verilog有關的課程。

2.2、Verilog HDL的產生及發展

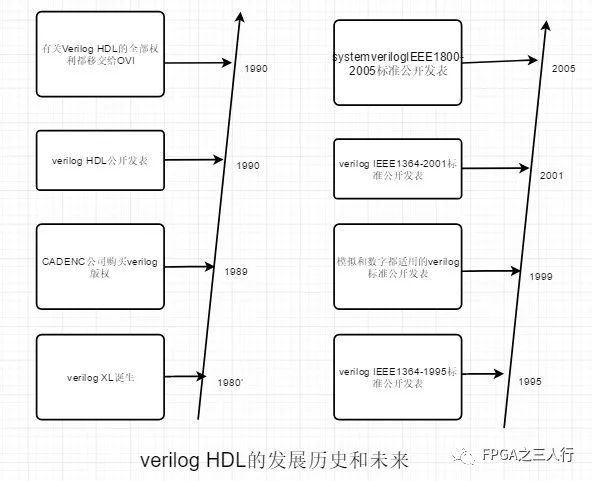

Verilog HDL是在1983年,由GDA(GateWay Design Automation)公司的Phil Moorby首創的。Phil Moorby后來成為Verilog-XL的主要設計者和Cadence公司(Cadence Design System)的第一個合伙人。在1984-1985年,Moorby設計出了第一個名為Verilog-XL的仿真器,1986年,他對Verilog HDL的發展又作出了另一個巨大貢獻:即提出了用于快速門級仿真的XL算法。

隨著Verilog-XL算法的成功,Verilog HDL語言得到迅速發展。1989年,Cadence公司收購了GDA公司,Verilog HDL語言成為Cadence公司的私有財產。1990年,Cadence公司決定公開Verilog HDL語言,于是成立了OVI(Open Verilog International)組織來負責促進Verilog HDL語言的發展。基于Verilog HDL的優越性,IEEE于1995年制定了Verilog HDL的IEEE標準,即Verilog HDL1364-1995;2001年發布了Verilog HDL1364-2001標準;2005年SystemVerilog IEEE 1800-2005 標準的公布,更使得Verilog語言在綜合、仿真驗證和模塊的重用等性能方面都有大幅度的提高。

下圖展示了Verilog的發展歷史和未來。

圖1

2.3、Verilog HDL和 VHDL的比較

Verilog HDL和VHDL都是用于邏輯設計的硬件描述語言,并且都已成為IEEE標準。VHDL是在1987年成為IEEE標準,Verilog HDL則在1995年才正式成為IEEE標準。之所以VHDL比Verilog HDL早成為IEEE標準,這是因為VHDL是由美國軍方組織開發的,而Verilog HDL 則是從一個普通的民間公司的私有財產轉化而來,基于Verilog HDL的優越性,才成為的IEEE標準,因而有更強的生命力。

VHDL 其英文全名為VHSIC Hardware Description Language,而VHSIC則是Very High Speed Integerated Circuit的縮寫詞,意為甚高速集成電路,故VHDL其準確的中文譯名為甚高速集成電路的硬件描述語言。

Verilog HDL和VHDL作為描述硬件電路設計的語言,其共同的特點在于:能形式化地抽象表示電路的行為和結構、支持邏輯設計中層次與范圍的描述、可借用高級語言的精巧結構來簡化電路行為的描述、具有電路仿真與驗證機制以保證設計的正確性、支持電路描述由高層到低層的綜合轉換、硬件描述與實現工藝無關(有關工藝參數可通過語言提供的屬性包括進去)、便于文檔管理、易于理解和設計重用。

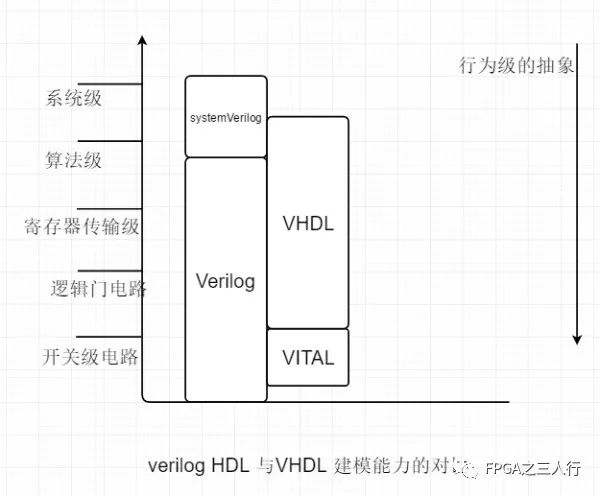

但是Verilog HDL和VHDL又各有其自己的特點。由于Verilog HDL早在1983年就已推出,至今已有二十多年的應用歷史,因而Verilog HDL擁有更廣泛的設計群體,成熟的資源也遠比VHDL豐富。與VHDL相比Verilog HDL的最大優點是:它是一種非常容易掌握的硬件描述語言,只要有C語言的編程基礎,通過二十學時的學習,再加上一段實際操作,一般同學可在二至三個月內掌握這種設計方法的基本技術。而掌握VHDL設計技術就比較困難。這是因為VHDL不很直觀,需要有Ada編程基礎,一般認為至少需要半年以上的專業培訓,才能掌握VHDL的基本設計技術。2005年SystemVerilog IEEE1800-2005標準公布以后,集成電路設計界普遍認為Verilog HDL 將在十年內全面取代VHDL成為ASIC設計行業包攬設計、測試和驗證功能的的唯一語言。下面圖2所示的是Verilog HDL和VHDL建模能力的比較圖,供讀者參考:

圖2

2001年公布的VerilogIEEE1364- 2001標準和2005年公布的SystemVerilog IEEE1800-2005標準,不但使Verilog的可綜合性能和系統仿真性能方面有大幅度的提高,而且在IP的重用方面(包括設計和驗證模塊的重用)也有重大的突破。因此Verilog HDL不但作為學習HDL設計方法的入門和基礎是比較合適的,而且對于ASIC設計專業人員而言,也是必須掌握的基本技術。學習掌握Verilog HDL建模、仿真、綜合、重用和驗證技術不僅可以使同學們對數字電路設計技術有更進一步的了解,而且可以為以后學習高級的行為綜合、物理綜合、IP設計和復雜系統設計和驗證打下堅實的基礎。

2.4、 Verilog 目前的應用情況和適用的設計

近十多年以來,EDA界一直對在數字邏輯設計中究竟采用哪一種硬件描述語言爭論不休。近兩三年來,美國、日本和我國臺灣省電子設計界的情況已經清楚地表明,在高層次數字系統設計領域,Verilog 已經取得壓倒性的優勢;在中國大陸,近10年來,Verilog應用的比率已有顯著的增加。根據筆者了解,國內大多數集成電路設計公司都采用Verilog HDL。Verilog是專門為復雜數字系統的設計仿真而開發的,本身就非常適合復雜數字邏輯電路和系統的仿真和綜合。由于Verilog 在其門級描述的底層,也就是在晶體管開關的描述方面比VHDL有強得多得功能,所以即使是VHDL的設計環境,在底層實質上也是由Verilog HDL描述的器件庫所支持的。1998年通過的Verilog HDL新標準,把Verilog HDL-A并入Verilog HDL新標準,使其不僅支持數字邏輯電路的描述還支持模擬電路的描述,因此在混合信號的電路系統的設計中,它也有很廣泛的應用。在深亞微米ASIC和高密度FPGA已成為電子設計主流的今天,Verilog的發展前景是非常遠大的。2001年3月,Verilog IEEE1364-2001標準的公布,以及2005年10月SystemVerilog IEEE 1800-2005 標準的公布,使得Verilog語言在綜合、仿真驗證和IP模塊重用等性能方面都有大幅度的提高,更加拓寬了Verilog的發展前景。

Verilog適合系統級(System)、算法級(Alogrithem)、寄存器傳輸級(RTL)、邏輯級(Logic)、門級(Gate)、電路開關級(Switch)設計,而SystemVerilog是Verilog語言的擴展和延伸,更適用于可重用的可綜合IP和可重用的驗證用IP設計,以及特大型(千萬門級以上)基于IP的系統級設計和驗證。

2.5、采用Verilog HDL設計復雜數字電路的優點

2.5.1、傳統設計方法--電路原理圖輸入法

幾十年前,當時所做的復雜數字邏輯電路及系統的設計規模比較小也比較簡單,其中所用到的FPGA或ASIC設計工作往往只能采用廠家提供的專用電路圖輸入工具來進行。為了滿足設計性能指標,工程師往往需要花好幾天或更長的時間進行艱苦的手工布線。工程師還得非常熟悉所選器件的內部結構和外部引線特點,才能達到設計要求。這種低水平的設計方法大大延長了設計周期。

近年來,FPGA和ASIC的設計在規模和復雜度方面不斷取得進展,而對邏輯電路及系統的設計的時間要求卻越來越短。這些因素促使設計人員采用高水準的設計工具,如:硬件描述語言(Verilog HDL或VHDL)來進行設計。

2.5.2、 Verilog HDL設計法與傳統的電路原理圖輸入法的比較

如 2.5.1.所述,采用電路原理圖輸入法進行設計,具有設計的周期長,需要專門的設計工具,需手工布線等缺陷。而采用Verilog 輸入法時,由于Verilog HDL的標準化,可以很容易地把完成的設計移植到不同的廠家的不同的芯片中去,并在不同規模的應用時可以較容易地作修改。這不僅是因為用Verilog HDL所完成的設計,它的信號位數是很容易改變的,可以很容易地對它進行修改,來適應不同規模的應用,在仿真驗證時,仿真測試矢量還可以用同一種描述語言來完成,而且還因為采用Verilog HDL綜合器生成的數字邏輯是一種標準的電子設計互換格式(EDIF)文件,獨立于所采用的實現工藝。有關工藝參數的描述可以通過 Verilog HDL提供的屬性包括進去,然后利用不同廠家的布局布線工具,在不同工藝的芯片上實現。

采用Verilog 輸入法最大的優點是其與工藝無關性。這使得工程師在功能設計、邏輯驗證階段,可以不必過多考慮門級及工藝實現的具體細節,只需要利用系統設計時對芯片的要求,施加不同的約束條件,即可設計出實際電路。實際上這是利用了計算機的巨大能力在EDA工具的幫助下,把邏輯驗證與具體工藝庫匹配、布線及時延計算分成不同的階段來實現從而減輕了人們的繁瑣勞動。

2.5.3、Verilog 的標準化

Verilog 是在1983年由GATEWAY公司首先開發成功的,經過諸多改進,于1995年11月正式被批準為Verilog IEEE1364-1995標準,2001年3月在原標準的基礎上經過改進和補充又推出Verilog IEEE1364-2001新標準。2005年10月又推出了Verilog語言的擴展,即SystemVerilog (IEEE 1800-2005 標準)語言,這使得Verilog語言在綜合、仿真驗證和IP模塊重用等性能方面都有大幅度的提高,更加拓寬了Verilog的發展前景。

Verilog HDL的標準化大大加快了Verilog HDL的推廣和發展。由于Verilog HDL設計方法的與工藝無關性,因而大大提高了Verilog模型的可重用性。

2.5.4、軟核

我們把功能經過驗證的、可綜合的、實現后電路結構總門數在5000門以上的Verilog HDL模型稱之為“軟核”(Soft Core)。而把由軟核構成的器件稱為虛擬器件,在新電路的研制過程中,軟核和虛擬器件可以很容易地借助EDA綜合工具與其它外部邏輯結合為一體。這樣,軟核和虛擬器件的重用性就可大大縮短設計周期,加快了復雜電路的設計。

2.5.5、固核和硬核的概念以及它們的重用

2.5.5.1、固核

我們把在某一種現場可編程門陣列(FPGA)器件上實現的,經驗證是正確的總門數在5000門以上電路結構編碼文件,稱之為“固核”。

2.5.5.1、硬核

我們把在某一種專用集成電路工藝的(ASIC)器件上實現的經驗證是正確的總門數在5000門以上的電路結構版圖掩膜,稱之為“硬核”。

2.5.5.3、軟核、固核、硬核對比

在具體實現手段和工藝技術尚未確定的邏輯設計階段,軟核具有最大的靈活性,它可以很容易地借助EDA綜合工具與其它外部邏輯結合為一體。當然,由于實現技術的不確定性,有可能要作一些改動以適應相應的工藝。相比之下固核和硬核與其它外部邏輯結合為一體的靈活性要差得多,特別是電路實現工藝技術改變時更是如此。而近年來電路實現工藝技術的發展是相當迅速的,為了邏輯電路設計成果的積累,和更快更好地設計更大規模的電路,發展軟核的設計和推廣軟核的重用技術是非常有必要的。我們新一代的數字邏輯電路設計師必須掌握這方面的知識和技術。Verilog語言以及它的擴展SystemVerilog 是設計可重用的IP,即軟核、固核、硬核和驗證用虛擬核所必須的語言。

2.6、FPGA硬件描述語言設計流程

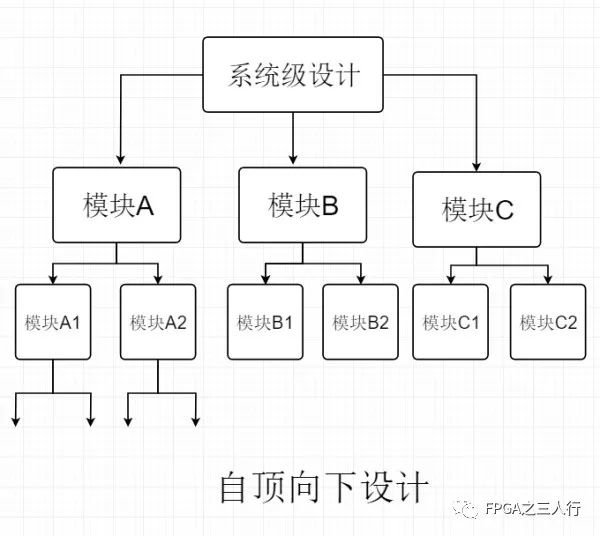

2.6.1、自頂向下(Top-Down)設計

自頂向下的設計(即TOP_DOWN設計)是從系統級開始,把系統劃分為基本單元,然后再把每個基本單元劃分為下一層次的基本單元,一直這樣做下去,直到可以直接用EDA元件庫中的基本元件來實現為止。利用層次化、結構化的設計方法,一個完整的硬件設計任務首先由總設計師(Architect)劃分為若干個可操作的模塊,編制出相應的模型(行為的或結構的),通過仿真加以驗證后,再把這些模塊分配給下一層的設計師。這就允許多個設計者同時設計一個硬件系統中的不同模塊,其中每個設計者負責自己所承擔的部分;而由上一層設計師對其下層設計者完成的設計用行為級上層模塊對其所做的設計進行驗證。為了提高設計質量,如果其中有一部分模塊可由商業渠道得到,我們可以購買它們的知識產權的使用權(IP核的重用),以節省時間和開發經費,。圖3為自頂向下的示意圖,以設計樹的形式繪出。

圖3 自頂向下設計

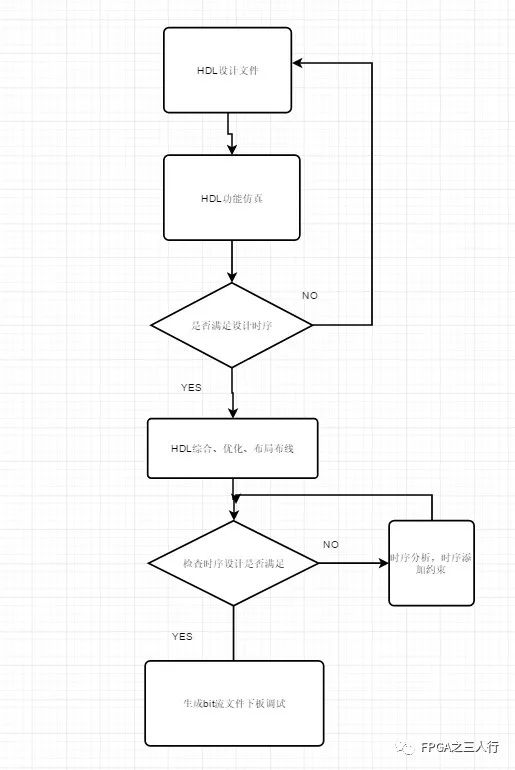

2.6.2、FPGA模塊的設計編譯和仿真的過程

在不同的層次做具體模塊的設計所用的方法也有所不同,在高層次上往往編寫一些行為級的模塊通過仿真加以驗證,其主要目的是系統性能的總體考慮和各模塊的指標分配,并非具體電路的實現。因而綜合及其以后的步驟往往不需進行。而當設計的層次比較接近底層時,行為描述往往需要用電路邏輯來實現。這時的模塊不僅需要通過仿真加以驗證,還需進行綜合、優化、布線和后仿真。總之具體電路是從底向上逐步實現的。EDA工具往往不僅支持HDL描述也支持電路圖輸入,有效地利用這兩種方法是提高設計效率的辦法之一。下面的流程圖簡要地說明了模塊的編譯和測試過程:

圖4

從上圖可以看出,模塊設計流程主要由兩大主要功能部分組成:

(1)、設計開發:即從編寫設計文件-->綜合到布局布線-->電路生成這樣一系列步驟。

(2)、設計驗證:也就是進行各種仿真的一系列步驟,如果在仿真過程中發現問題就返回設計輸入進行修改。

2.7、總結

2.7.1、編程語言verilog的優點

(1)采用VerilogHDL進行電路設計的最大優點是設計與工藝無關系,

(2)能夠在每個抽象層次的描述上對設計進行仿真驗證,

(3)VerilogHDL適用于復雜數字邏輯電路和系統的總體仿真、子系統仿真和具體電路綜合等各個設計階段。

2.7.2、熟練掌握FPGA設計流程

由于TOP_DOWN的設計方法是首先從系統設計入手,從頂層進行功能劃分和結構設計。系統的總體仿真是頂層進行功能劃分的重要環節,這時的設計是與工藝無關的。由于設計的主要仿真和調試過程是在高層次完成的所以能夠早期發現結構設計上的錯誤,避免設計工作的浪費,同時也減少了邏輯仿真的工作量。自頂向下的設計方法方便了從系統級劃分和管理整個項目,使得幾十萬門甚至幾千萬門規模的復雜數字電路的設計成為可能,并可減少設計人員,避免不必要的重復設計,提高了設計的一次成功率。

從底向上的設計在某種意義上講可以看作上述TOP_DOWN設計的逆過程。雖然設計也是從系統級開始,即從設計樹的樹根開始對設計進行逐次劃分,但劃分時首先考慮的是單元是否存在,即設計劃分過程必須從已經存在的基本單元出發,設計樹最末枝上的單元要么是已經制造出的單元,要么是其它項目已開發好的單元或者是可外購得到的單元。

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603319 -

Verilog

+關注

關注

28文章

1351瀏覽量

110095 -

HDL

+關注

關注

8文章

327瀏覽量

47382 -

編程語言

+關注

關注

10文章

1945瀏覽量

34735

原文標題:FPGA之編程語言verilog

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog HDL的歷史 FPGA硬件描述語言設計流程

Verilog HDL的歷史 FPGA硬件描述語言設計流程

評論