今天,我們來聊聊數據中心另一個新技術CXL。

在過去幾十年中,CPU一直是計算系統中的絕對核心,甚至連存儲、網絡等子系統的能力都是CPU說了算。

比如,一個CPU能夠支持多大的內存,CPU都是有嚴格要求的。甚至同樣一顆CPU,只是支持不同的內容,都能賣兩個價格。

而且更要命的是,隨著大內存等應用場景需求大增,想要擴展內存容量,你只能通過買CPU的方式才能擴展內存容量,想要在內存上做點"手腳"那是被限制的死死的。

但人算不如天算,在Intel按部就班的擠牙膏的時候,沒想到大數據AI、視覺渲染、基因分析以及EDR仿真等需求的突然爆發,給了NVIDIA 的GPU帶了巨大增長空間。

眼看著GPU越賣越多,NVIDIA的市值甚至遠遠超過了Intel,于是英特爾"揮刀自宮",讓充滿黑科技意味的傲騰業務和3D Xpoint走向終結,取而代之的是開始向CXL架構發展。

▉推出CXL ,Intel是為了什么?

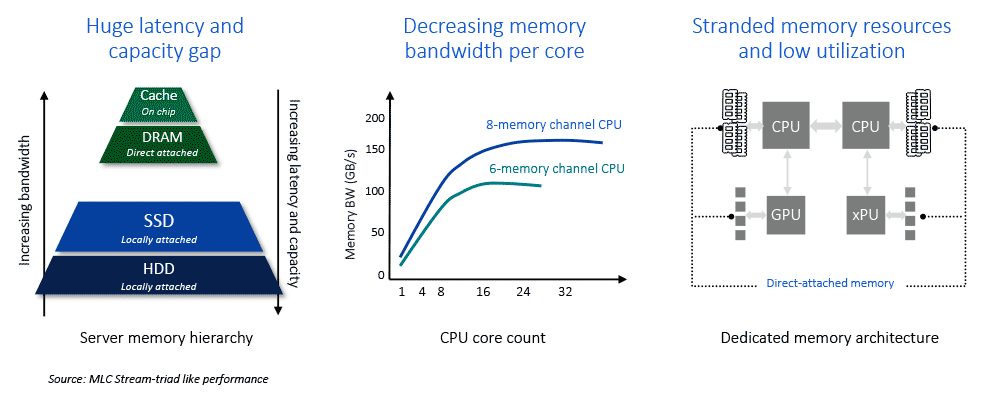

上文中提到,在當前的系統架構中,內存子系統面臨諸多挑戰。

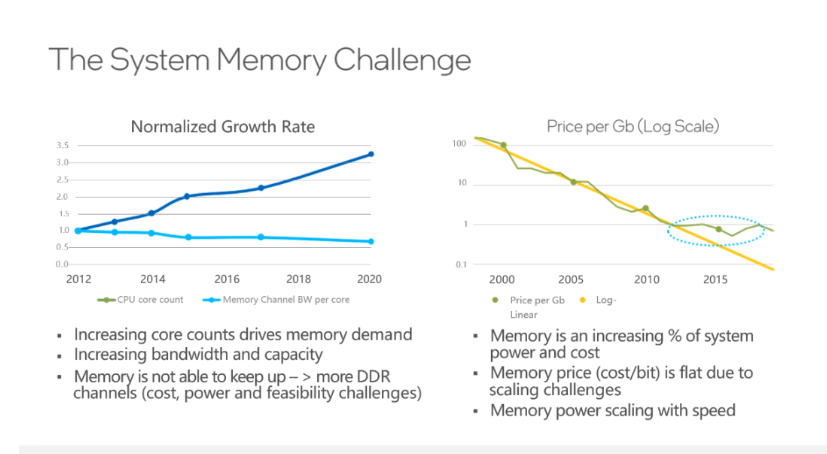

如下面左圖所示,CPU技術的發展使得核心數量實現了比較快的增長,內存通道數增速卻相對較慢。但從發展趨勢來看,每個CPU核心所擁有的內存通道反而是在下降。

這會帶來很多問題,很多CPU核心因為不能充分得到數據來處于滿負荷的運行狀態,會導致整體計算效率下降。

是可忍孰不可忍,這么明顯的問題為何Intel在增加核心的時候也增加內存通道呢?

其實并不是英特爾不想,而是牽扯到了多方面原因。首先在CPU設計方面,內存控制器是在CPU里的,如果增加內存通道,則意味著會增加CPU的功耗,芯片面積也會變大,PCB走線距離增加,為了保證信號的完整性,對于PCB本身也提出更高要求,所以,如果增加內存通道,CPU的成本和功耗都會增長。

另外,從服務器整機的層面來看,在主板上增加內存DIMM槽,插上更多的內存后,整機的成本也會不可避免地增長,即使內存成本降低,也不會無限度的降低下去,最終會導致整體成本的上升。所以,不能隨意的無限度地通過增加內存通道來解決問題。

既然增加內存通道這條路走不通,那有沒有其他方式可以解決內存互聯網問題呢?

這個答案當然是肯定的,為了解決內存子系統的問題,幾種不同的傳輸和內存語義協議逐漸出現--IBM的OpenCAPI內存接口協議、Xilinx的CCIX協議、NVIDIA的NVLink協議、惠普企業版的Gen-Z協議,都是為了解決內存池化方面的問題。

雖然這幾種協議方式與后來的CXL協議其實類似。但這些明顯挖英特爾"墻角"的方式并沒有得到Intel的積極響應。店大何止欺客,店大甚至可以決定產品的走向。

但眼看著GPU賣的越來越多,Intel有點坐不住了,于是在2019年3月份Intel推出了CXL(Compute Express Link)協議接口,其與CAPI酷似,也是將CXL協議封裝到PCIE鏈路層數據包中傳送,并在CPU端的PCIE總控后端按照事務標識分流CXL專屬事務給CXL處理邏輯處理。

為何Intel突然會突然妥協,讓出這部分利益,推出CXL協議呢?借用DOIT朱朋博老師的一句話:擱置爭議,共同開發。

商人總是尋求利益最大化,既然大內存需求趨勢已經來襲,堵不如疏,不如把GPU、DPU等用作一把刀,來與NVIDIA形成某種制衡,當然,如今的NVIDIA也加入了CXL聯盟,但是所謂"此路是我開,要在此路過,留下買路財"。反正我建了通往內存的"高速路",你GPU怎么走都得聽我的。

通過這種方式,也能進一步制衡GPU的發展,一如文章開頭Intel對內存的制約,想支持幾個GPU,還得通過我的CPU說了算。值得注意的是,第四代英特爾至強可擴展處理器每一顆處理器支持最多4個CXL設備,支持CXL Type1和CXL Type2。)

▉CXL協議具體能干啥?

從2019年發布CXL 1.0/1.1,到2020年11月發布CXL2.0,如今Intel已經發布了CXL 3.0,它的功能一直在發生著變化。

首先我們來看下CXL是什么?CXL要如何解決問題呢?

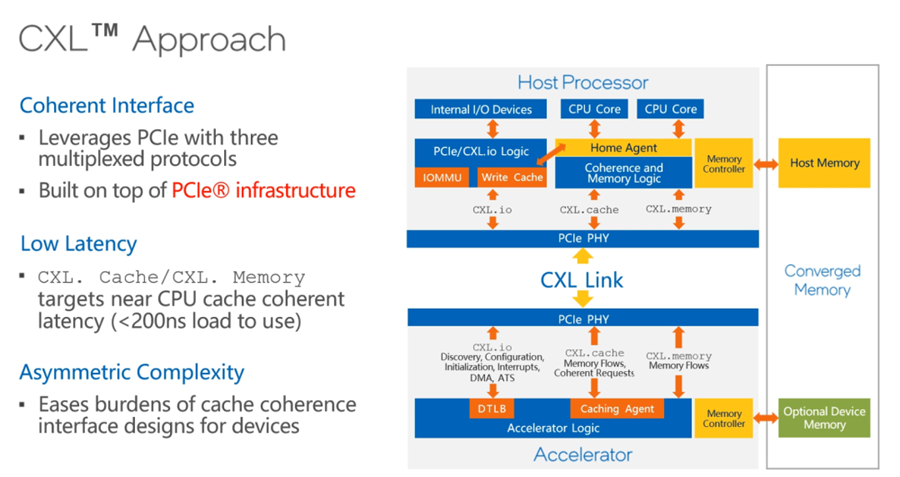

如今,CXL有CXL.io、CXL.memory和CXL.cache三個協議:

其中,CXL.io就是原來的PCIe,在CXL的建立連接、設備發現、配置等過程中發揮重要作用,連接建立后,CXL.cache協議負責做cache一致性的工作,CXL.cache和CXL.memory配合起來用來做內存擴展。

CXL.cache和CXL.memory對于latency的要求會比較高,尤其CXL.cache對延遲要求非常高,因為這關系到計算的效率。

在CXL1.0和1.1規范定義了三種Device:

Type1Device主要的應用場景是高性能計算里的網卡(PGAS NIC),它支持一些網卡的原子操作,主要利用的協議就是CXL.io和CXL.cache。

Type2Device主要指的是帶有內存的加速器,包括GPU、FPGA等加速器,它使用的協議包括用來做鏈接的CXL.io,做cache一致性的CXL.cache,用來做內存擴展的CXL.memory。

Type3Device主要用作內存的Buffer,做內存的擴展。它主要利用CXL.io和CXL.memory的協議。如圖所示,CPU除了可以用本地的DDR內存,還可以通過CXL去擴展遠端內存,遠端內存可以是一個大的內存池,這里的內存可以共享給不同的CPU來用。

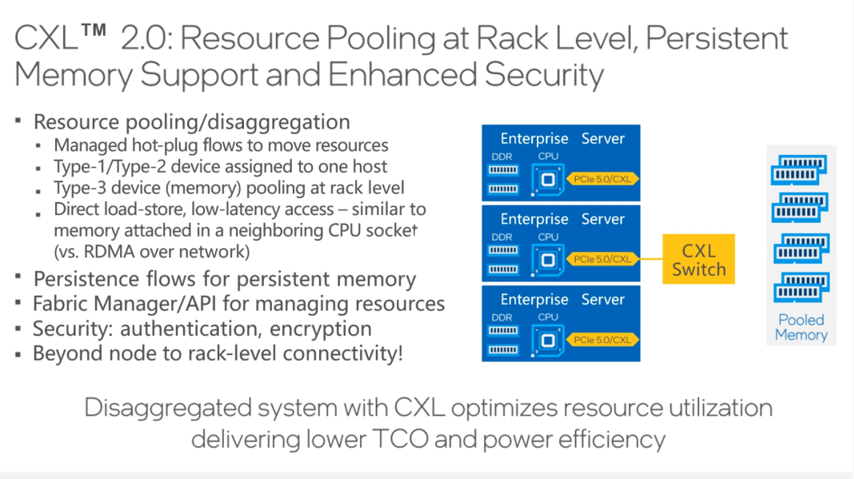

CXL2.0規范實現了機架級別的資源池化。

云計算強調資源可以像水和電一樣按需獲取,云計算的技術潮流下,追求不同資源之間的松耦合,為的是提高使用效率,為了提高使用效率,要實現的是相同資源的池化。

隨著技術的發展,未來的服務器不再是傳統意義上的服務器,它不再具有現實的形態,用戶從云服務商那里申請云主機的時候,主機的CPU是從CPU池里拿出來的,內存是從內存池里拿出來的,CPU池和內存池通過CXL連起來的。

使用從資源池里拿出來資源組成邏輯上的服務器,這就是資源解耦和資源池化在未來能帶來的變化。

CXL2.0規范在資源池化方面有所強化,同時,也還增加了CXL switch功能,它可以在一個機架內通過一套CXL交換機構建成一個網絡。

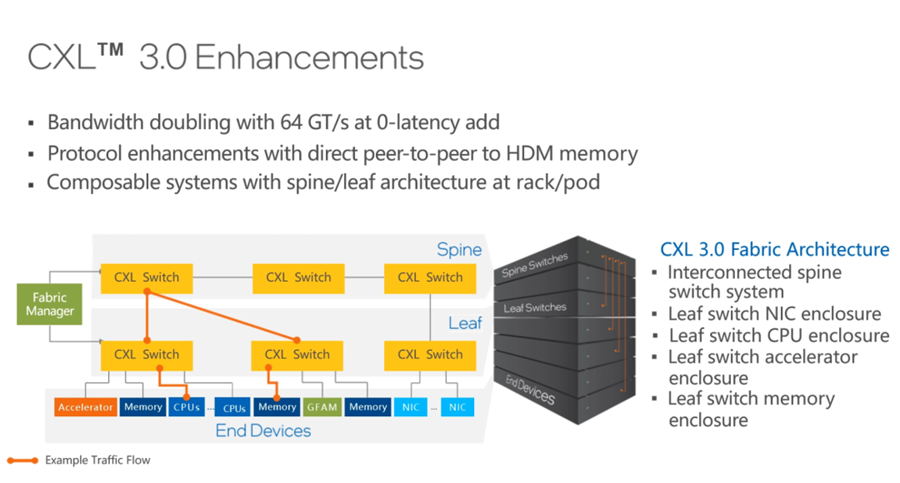

2022年,新發布的CXL 3.0規范又新增很多特性。

首先,CXL 3.0 PCIe 6.0規范,它的速率從32GT提升到了64GT,在相同的鏈路時,帶寬翻倍。并且,Latency也沒有任何變化。

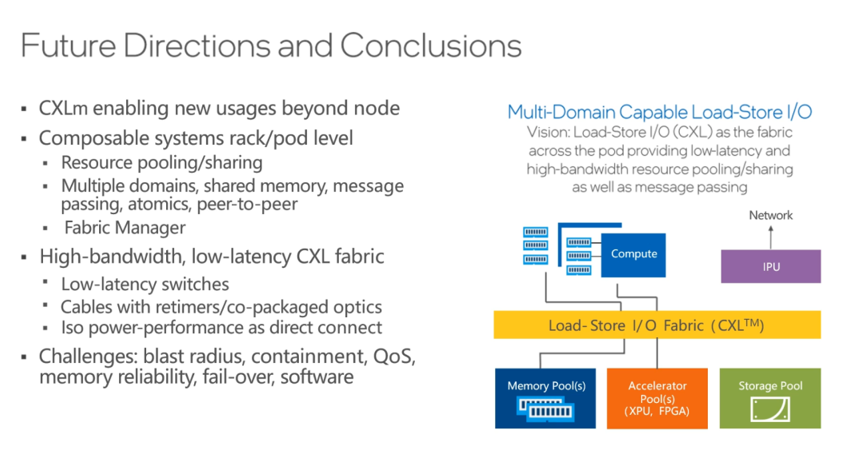

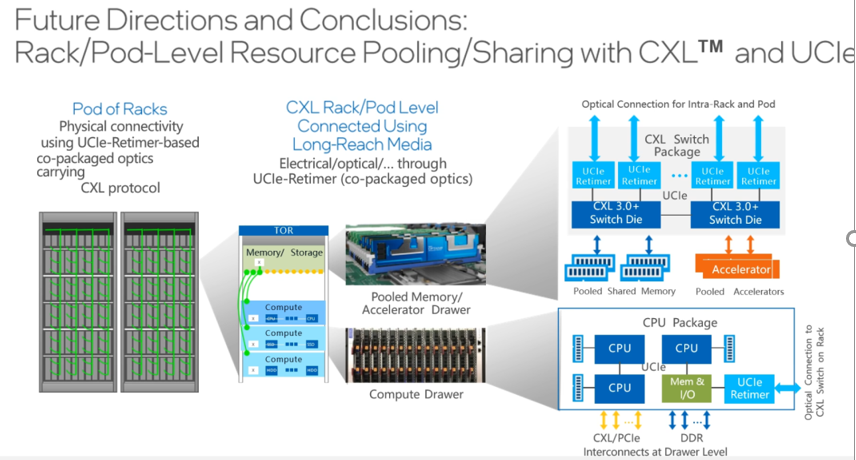

第二,CXL 3.0新增了對二層交換機的支持,也就是Leaf spine網絡架構,如此便可以更好地對資源進行解耦和池化,做更多的資源池,比如CPU資源池、內存資源池、網卡資源池和加速器資源池等,Leaf與Spine之間通過Fabric manager軟件構建各種拓撲和各種路由方式。

CXL 3.0不但可以更好地在一個機柜內實現計算資源和存儲資源的池化和解耦,而且,可以在多個機柜之間建立更大的資源池,如此一來,對于云計算服務商的資源管理效率和成本優化都會帶來很大幫助。

▉CXL的未來發展方向?

說了那么多CXL的優勢和好處,那么CXL的未來發展方向如何呢?

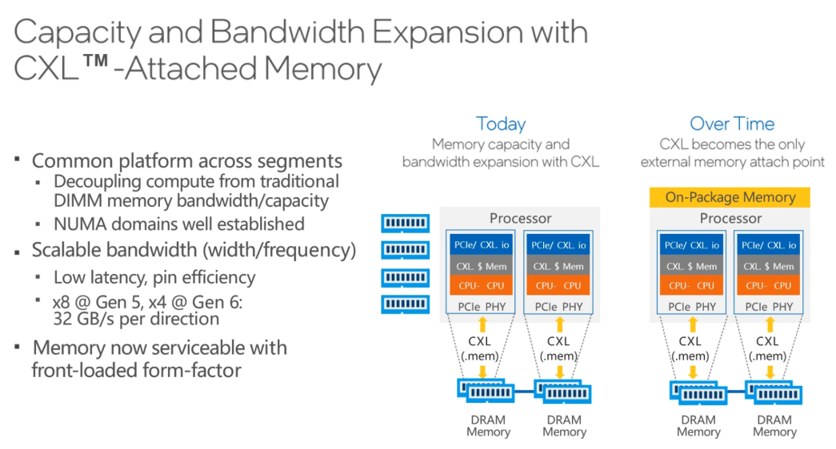

首先,CXL可以用來擴展內存的容量和帶寬,這是非常重要的一個方面。在使用服務器本地內存的同時,還可以通過CXL利用遠端內存,遠端內存的成本和價格相對更低,而且,它能讓CPU和內存之間的配比變得更靈活。

進一步發展之后,未來完全可以取消近端本地內存,全部都使用遠端內存,這有賴于摩爾定律的作用,讓計算芯片和存儲芯片都有更進一步的發展。

與此同時,CPU上會有比DRAM更高速的內存,比如可能會把HBM與處理器封裝到一個die里,使得CPU有更多的高速內存。

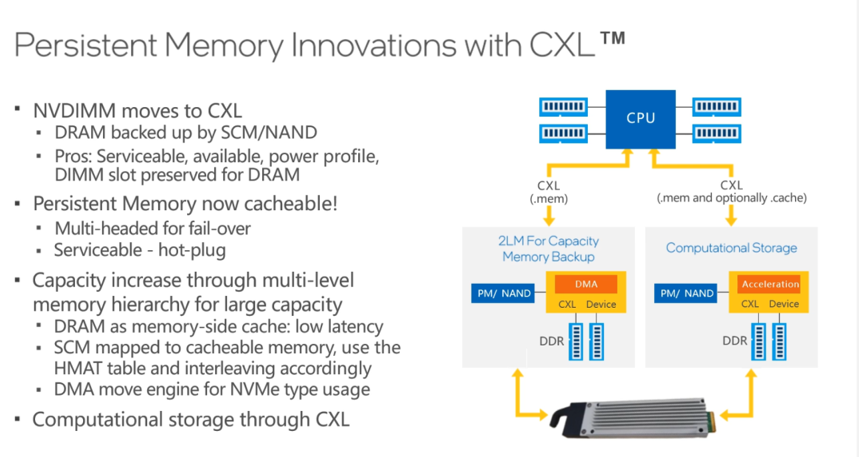

另外,還有一個趨勢在于遠端內存的持久化。目前,英特爾就有傲騰持久內存,但因為一些原因,英特爾宣布不再繼續研發了,不過,業界還有很多替代方案,比如NVDIMM,配合CXL將這些持久內存作為遠端內存,還能夠提供多種實用功能。

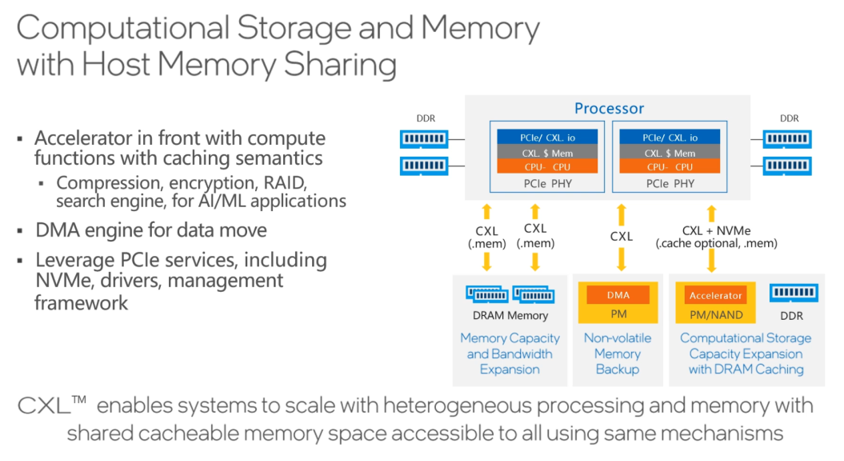

除此之外,還能利用CXL技術實現Computational Storage,通過CXL利用內存資源,在存儲上做一些壓縮或者解壓縮的操作,類似可以在遠端實現的功能還有很多。

CXL帶來的改變從單節點開始,擴展到機架規模,而后是Tor級別,最終會影響到數據中心級別,CXL將要重構未來的數據中心。

數據中心利用CXL做解耦和池化,CXL技術能夠讓不同的資源從緊耦合變成松耦合,讓相同的資源變成池化資源,會形成CPU資源池、GPU資源池以及內存資源池,各個資源池通過CXL連接。

在未來發展中,隨著CXL技術的逐步落地,IPU承擔的任務也會越來越多,既作為CXL的端點,又作為以太網的端點,會有很多功能和負載卸載到IPU上,架構上會有很多變化,將會有很多新的創新。

比如把存儲offload到IPU上,未來還有一些塊存儲或者其他內存相關服務也都可以用IPU來承載,通過CXL連接到相應的資源池上,總之,未來有非常多的想象空間。

最后,不得不說的是,未來的發展方向中,最終就要實現徹底的解耦和池化,過程是逐步從Rack級別,提升到資源池的級別,甚至是數據中心級別,而這些池化資源之間的共享就靠CXL和UCIe來實現。CXL重構數據中心,并不遙遠!

審核編輯:劉清

-

存儲器

+關注

關注

38文章

7502瀏覽量

163932 -

加速器

+關注

關注

2文章

800瀏覽量

37916 -

NVIDIA技術

+關注

關注

0文章

17瀏覽量

6290 -

PCB設計

+關注

關注

394文章

4690瀏覽量

85778 -

FPGA開發板

+關注

關注

10文章

122瀏覽量

31520

原文標題:一文詳解:為什么說CXL能重構數據中心?

文章出處:【微信號:LinuxDev,微信公眾號:Linux閱碼場】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CXL事務層的結構是由哪些部分組成的

CXL內存協議介紹

一文詳解CXL鏈路層格式的定義

Intel宣布聯合多家廠商推出全新互聯協議 并發布CXL1.0規范

Astera Labs推出業界首個 CXL? 2.0 Memory Accelerator SoC Platform

Cadence推出新一代CXL VIP和系統VIP工具

SMART世邁科技推出首款XMM CXL內存模塊

CXL協議和標準介紹, CXL2.0和3.0有什么新功能?

IPU和CXL如何提高數據中心的電源效率?

什么是CXL技術?CXL的三種模式、類型、應用

內存擴展CXL加速發展,繁榮AI存儲

推出CXL,Intel是為了什么?聊聊數據中心另一個新技術CXL

推出CXL,Intel是為了什么?聊聊數據中心另一個新技術CXL

評論