深夜醒來,翻開枕邊詩集,遙想當(dāng)年,蘇老舉杯邀歌,寫出了千古流傳的《水調(diào)歌頭》,“我欲乘風(fēng)歸去,又恐瓊樓玉宇,高處不勝寒。起舞弄清影,何似在人間。”如今想來,蘇老先生字里行間難掩對嚴(yán)寒天宮的向往,又終覺人間美好,我等后生晚輩做科研工作更是要腳踏實(shí)地。

在遙遠(yuǎn)的天宮,衛(wèi)星工作的環(huán)境非常惡劣。衛(wèi)星運(yùn)行期間,不可避免地遭遇地球輻射帶質(zhì)子、銀河宇宙線粒子、太陽宇宙線粒子轟擊,這些輻射粒子,極易引起電子元器件的性能退化、邏輯功能錯誤、狀態(tài)鎖定等,從而導(dǎo)致電子設(shè)備的功能錯誤及異常,進(jìn)而危害衛(wèi)星的功能發(fā)揮乃至運(yùn)行安全。

SRAM型FPGA屬于核心元器件,因此對SRAM型FPGA進(jìn)行抗輻照加固設(shè)計(jì)非常必要。今天貧道主要給大家布道一下SRAM型FPGA在軌會遇到的問題及其影響。

1SEE分類

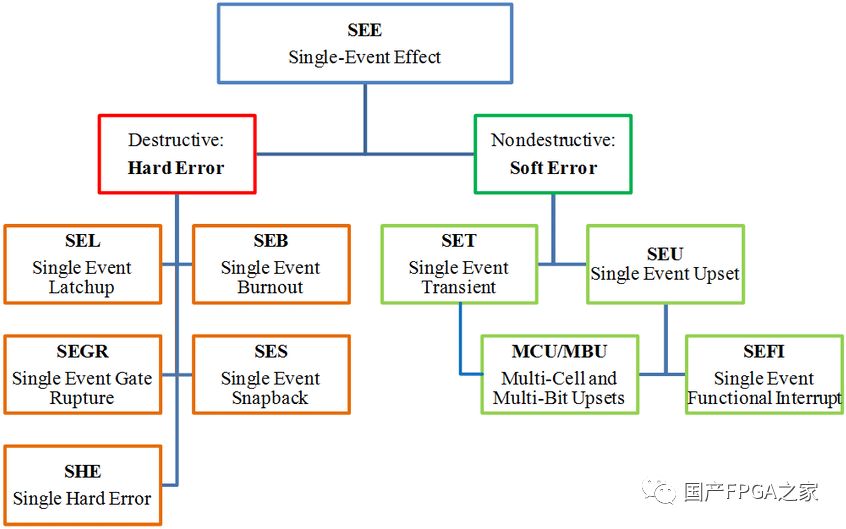

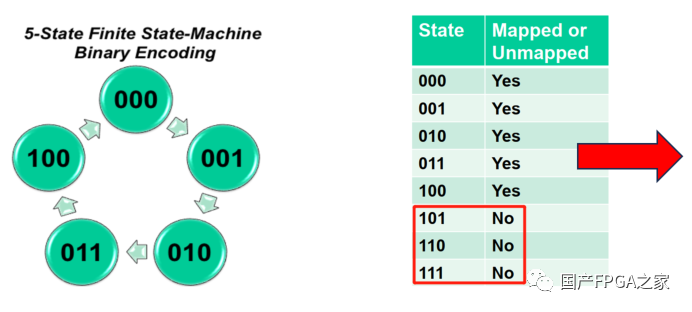

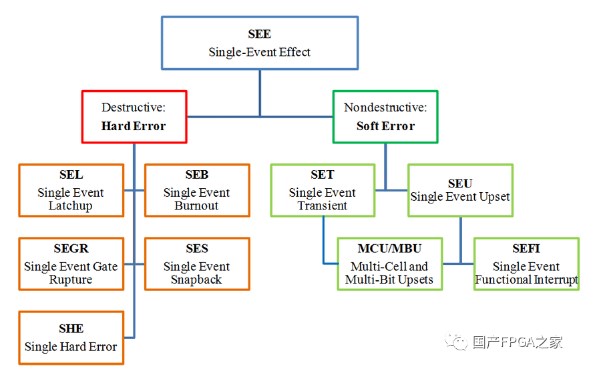

SRAM型FPGA空間應(yīng)用下面臨的主要問題是單粒子效應(yīng)和總劑量效應(yīng)。如圖1所示,單粒子效應(yīng)包括單粒子閂鎖SEL,單粒子翻轉(zhuǎn)SEU,單粒子瞬變SET和單粒子功能中斷SEFI。SEL屬于硬錯誤,可能會導(dǎo)致FPGA器件損傷。而SEU,SET和SEFI則屬于軟錯誤,一般不會對器件造成損傷,但會影響FPGA功能。

圖1 元器件單粒子效應(yīng)的分類

2TID

經(jīng)常聽說某國產(chǎn)元器件TID指標(biāo)大于100Krad or 150K rad,為啥要定義這個指標(biāo)呢?不同軌道的航天器遭受的年劑量是不一樣的,比如LEO軌道遭受的只有幾Krad[si],GEO軌道年劑量可能達(dá)到100Krad[si],而MEO軌道年劑量最高可達(dá)數(shù)百Krad[si]。

這里提到的指標(biāo)是典型的3mm鋁屏蔽下的年劑量,乘以衛(wèi)星的使用壽命,并考慮2~3倍的抗輻射設(shè)計(jì)余量(RDM),就是型號任務(wù)通常的抗總劑量要求。為了滿足總劑量的要求,可以通過設(shè)備機(jī)箱進(jìn)行屏蔽,也可以通過整星設(shè)計(jì),設(shè)備機(jī)箱結(jié)合其他結(jié)構(gòu)件組合屏蔽。一般到元器件層面總劑量指標(biāo)大于100Krad能滿足型號任務(wù)的需求。

3SEL

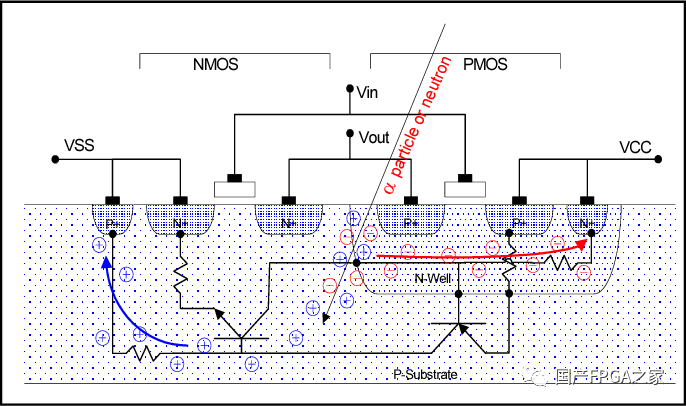

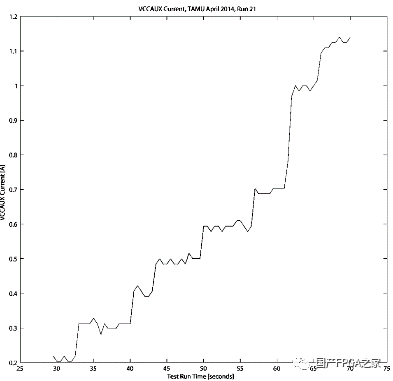

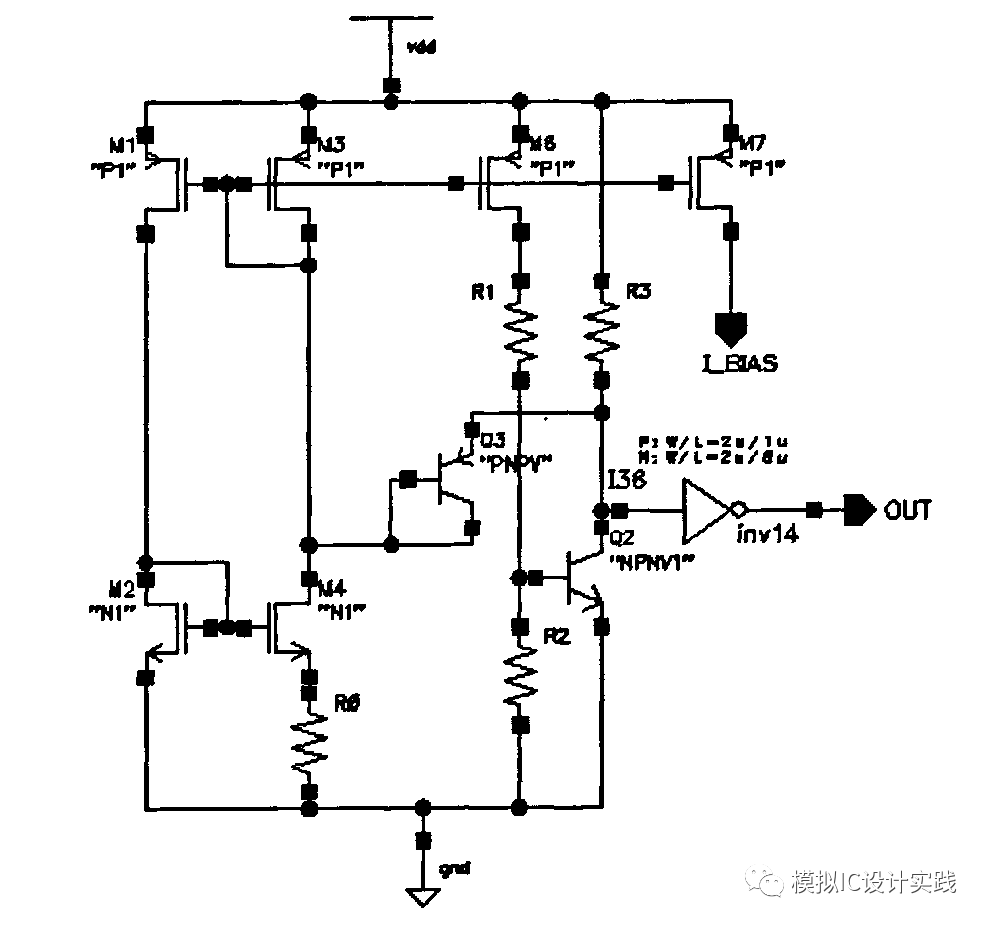

目前主流的SRAM型FPGA是CMOS工藝,由于天然的寄生效應(yīng),一個NMOS和一個PMOS串聯(lián)起來產(chǎn)生PNPN結(jié)構(gòu)。受單粒子效應(yīng)的影響,PNPN會處于導(dǎo)通狀態(tài)且不斷電會一直處于導(dǎo)通狀態(tài),影響管子使用壽命。隨著導(dǎo)通的管子數(shù)量增多,外在表現(xiàn)就是電流會階梯型上升。某國產(chǎn)宇航級的FPGA會在芯片內(nèi)部進(jìn)行SEL特殊加固設(shè)計(jì), 指標(biāo)達(dá)到84 Mev.cm^2/mg板級設(shè)計(jì)不需要考慮額外的抗SEL設(shè)計(jì)。

工業(yè)級的FPGA則必須要在板級設(shè)計(jì)中考慮電源的監(jiān)測和管理。由于電路的階梯型上升特點(diǎn),只對一級電源進(jìn)行監(jiān)測缺點(diǎn)是靈敏度不夠,發(fā)現(xiàn)不了潛在的閂鎖。最好對每路電源進(jìn)行監(jiān)測,提高靈敏度,一旦發(fā)生異常,采取斷電重啟。

圖2 CMOS電路中的寄生效應(yīng)

圖3 發(fā)生SEL后電流階梯型上升

4SEFI

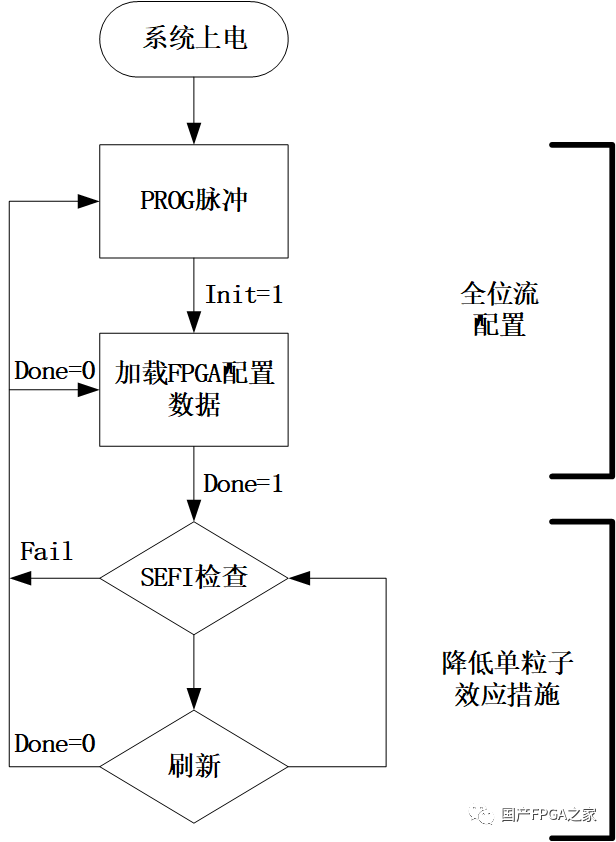

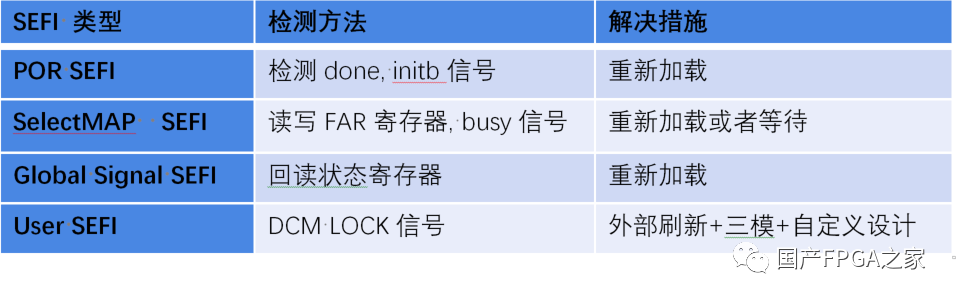

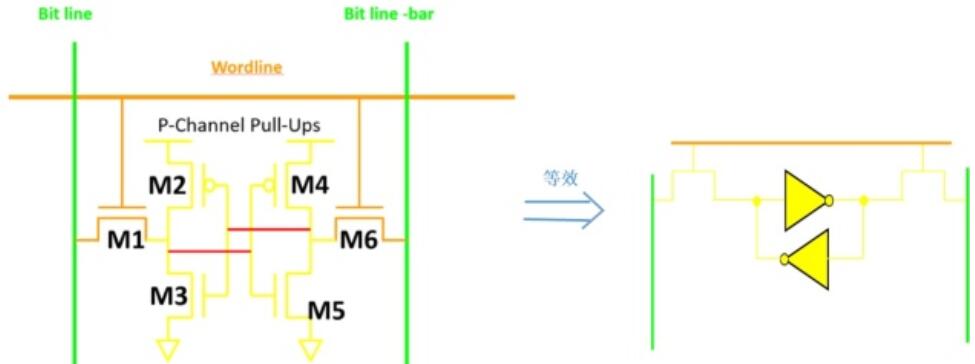

SEFI分為應(yīng)用級SEFI和器件級SEFI。如表1所示,器件級SEFI包括POR SEFI,SelectMAP SEFI,F(xiàn)AR SEFI和全局信號的SEFI。一般需要通過外部的刷新電路對器件級SEFI進(jìn)行監(jiān)測,并采取相應(yīng)的應(yīng)對措施。某國產(chǎn)宇航級的FPGA會在芯片內(nèi)部進(jìn)行SEFI特殊加固設(shè)計(jì),指標(biāo)達(dá)到37 Mev.cm^2/mg,極大增強(qiáng)了FPGA在軌穩(wěn)定運(yùn)行的能力。

圖4 刷新芯片監(jiān)測FPGA SEFI流程

表1 SEFI類型與解決措施

應(yīng)用級SEFI需要把由SEU導(dǎo)致的用戶層面邏輯功能異常刨除掉,專注一些基礎(chǔ)性的一般性的東西,否則應(yīng)用級SEFI就是一個模糊不清的概念。本文中應(yīng)用級SEFI指的是時鐘SET、復(fù)位毛刺和MMCM/PLL/DCM的功能異常,下面對應(yīng)用級SEFI分類進(jìn)行說明。

1)時鐘SET

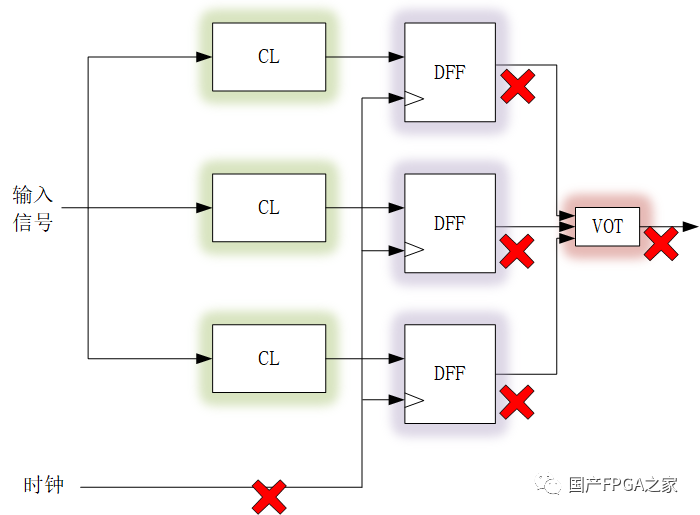

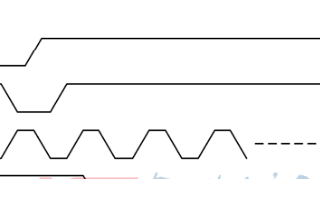

如圖5所示,盡管對電路做了TMR加固,但時鐘信號的SET會導(dǎo)致該時鐘域下的所有寄存器發(fā)生SEU,最終Voter判定結(jié)果錯誤,TMR加固失效。

圖5 時鐘毛刺

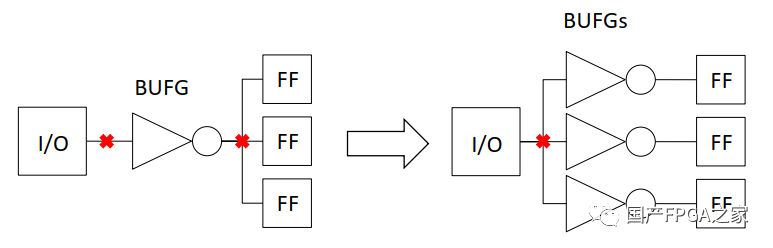

對時鐘網(wǎng)絡(luò)推薦采用GTMR策略,時鐘IO不做TMR,對BUFG做TMR。加固前單點(diǎn)失效路徑是整個時鐘routing,加固后單點(diǎn)失效路徑是IO到BUFGs的交匯處,通常單點(diǎn)失效路徑截面大為減少。

圖6 GTMR有效降低時鐘網(wǎng)絡(luò)SET概率

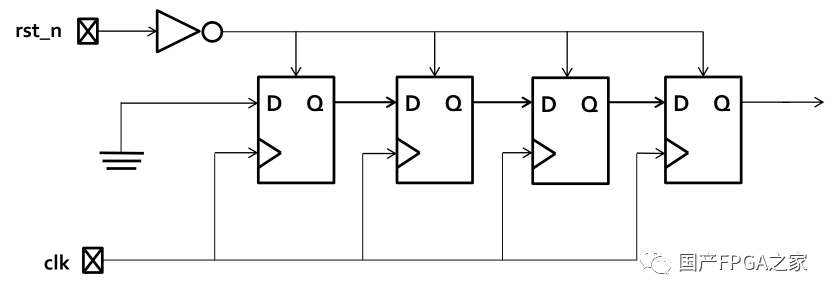

2)復(fù)位毛刺

FPGA加載時用GSR來控制寄存器和狀態(tài)機(jī)初值,因此并不需要額外產(chǎn)生復(fù)位信號來做初值控制。比如,不需要復(fù)位的寄存器(如數(shù)據(jù)流相關(guān)的寄存器)不設(shè)計(jì)外部復(fù)位,用GSR做初值控制。對復(fù)位毛刺很敏感的寄存器和狀態(tài)機(jī),可以改用同步復(fù)位,同步復(fù)位比異步復(fù)位消耗資源多一些,但比異步復(fù)位對毛刺敏感性低。

圖7 異步復(fù)位同步釋放電路

如果外部異步復(fù)位扇出較多的寄存器,可以用GTMR加固策略。復(fù)位信號經(jīng)過3個BUFG走全局時鐘專用網(wǎng)絡(luò),單路復(fù)位毛刺翻轉(zhuǎn)影響不了另外兩路復(fù)位信號對應(yīng)的寄存器。

3)MMCM/PLL/DCM

MMCM/PLL/DCM的LOCK信號為高并不代表功能一定正常,因此建議開發(fā)一種緩解方案,例如通過計(jì)數(shù)器來檢測MMCM/PLL/DCM輸出故障。一旦MMCM/PLL/DCM發(fā)生故障,進(jìn)行復(fù)位操作。

5SEU

單粒子翻轉(zhuǎn)SEU可以發(fā)生在FPGA任意的資源上,比如配置SRAM、配置邏輯電路、用戶邏輯DFF和塊存儲器等。

配置SRAM的SEU直接影響的是查找表LUT的值和互連資源的連接關(guān)系。查找表值的錯誤會導(dǎo)致用戶邏輯功能出錯,邏輯錯誤向下傳播還可能導(dǎo)致時序單元出錯。此外如果LUT用作了分布式RAM或者移位寄存器SRL,那么還會導(dǎo)致存儲數(shù)據(jù)出錯。

互連出錯可能導(dǎo)致用戶邏輯連接出錯,連接錯誤向下傳播可能導(dǎo)致時序單元出錯。互連出錯還可能導(dǎo)致互連產(chǎn)生短路,引起靜態(tài)功耗增加。

觸發(fā)器DFF的SEU會導(dǎo)致用戶邏輯狀態(tài)出錯和FSM狀態(tài)機(jī)出錯。流水寄存器狀態(tài)出錯的影響僅限于單個時鐘周期,因此影響比較小。FSM狀態(tài)機(jī)出錯可能會造成嚴(yán)重的影響。如圖8 所示,狀態(tài)機(jī)如果發(fā)生翻轉(zhuǎn)至為定義的狀態(tài),那會導(dǎo)致狀態(tài)機(jī)鎖死,用戶功能無法恢復(fù)。

圖8 狀態(tài)機(jī)發(fā)生SEU導(dǎo)致鎖死

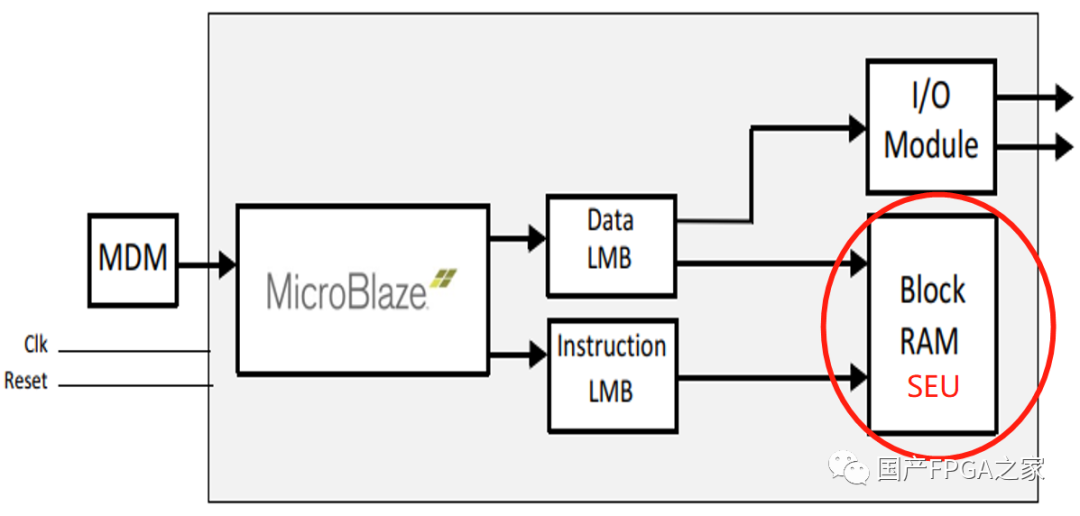

BRAM塊存儲器發(fā)生SEU可能會造成功能出錯。當(dāng)BRAM資源用作ROM,ROM存儲重要的參數(shù),重要參數(shù)發(fā)生錯誤會導(dǎo)致用戶功能受到嚴(yán)重影響。比如FPGA內(nèi)部跑軟核,程序存儲在FPGA內(nèi)部的BRAM資源中,BRAM程序區(qū)的SEU會導(dǎo)致指針亂跳,程序跑飛。

圖9 軟核存儲器發(fā)生SEU導(dǎo)致程序跑飛

戰(zhàn)術(shù)總結(jié)

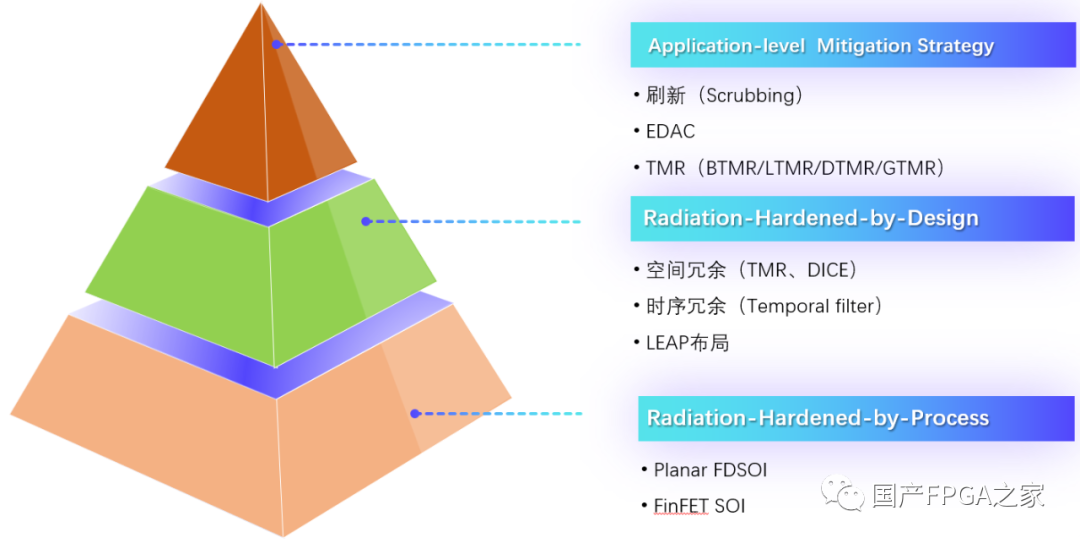

對于SRAM型的FPGA而言,單粒子效應(yīng)SEE可產(chǎn)生嚴(yán)重的影響。貧道今天給大家介紹了SEE的各個細(xì)分,包括SEL、SEFI、SEU和SET。那么針對不同細(xì)分,有什么解決方法,該采取什么樣的應(yīng)對措施,又如何驗(yàn)證措施的有效性呢?欲知后事如何、且聽下回分解。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評論