1、set_output_delay的本質

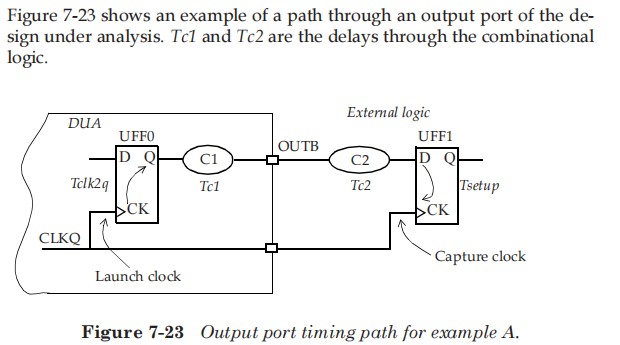

set_output_delay是對模塊output信號在模塊外部延遲的約束,本質上EDA工具會根據約束調整內部器件(UFF0)的類型,擺放位置以及組合邏輯(C1)以滿足約束要求,即EDA工具保證模塊DUA的UFF0的Tclk2q+Tc1延時能夠滿足約束要求。

約束指導原則:盡量照顧設計外部邏輯延時

max 正值盡量大

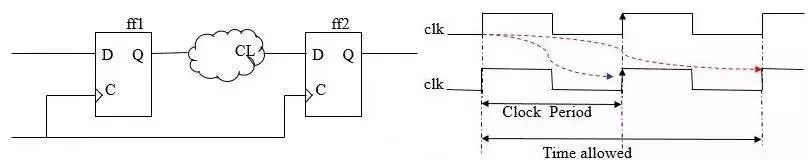

set_output_delay -max delay_vaule : delay_vaule 數值越大,對自身的約束越嚴格,對外部的要求越寬松,本質上是對setup time的約束。

set_output_delay -min delay_vaule : delay_vaule 可以是負值,delay_vaule 數值越小,需要自身的延時(Tclk2q+Tc1)越大,本質上是對hold time的約束。delay_vaule 為0 表示要求信號的自身的延時(Tclk2q+Tc1)至少要大于capture(UFF1)的hold time。

2、set_output_delay示意圖

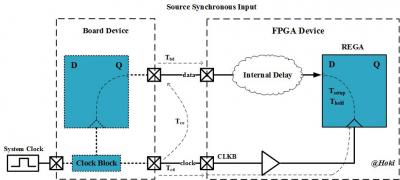

圖7-23顯示了DUA(the design under analysis )的輸出路徑。觸發器UFF0在DUA內部,并向DUA外部的觸發器UFF1提供數據。數據由UFF0的Q端輸出,經過組合邏輯C1,通過輸出端口OUTB輸出經過組合邏輯C2到達UFF1。觸發器UFF0和觸發器UFF1的采樣時鐘均為CLKQ。不考慮CLKQ時鐘偏移,該時鐘周期是兩個觸發器UFF0和UFF1之間采樣時間差。針對DUA輸出管腳OUTB設置的set_output_delay指的就是相對于時鐘CLKQ的Tc2延時加上UFF1的setup time延時。

set Tc2 3.9 set Tsetup 1.1 set_output_delay -clock CLKQ -max [expr Tc2 + Tsetup] [get_ports OUTB]

3、set_output_delay簡單案例

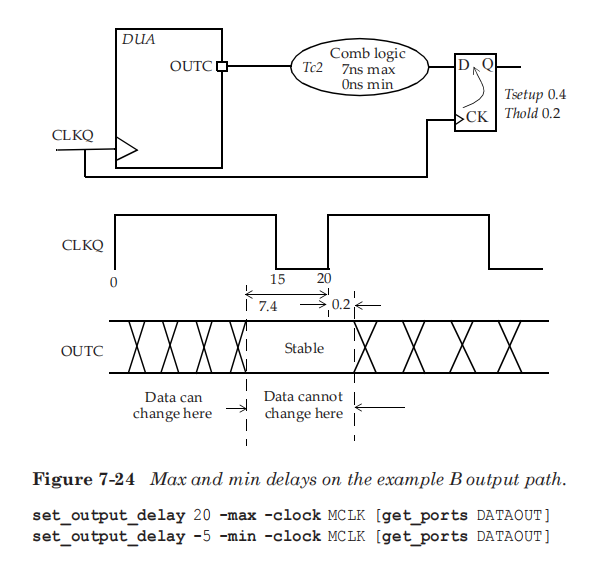

如圖所示,組合邏輯Tc2的延時范圍為0ns~7ns。外部觸發器的Tsetup 為0.4ns,Thold為0.2ns,因此外部路徑的最大延時為7.4ns (= max Tc2 plus Tsetup = 7 + 0.4),外部路徑的最小延時為-0.2ns (= min Tc2 minus Thold = 0 - 0.2)。(PS:12nm~5nm工藝,hold time和setup time僅僅只有幾十~十幾ps。)

create_clock -period 20 -waveform {0 15} [get_ports CLKQ] set_output_delay -clock CLKQ -min -0.2 [get_ports OUTC] set_output_delay -clock CLKQ -max 7.4 [get_ports OUTC]

審核編輯:劉清

-

EDA工具

+關注

關注

4文章

268瀏覽量

31803 -

觸發器

+關注

關注

14文章

2000瀏覽量

61181 -

延時器

+關注

關注

1文章

36瀏覽量

15118 -

Dua

+關注

關注

0文章

3瀏覽量

7144 -

CLK

+關注

關注

0文章

127瀏覽量

17177

原文標題:淺談時序:set_ouput_delay

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA設計約束技巧之XDC約束之I/O篇 (上)

Xilinx Vivado I/O延遲約束介紹

時序約束中如何精確找到匹配的template?

STM32上進行Delay延時的方法

詳解FPGA的時序input delay約束

FPGA的虛擬時鐘用于什么地方?

創建輸入輸出接口時序約束的竅門

介紹基本的sdc時序特例

怎樣查看input/output delay是否生效

set_output_delay的本質是什么?淺談set_ouput_delay時序

set_output_delay的本質是什么?淺談set_ouput_delay時序

評論