|| 前言

作者一直覺得,善待和重視每個產品。產品簡單,但是背后隱藏的東西卻很多。量產近十年的產品,因為缺芯問題也不得不改版。盡管不想改,但是市場供應非常嚴峻。那既然這樣,就正確一次到位,當然在市場面前發現一次到位幾無可能。因為復雜系統,缺一種芯片和缺十種芯片最終是一樣的,都無法有效生產出貨。

改板出來,變化有點大了,改板的話也就沒有改多少,cpu換了,電源全部換了,業務芯片全換了,增加了fpga,電源架構相比上板也基本全變了。除了產品大的架構,基本上和新產品一樣。

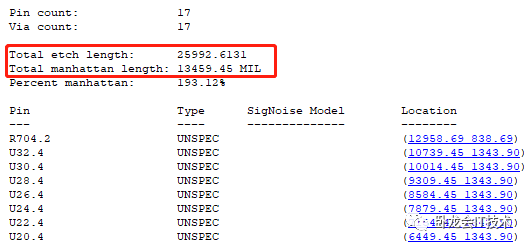

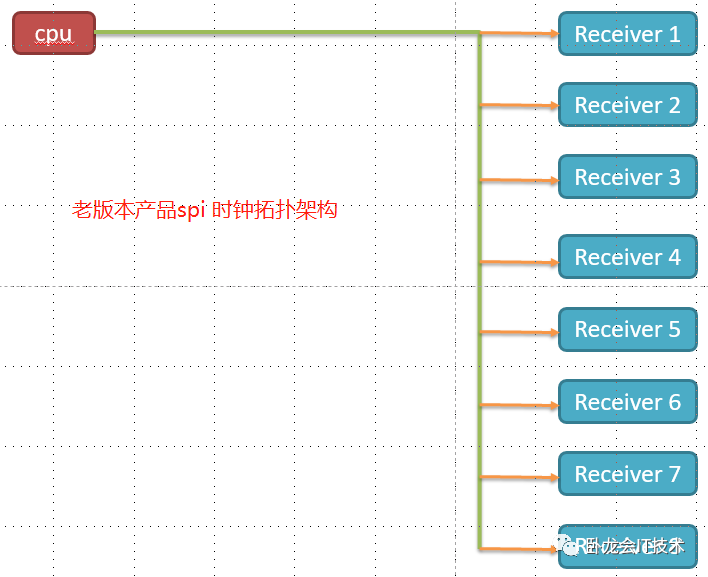

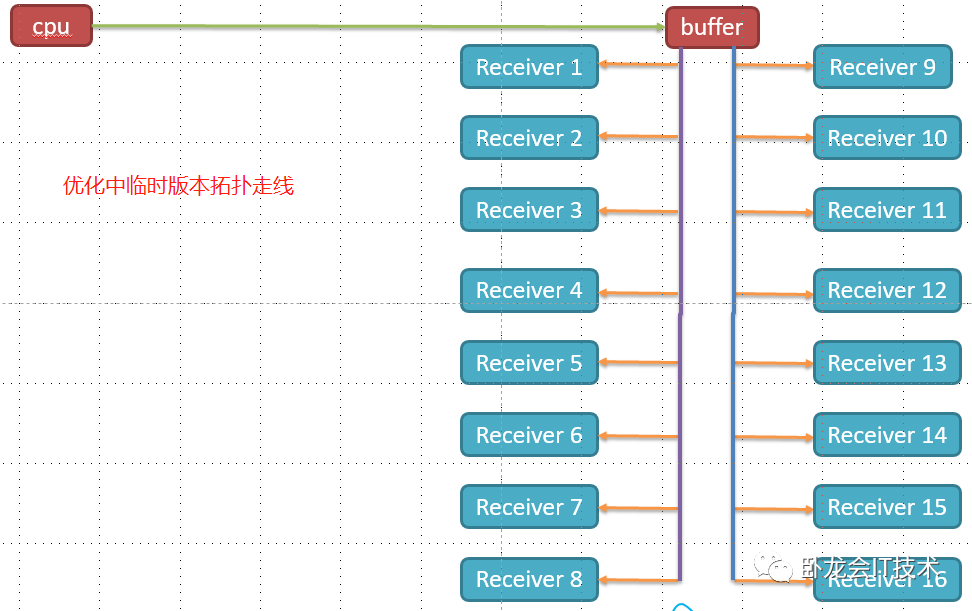

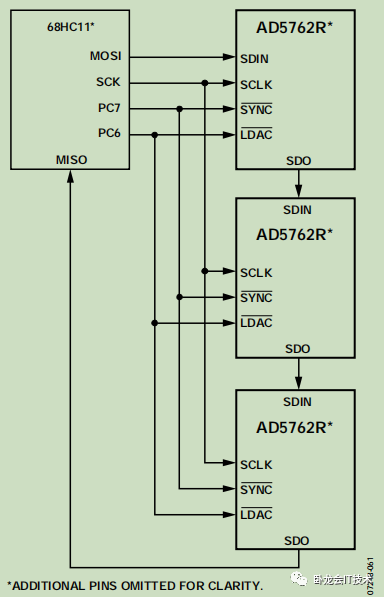

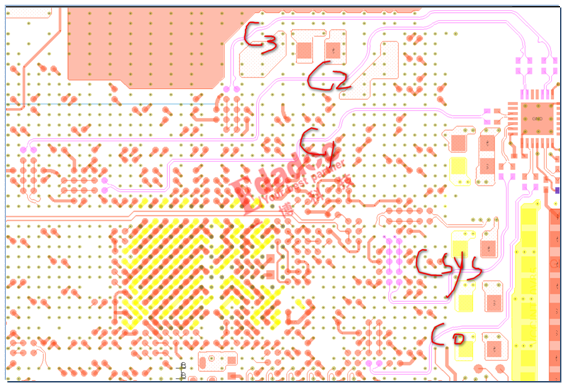

這不變化最大的其實最沒有引起注意的是,之前業務芯片是一顆負責兩路,新的芯片是一顆負責一路,然后就翻番了;然后spi從過去的1驅8改為1驅16了,因為芯片翻番走線尺寸也同時完全翻番(業務芯片QFN封裝且外圍電路高壓低壓配置一應俱全,單元電路面積較大)。

然后作者就覺得這事懸了,提出過優化拓撲的呼聲意見在群情激奮大干快干的口號中也被淹沒了。

但是信號質量饒過誰,這不就翻車了。

|| 正文

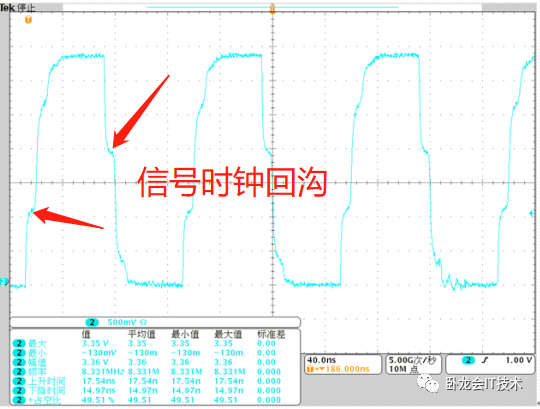

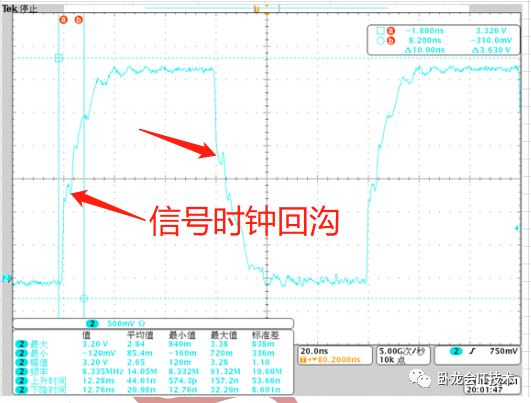

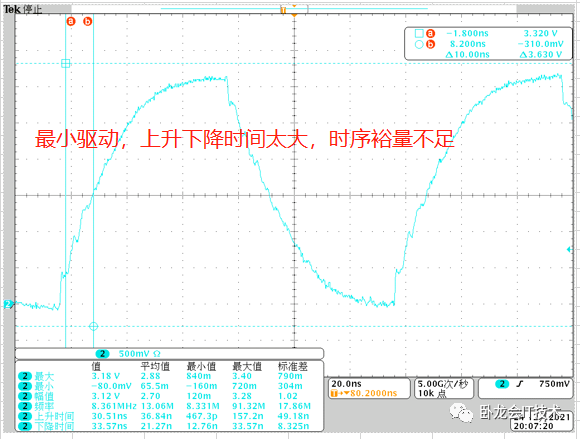

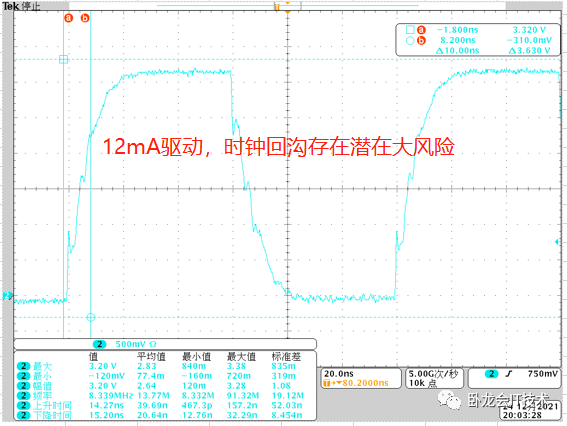

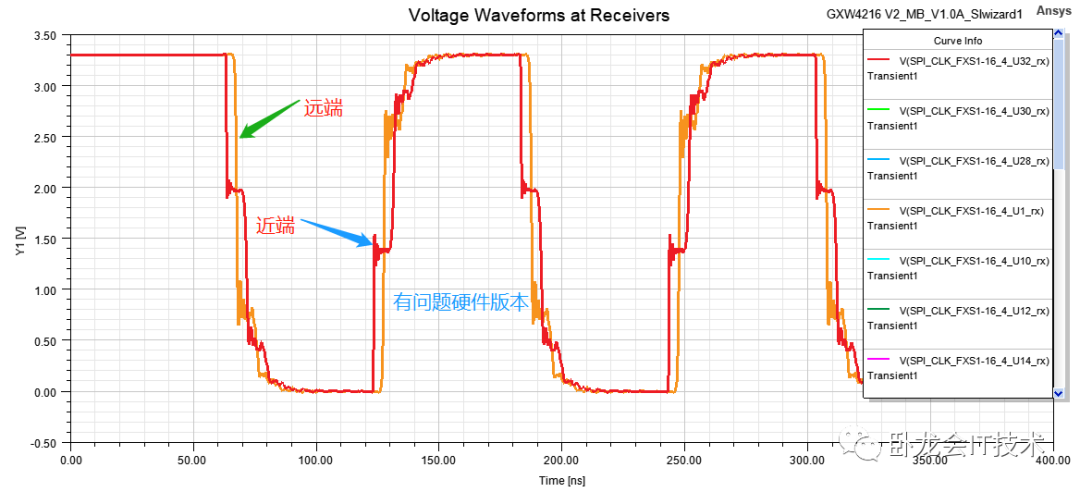

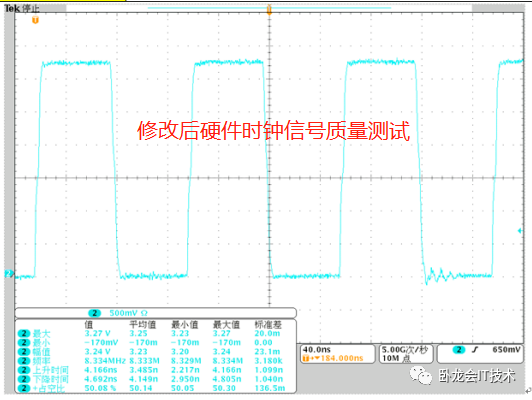

信號回溝不可怕,時鐘回溝就有點要老命了。正常情況我們是杜絕時鐘邊沿上有回溝,特別是在非穩定區間及臨界點上的回溝,更是絕不接受的。

事已至此,說啥都是虛的,作者提倡實際行動走起來!

邊仿邊測是王道,只仿不測是高手,只測不仿要么是高手(已經完全從理論經驗積累上杜絕了),只測不仿要么是渣渣(太過于沉迷淺顯的認知理解了)。

分析

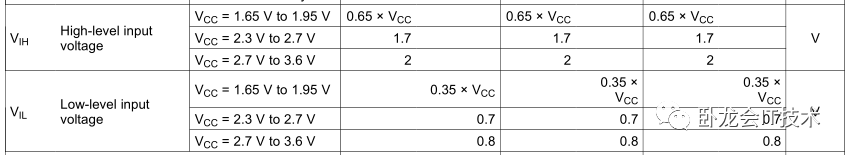

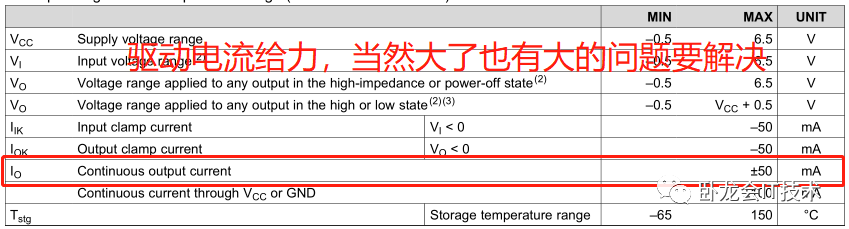

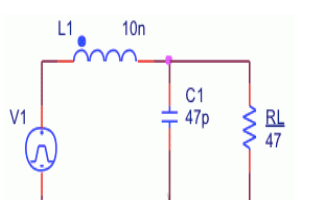

實際走線已看過,長得有點超出我的想象了,而且是一驅16啊,負載容性效應,走線寄生效應及反射疊加。近端的質量可想而知了,現在唯一的意思希望是提升驅動力看看能否明顯好轉點。

當然很不幸,驅動力已經是最大等級了。

分析設計

作者認為需要出大招了,上buffer。上buffer干嘛,縮短有效傳輸路徑,增加驅動能力解決邊沿時間過長及反射明顯影響。

器件有了,該搞拓撲了。拓撲是個啥,就是連連看。

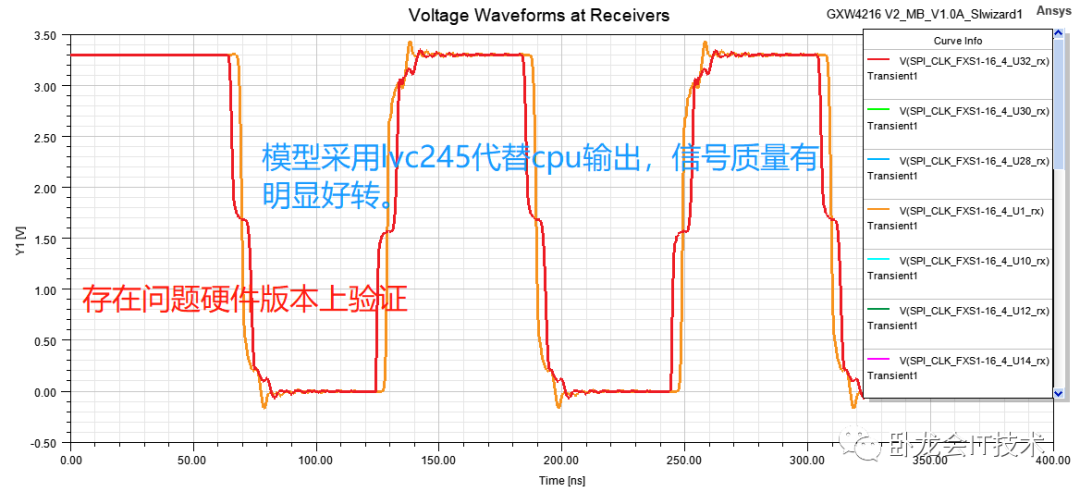

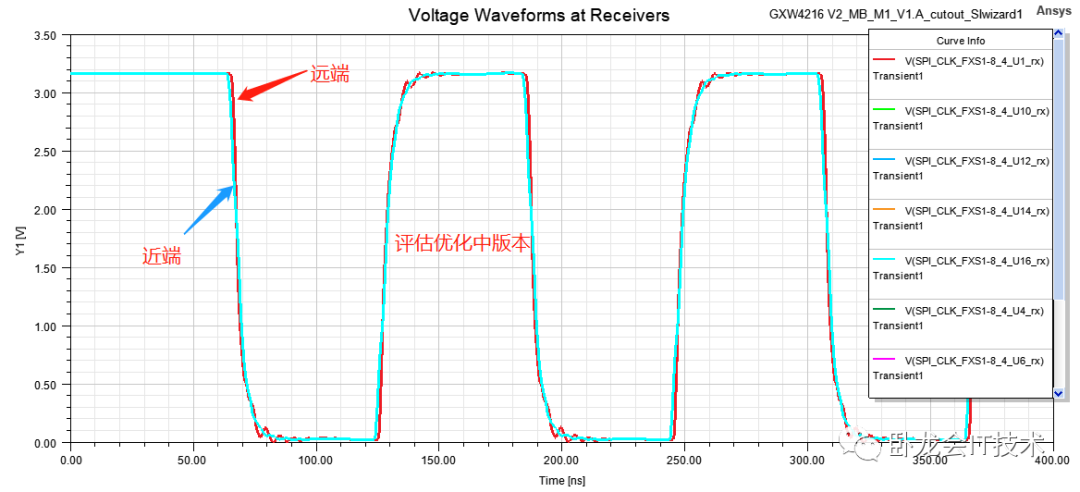

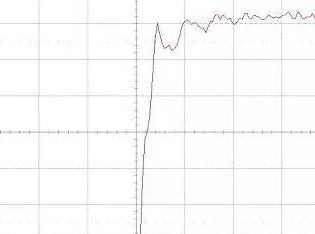

仿真結果

需要說明下,仿真過程中我們并沒有使用實際器件模型,都是使用友商相應模型代替評估。仿真和實際測試結果偏差稍大點原因如下:

驅動電流達不到實際處理器輸出12mA驅動,驅動電流最大10mA;

示波器探頭影響,盡管測試中已經使用有源探頭進行測試;

修改拓撲后,buffer輸出段業務芯片上的時鐘信號。信號質量明顯去除回溝且邊沿時間裕量較大。

|| 總結

作者一直認為存在即合理,其實在出現問題時候已經想到十多年前復雜通訊系統班上的jtag鏈接菊花鏈方式,但是很不幸使用的芯片不支持,但是芯片支持through模式,可以省卻部分網絡走線例如片選、多組輸入。但是距離這種菊花鏈拓撲還是多了點復雜程度需要考慮注意。

-

FPGA

+關注

關注

1630文章

21760瀏覽量

604382 -

芯片

+關注

關注

456文章

50967瀏覽量

424868 -

封裝

+關注

關注

127文章

7948瀏覽量

143114 -

時鐘

+關注

關注

11文章

1736瀏覽量

131591 -

信號完整性

+關注

關注

68文章

1410瀏覽量

95528

原文標題:|| 總結

文章出處:【微信號:電子工程師筆記,微信公眾號:電子工程師筆記】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時鐘信號測試有回溝怎么辦?測試點位置與芯片DIE分析

淺談PCB設計的高速信號跨溝及信號回流

信號反射的幾個基本問題分析

時鐘信號回溝與測試點位置有關嗎

簡析上電過程中的上電回溝

實際開發中的紋波噪聲過沖回溝的詳細介紹

時鐘有回溝?什么原因會導致信號波形邊沿的回溝?

電源上電回溝

信號時鐘回溝分析設計

信號時鐘回溝分析設計

評論