眾所周知,華為是全球備受矚目的“專利大戶”,從5G/6G到通信設備,再到手機芯片、操作系統、自動駕駛、EVS等均有涉及。而最近,華為又新增了多條專利信息,其中一項便是關于芯片封裝和制備方法的,這將有利于提高芯片的性能。

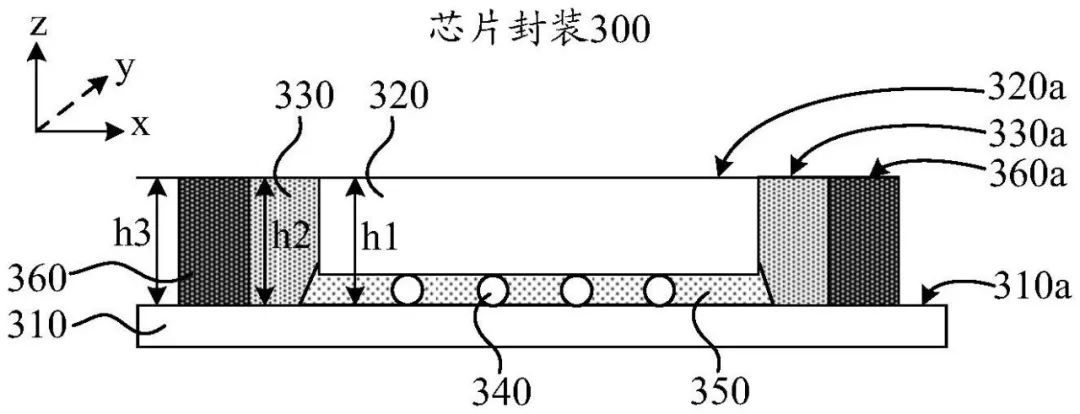

根據企查查公開的信息顯示,這項新專利的名稱為“一種芯片封裝以及芯片封裝的制備方法”,申請日期為2020年12月16日,申請公布日為2023年8月4日,申請公開號為CN116547791A。

▲圖片來源:企查查

據悉,這是一種用于簡化芯片堆疊結構及其形成方法的制造技術。

根據專利摘要顯示,該芯片封裝包括基板、裸芯片、第一保護結構和阻隔結構;該裸芯片、該第一保護結構和該阻隔結構均被設置在該基板的第一表面上;該第一保護結構包裹該裸芯片的側面,該阻隔結構包裹該第一保護結構背離該裸芯片的表面,且該裸芯片的第一表面、該第一保護結構的第一表面和該阻隔結構的第一表面齊平。

其中,該裸芯片的第一表面為該裸芯片背離該基板的表面,該第一保護結構的第一表面為該第一保護結構背離該基板的表面,該阻隔結構的第一表面為該阻隔結構背離該基板的表面。

通過這種芯片堆疊結構的設計,旨在簡化芯片堆疊結構的制備工藝,并有利于提高生產效率。該專利對于芯片封裝行業具有重要意義,可以加快芯片制造的速度、降低生產成本,并提高芯片的性能和可靠性。

▲專利原理示意圖

該專利一經曝光,立即引起了網友的廣泛關注和討論,例如“華為可以將兩塊14nm制程芯片堆疊在一起,實現與7nm制程芯片相似的性能和功耗”的說法也隨之流傳開來。

不過,華為官方已經多次證實這是謠傳。因為“通過芯片疊加工藝讓兩塊14nm芯片達到7nm水平”這樣的說法本身就是錯誤的,芯片堆疊技術方案難題包含了熱管理、電氣互聯、封裝和測試、制造技術等多個方面,要想完成這些并非易事。

此外,兩塊14nm芯片堆疊在一起,還要功耗跟7nm相當,暫且說可以組合,但這樣實現后也是通過降頻。要知道,14nm芯片達到7nm的性能水平就必須功耗翻倍,同時還得進一步擴大芯片面積才能塞下更多的晶體管,這顯然脫離了芯片發展規律。

雖然這項新專利實現不了7nm工藝,但卻展現了華為在芯片領域的研發實力和創新能力,也為全球芯片行業的發展提供了更多新的可能。

據統計,截至2022年,華為持有超過12萬項有效授權專利,是中國國家知識產權局和歐洲專利局2021/2022年度專利授權量排名第一的公司,也是2022年中國PCT國際專利申請量全球第一的公司。在研發方面,華為2022年研發支出超過1600億元,近十年研發支持超過9700億元。正是這些大手筆研發投入,讓華為在各領域都能遙遙領先,為消費者帶來不斷迭代的新功能、新技術。

未來,隨著研發投入的持續積淀,以及最新芯片堆疊封裝專利技術的普及與應用,我們可以期待華為將在芯片領域取得更多的技術突破,為中國芯片的發展注入更多新的動力。

-

芯片

+關注

關注

459文章

51910瀏覽量

433432 -

華為

+關注

關注

216文章

34903瀏覽量

254542 -

堆疊

+關注

關注

0文章

36瀏覽量

16762

原文標題:突破!華為首次公開芯片堆疊專利,7nm有戲了?

文章出處:【微信號:robotqy,微信公眾號:機械自動化前沿】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

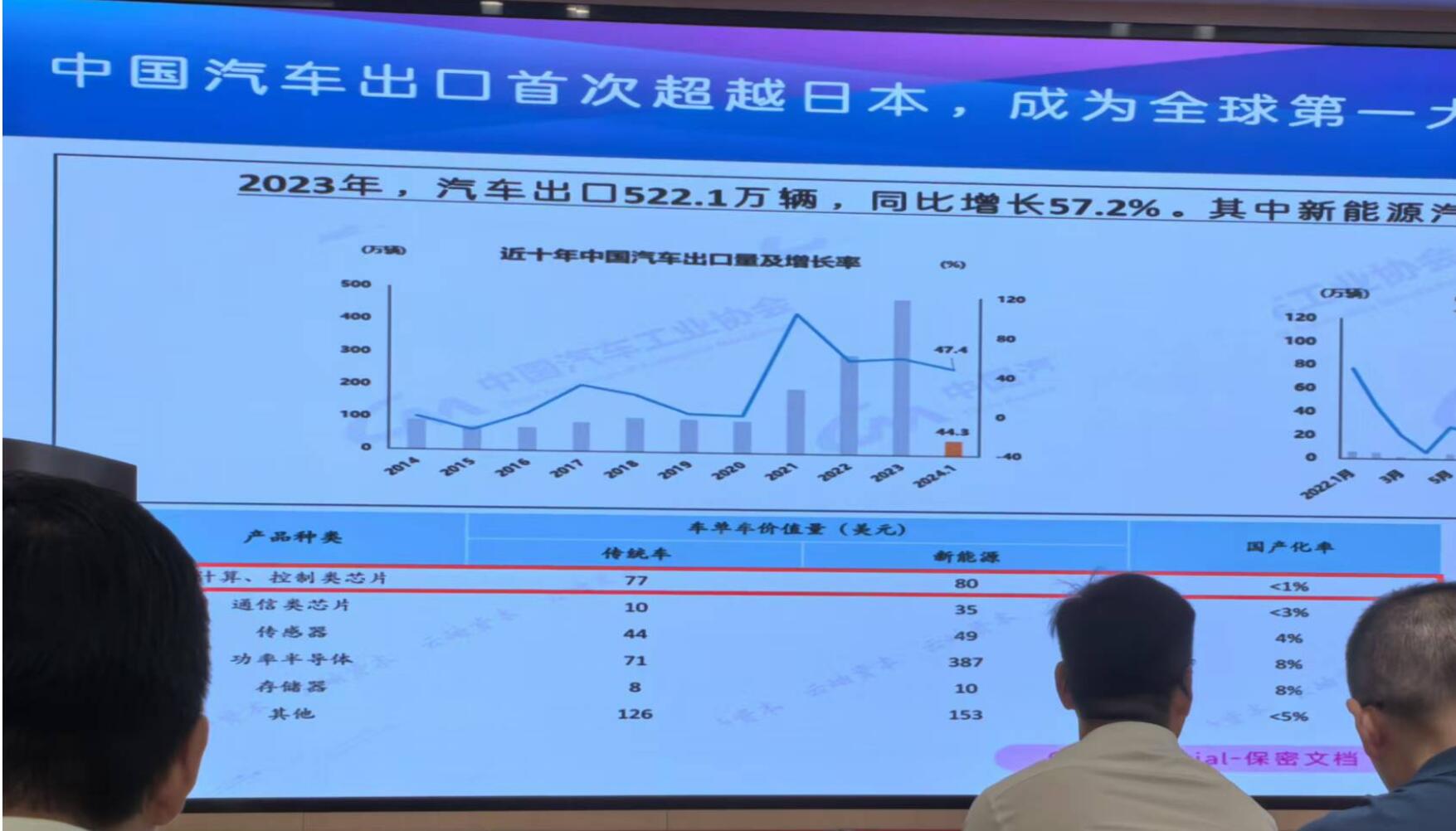

國產化率不足5%!國產7nm座艙芯片最新有哪些突破?

北京市最值得去的十家半導體芯片公司

TSV三維堆疊芯片的可靠性問題

華進半導體榮獲中國專利優秀獎

蘋果公開新專利:可折疊設備鉸鏈

今日看點丨 傳蘋果2025年采用自研Wi-Fi芯片 臺積電7nm制造;富士膠片開始銷售用于半導體EUV光刻的材料

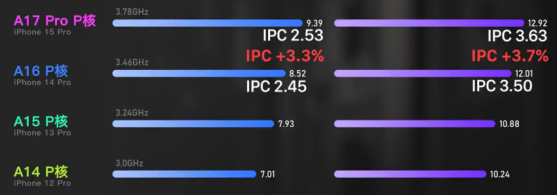

所謂的7nm芯片上沒有一個圖形是7nm的

雙芯片磁性位置傳感器中堆疊芯片和并排芯片實施方案之間的比較

華為首款視覺智駕SUV,問界M7 Pro上市

臺積電產能分化:6/7nm降價應對低利用率,3/5nm漲價因供不應求

存內計算——助力實現28nm等效7nm功效

評論