隨著科技領(lǐng)域國際競爭不斷加劇,我國的關(guān)鍵核心技術(shù)“卡脖子”問題依然存在,在芯片設(shè)計(jì)領(lǐng)域追求自主研發(fā)的需求尤為迫切。

RISC-V作為一種開源的指令集架構(gòu),被業(yè)內(nèi)看作是一個(gè)可繞開西方壟斷的技術(shù)方向。其開放特性使得任何人都可以使用和定制RISC-V,有助于提升芯片設(shè)計(jì)的靈活性和自主能力。

然而,需要注意的是,在實(shí)際應(yīng)用中仍存在一些風(fēng)險(xiǎn)和技術(shù)挑戰(zhàn)。包括生態(tài)系統(tǒng)成熟度、性能和功耗、標(biāo)準(zhǔn)化和互操作性以及安全性和可靠性等方面。

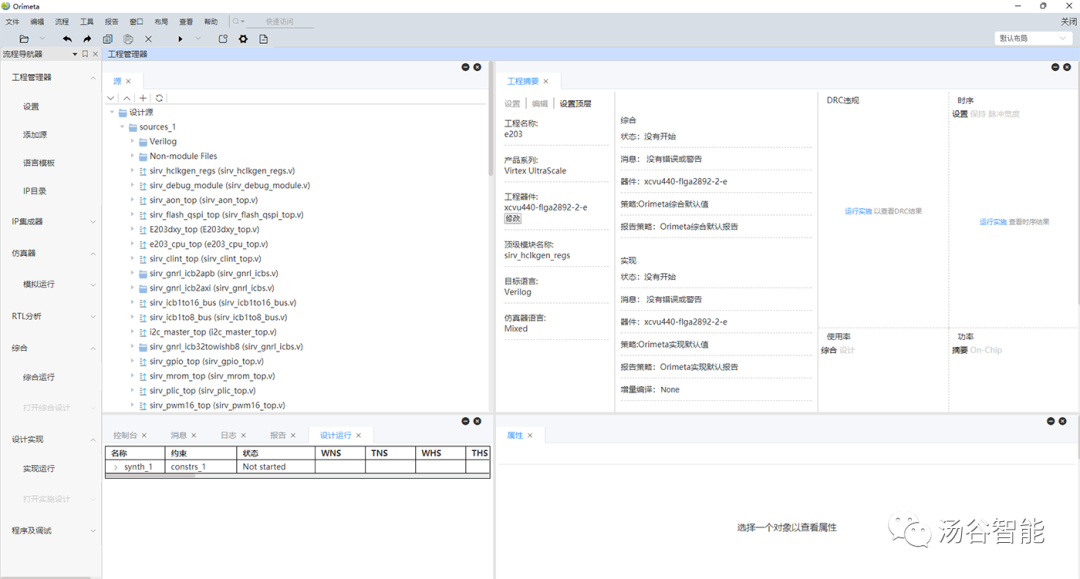

針對(duì)這些挑戰(zhàn),湯谷智能推出了專門針對(duì)RISC-V場景的全棧原型驗(yàn)證解決方案。該解決方案包括硬件平臺(tái)Logic Giant系列原型驗(yàn)證平臺(tái)和配套的開發(fā)工具Orimeta集成開發(fā)軟件。

通過該解決方案,可以實(shí)現(xiàn)從指令集架構(gòu)到軟件生態(tài)的全面驗(yàn)證,支持不同指令集架構(gòu)如RISC-V、ARM以及自研指令集架構(gòu)。

同時(shí),該解決方案提供了基于Linux操作系統(tǒng)的軟件工具鏈、驅(qū)動(dòng)程序和應(yīng)用程序開發(fā)的支持。這將有助于加快RISC-V的采用和發(fā)展,并克服當(dāng)前面臨的挑戰(zhàn)和問題。

圖2-Orimeta集成開發(fā)軟件截圖

全棧原型驗(yàn)證解決方案的優(yōu)勢在于加快進(jìn)度、節(jié)約成本、與時(shí)俱進(jìn)、系統(tǒng)驗(yàn)證和靈活配置。

這些特點(diǎn)使得它們能夠幫助處理器開發(fā)人員在早期階段發(fā)現(xiàn)和解決潛在問題,提高產(chǎn)品性能和可靠性。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19286瀏覽量

229853 -

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

52文章

8236瀏覽量

146369 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1019瀏覽量

54897 -

Linux操作系統(tǒng)

+關(guān)注

關(guān)注

0文章

54瀏覽量

11053 -

RISC-V

+關(guān)注

關(guān)注

45文章

2277瀏覽量

46159

原文標(biāo)題:RISC-V全棧原型驗(yàn)證解決方案-基于湯谷logic giant?系列原型驗(yàn)證平臺(tái)

文章出處:【微信號(hào):湯谷智能,微信公眾號(hào):湯谷智能】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Nordic推出最新物聯(lián)網(wǎng)原型驗(yàn)證平臺(tái)Thingy:91 X

EM儲(chǔ)能網(wǎng)關(guān)&ZWS智慧儲(chǔ)能云應(yīng)用(5) — 削峰填谷策略接入介紹(二)

數(shù)字芯片設(shè)計(jì)驗(yàn)證經(jīng)驗(yàn)分享文章 實(shí)際案例說明用基于FPGA的原型來測試、驗(yàn)證和確認(rèn)IP——如何做到魚與熊掌兼

解鎖SoC “調(diào)試”挑戰(zhàn),開啟高效原型驗(yàn)證之路

快速部署原型驗(yàn)證:從子卡到調(diào)試的全方位優(yōu)化

谷東科技成功實(shí)現(xiàn)分子鍵合技術(shù)驗(yàn)證

大規(guī)模 SoC 原型驗(yàn)證面臨哪些技術(shù)挑戰(zhàn)?

西門子數(shù)字化工業(yè)軟件推出Veloce CS硬件輔助驗(yàn)證和確認(rèn)系統(tǒng)

美光全系列車規(guī)級(jí)解決方案已通過高通汽車平臺(tái)驗(yàn)證

fpga原型驗(yàn)證平臺(tái)與硬件仿真器的區(qū)別

fpga原型驗(yàn)證流程

湯谷智能發(fā)布全棧RISC-V硬件仿真加速系統(tǒng)方案

原型平臺(tái)是做什么的?proFPGA驗(yàn)證環(huán)境介紹

基于湯谷logic giant?系列原型驗(yàn)證平臺(tái)介紹

基于湯谷logic giant?系列原型驗(yàn)證平臺(tái)介紹

評(píng)論