在Verilog和SystemVerilog中經常需要在使用變量或者線網之前,期望變量和線網有對應的初始值,為此經常會在過程塊或者連續賦值語句中對相關變量或者線網進行初始化,這樣的初始化我們稱之為“顯式初始化”,其實除了這種初始化操作方式之外,也有人會在變量和線網聲明的同時進行初始化,這種初始化方式成為“隱式初始化”,只不過在使用“隱式初始化”時經常會出現一些不期望的結果,下面將通過示例對這些初始化操作進行說明。

1 線網初始化

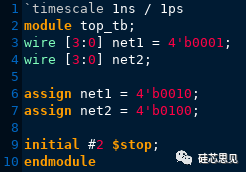

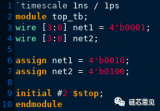

【示例】

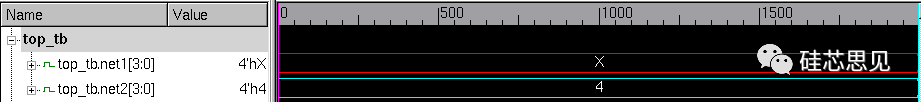

【仿真結果】

示例中,net1在聲明的同時進行了賦值操作(初始化),同時在代碼中通過連續賦值語句對net1又進行了賦值(與聲明時初始化的值不同),此時從仿真結果可以觀測到net1顯示結果為不定態;net2在聲明時并沒有進行賦值操作,對其的賦值操作發生在連續賦值語句中,從仿真結果可以看到net2并沒有出現不定態,其獲得了確切的數值。

出現線網net1這種現象的主要是因為線網聲明時的“初始化”是一種“隱式的連續賦值語句”,并且在仿真過程中會一直保持,當有其他語句驅動該線網時,此時相當于對該線網進行了多驅動,在仿真波形上就會表現出不定態。那么對于變量的初始化操作是否也會像示例中net1這樣的情況呢?請看下例。

2 變量初始化

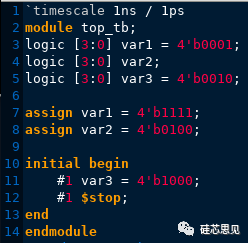

【示例】

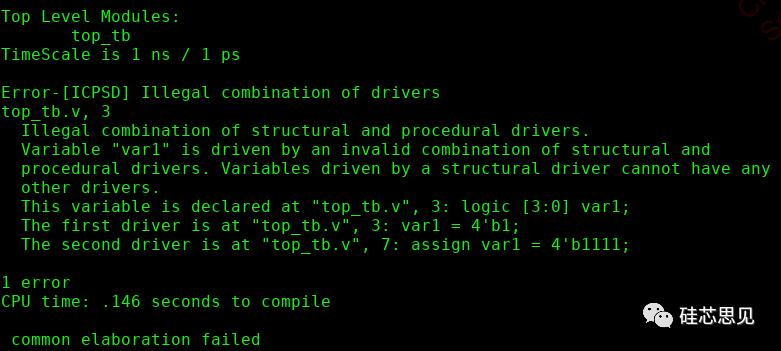

【仿真結果】

編譯報錯,從報錯信息上可以知道,var1同時被過程塊代碼和結構級代碼驅動,這主要是因為var1為變量,在聲明時進行了初始化,同時又在連續賦值語句中也進行了賦值,從而導致了編譯錯誤,即錯誤原因是變量聲明時進行了初始化的話,那么該變量不能作為連續賦值語句的賦值對象進行使用,即SystemVerilog中不允許對于同一變量在連續賦值語句和過程語句中同驅動。對上述代碼進行修改,如下。

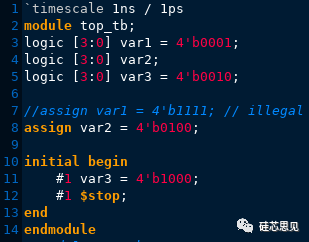

【示例】

【仿真結果】

示例中,var1聲明時進行了初始化,但是本例中并沒有其他連續賦值語句對該變量的值進行修改驅動,所以此時var1中的值在仿真過程中一直保持,var2在聲明時沒有進行初始化,其值由連續賦值語句驅動為4’b0100,可見,SystemVerilog中變量可以用于連續賦值語句中,var3聲明時進行了初始化,但在過程塊(initial)中對var3進行了修改,此時var3的值更新為了過程塊中的值,由此我們可以看出,變量在聲明時的初始化先于過程塊的執行,其次變量聲明時的初始化并不具有持續性,會被后續的賦值操作所更新,否則就會出現多驅動情況,即并不具有“隱式連續賦值的特點”。

通過上述示例可以看到,線網聲明時的初始化實際上是一種“隱式連續賦值語句”,其“初始化”具有持續性,而變量聲明時的初始化會被后續的賦值操作更新,并不具有持續性,同時需要注意如果變量在聲明時進行初始化,此時該變量不能同時被連續賦值語句驅動。

審核編輯:劉清

-

仿真器

+關注

關注

14文章

1018瀏覽量

83746 -

VaR

+關注

關注

0文章

39瀏覽量

11341 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8235

原文標題:verilog/systemverilog 中隱藏的初始化

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

手機模塊初始化向導

objc源碼中NSObject如何進行初始化

uboot和內核里phy的初始化_內核里的雙網絡配置及phy的初始化

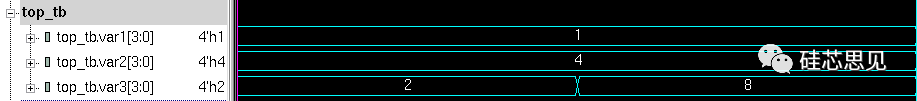

8253初始化程序分享_8253應用案例

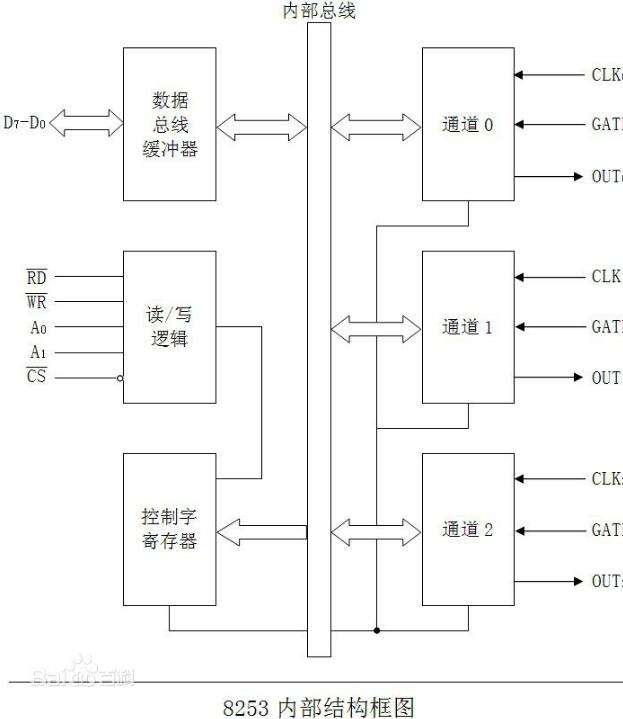

在51平臺下初始化文件的引入導致全局變量無法初始化的問題如何解決

verilog/systemverilog中隱藏的初始化說明

verilog/systemverilog中隱藏的初始化說明

評論