為什么需要復位樹

復位信號在數字電路里面的重要性僅次于時鐘信號。對一個芯片來說,復位的主要目的是使芯片電路進入一個已知的,確定的狀態。主要是觸發器進入確定的狀態。

在一般情況下,芯片中的每個觸發器都應該是可復位的。在某些情況下,當在高速應用程序中使用流水線觸發器(移位寄存器觸發器)時,為了實現更高的性能設計,可能會從某些觸發器中消除復位。這種類型設計需要在復位激活期間,運行預先確定數量的時鐘周期,以使芯片處于已知的狀態。

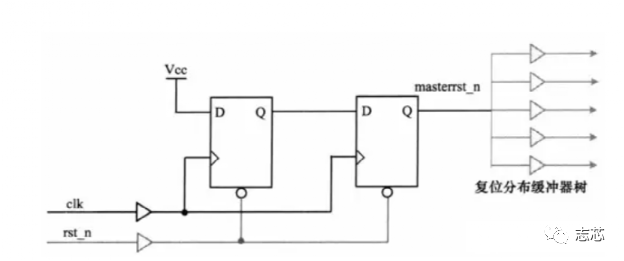

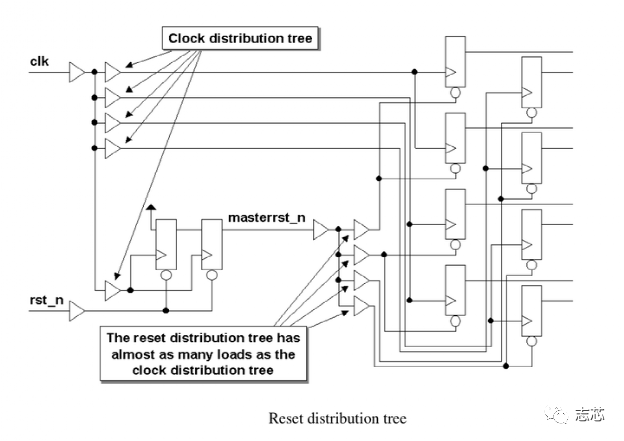

復位樹是復位電路形成的類似于時鐘樹的樹狀結構,因為復位信號也要送到各個寄存器上。復位樹和時鐘樹一樣應該引起重視,因為典型的數字電路中,reset的負載和clock的負載數量一般是相當的。不管是同步復位還是異步復位,對復位樹都是有時序要求的。

復位信號用什么電路產生

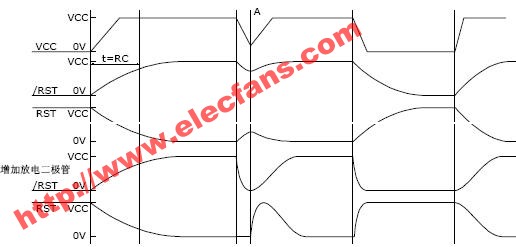

POR是上電復位電路(Power-On Reset),廣泛應用于各種數字電路和系統中。上電復位電路就是在電源電壓上升過程中一直保持低電平(有效復位電平),直到電源電壓穩定達到系統規定的正常工作電壓后才迅速產生一個高電平(無效復位電平)。在復位信號電平發生翻轉時,電源所上升到的電壓值被稱作復位電路的“起拉電壓”。

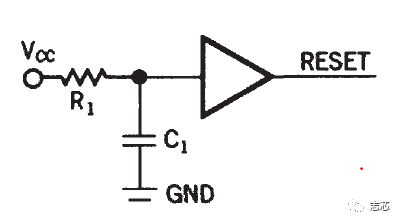

上圖是一種基于RC網絡實現的簡單復位電路,復位信號在上電開始的一段時間內保持低電平接近零伏),隨著電源電壓Vcc通過電阻R1對電容器C1充電,當電容上極板的電壓達到一定高位后觸發后級門電路,復位信號隨即輸出高電平。

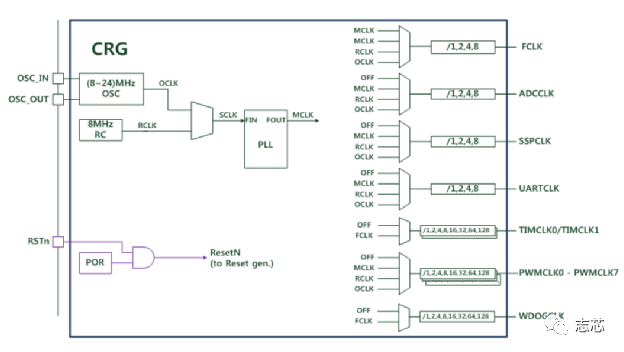

如下圖所示,復位信號源也是CRG(時鐘復位信號產生模塊)的重要組成部分。

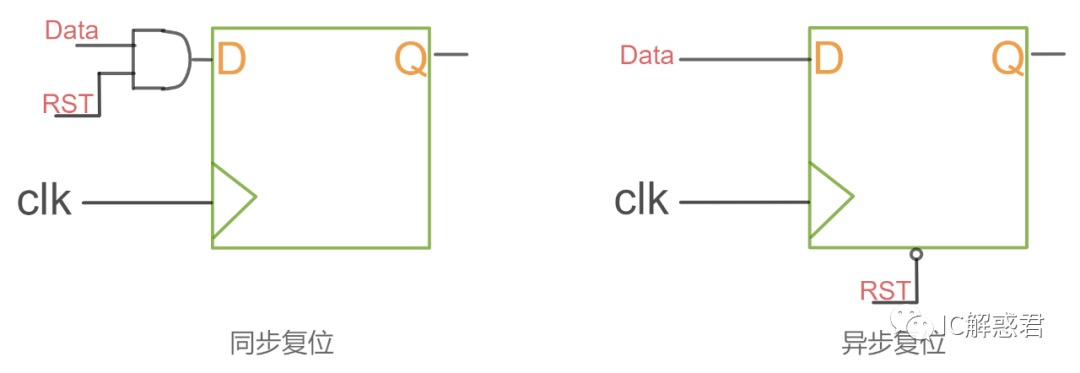

復位實現主要有同步復位和異步復位兩種方式,兩種方式使用的寄存器結構和復位樹結構都不相同。

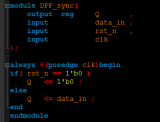

同步復位

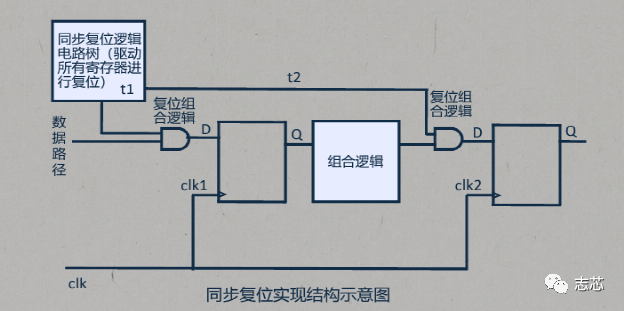

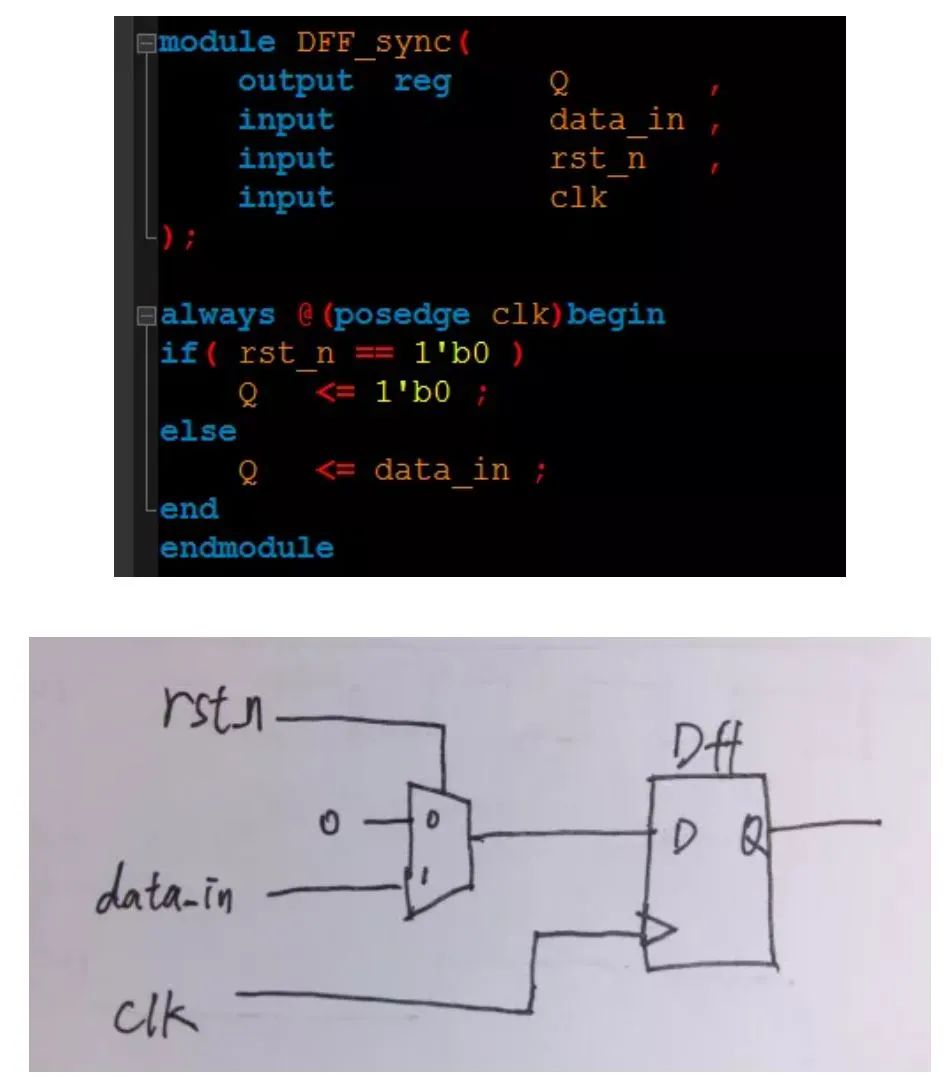

同步復位采用下圖所示的寄存器電路,復位信號和數據信號通過組合邏輯接入到寄存器的數據輸入端,二者共用時鐘信號,復位也必須在時鐘有效沿下才能生效。

同步復位的優點:1、同步復位可以確保整個電路為同步電路;2、同步復位對復位信號毛刺不敏感,可以過濾掉復位信號的毛刺;3、同步復位相比于異步復位而言會綜合成更小的觸發器。

同步復位的缺點:1、同步復位要求復位脈沖信號要盡可能的寬,必要的時候需要對復位信號進行脈沖展寬,從而保證復位信號能夠出現在時鐘有效沿到來時;2、同步復位需要保證時鐘存在才能對電路進行復位,在某些使用時鐘門控節約功耗的場景下,由于沒有時鐘,可能會造成復位失效,此時必須使用異步復位。

異步復位

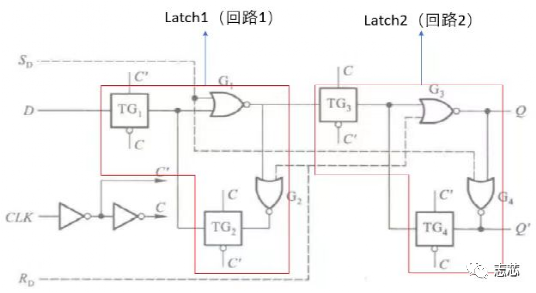

下圖是一種異步復位采用的寄存器結構,將邊沿觸發器的非門替換為或非門。SD=RD=0時為工作態;SD=1&RD=0為置1態;SD=0&RD=1為置0態。該寄存器的復位生效不需要依賴于時鐘有效沿。

異步復位的優點:1、異步復位具有最高優先級,不管有沒有時鐘都能正確復位,綜合工具能夠自動推斷出異步復位而不需要添加額外綜合參數。2、生產商所提供的單元庫中帶有異步復位觸發器,可以保證數據路徑干凈,可以減小路徑延時,緩解時序緊張。

異步復位的缺點:1、異步復位使整個系統不再是同步系統,異步復位在時鐘有效沿附近釋放需要滿足移除時間和恢復時間的時序要求,如果不滿足即會出現亞穩態。2、異步復位對復位信號的毛刺比較敏感,需要設計專門的毛刺過濾器來對復位毛刺進行消除。

異步復位,同步恢復:所有的復位信號是用兩集同步器的第二級 reg送到后來的reg系列,這個reg和后面的所有reg系列都有recover和removal timing check。

一般復位信號送到芯片內部之前需要經過同步處理,一般使用兩級同步器。兩級同步器是1防止reset中的glitch導致reg錯誤反轉;

2防止復位移除時剛好處于時鐘跳變邊沿導致亞穩態,所以把reset信號通過同步電路變成clk clock這個group中的一級信號,同步化。

所以對于異步復位同步恢復,復位時鐘樹不用單獨處理,同步器的reg和功能reg自己做平。復位時時鐘頻率也可以拉低,比較容易滿足時序要求。

審核編輯:劉清

-

電容器

+關注

關注

64文章

6227瀏覽量

99756 -

IC設計

+關注

關注

38文章

1297瀏覽量

104023 -

電源電壓

+關注

關注

2文章

989瀏覽量

24007 -

觸發器

+關注

關注

14文章

2000瀏覽量

61192 -

同步器

+關注

關注

1文章

98瀏覽量

14649

原文標題:數字IC設計中的復位樹

文章出處:【微信號:IC學習,微信公眾號:IC學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

復位信號是什么意思?復位信號的作用?詳解Xilinx FPGA復位信號那些事

為什么需要復位樹?復位信號用什么電路產生?

為什么需要復位樹?復位信號用什么電路產生?

評論