讀取txt文件數據

將數據寫入txt文件

??第2篇的題材是文件的讀寫控制,仿真時經常需要從文件中讀取測試激勵,還要將仿真結果存取在文件中供其它程序讀取調用。

讀取txt文件數據

??示例代碼如下:

integer i; //數組坐標 reg [9:0] stimulus[1:data_num]; //數組形式存儲讀出的數據 initial begin $readmemb("SinIn.txt", stimulus); //將txt文件中的數據存儲在數組中 i = 0; repeat(data_num) begin //重復讀取數組中的數據 i = i + 1; din = stimulus[i]; #clk_period; //每個時鐘讀取一次 end end

??用“數組”來表述Verilog HDL中的定義并不準確,但對大多數人來說應該更好理解。可以將stimulus視作一個存儲器,[9:0]定義了數據的位寬,[1:data_num]定義了存儲器的深度。stimulus的定義應該與txt文件中的數據相匹配。txt文件中每行存儲一個數據,則上述定義對應的是txt中存儲了data_num個數據,每個數據的最大位寬為10bit。

??讀取二進制格式的文件是用系統任務readmemb;讀取十六進制格式文件使用readmemb;讀取十六進制格式文件使用readmemh。其命令為$readmemb(“filename”, mem_name),將filename中的內容讀取到mem_name中。

??注意filename文件路徑中應該用反斜杠“/”,與windows系統中的文件路徑使用的“”不同。如果不指定路徑,向上面程序一樣直接寫文件名字,那么該文件必須和testbench文件在同一路徑下。

??repeat(n) begin … end中的內容應該根據設計的需要編寫。

將數據寫入txt文件

??示例代碼如下:

integer file_out;

initial

begin

file_out = $fopen("mixer_out.txt");

if (!file_out) begin

$display("can't open file");

$finish;

end

end

wire signed [19:0] dout_s = dout;

wire rst_write = clk & rst_n; //復位期間不應寫入數據

always @ (posedge rst_write)

$fdisplay(file_out, "%d", dout_s);

??寫入文件需要先用$fopen系統任務打開文件,這個系統任務在打開文件的同時會清空文件,并返回一個句柄,如果句柄為0則表示打開文件失敗。

??如果原來不存在該文件,則會自動創建該文件。

??打開文件之后便可以用得到的句柄和KaTeX parse error: Expected 'EOF', got '&' at position 55: …printf函數的用法很像。

上面的程…fdisplay`,都會在數據后插入一個換行符。

審核編輯:劉清

-

存儲器

+關注

關注

38文章

7511瀏覽量

163980 -

二進制

+關注

關注

2文章

795瀏覽量

41681 -

HDL

+關注

關注

8文章

327瀏覽量

47409 -

十六進制

+關注

關注

2文章

32瀏覽量

37773 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8277

原文標題:Testbench編寫指南(2)文件的讀寫操作

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

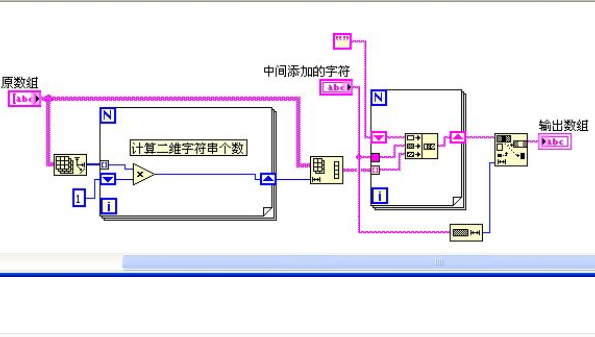

關于labview讀取EXCEL文件數據的問題

用matlab讀取txt文件數據

Verilog Testbench怎么寫 Verilog Testbench文件的編寫要點

FPGA入門必備:Testbench仿真文件編寫實例詳解

編寫高效Testbench的指南和示例

Testbench編寫指南(2)讀取txt文件數據

Testbench編寫指南(2)讀取txt文件數據

評論