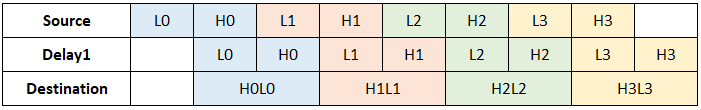

在FPGA設計中,我們經常會碰到這樣的情形:從快時鐘域到慢時鐘域完成位寬轉換,這時,這兩個時鐘是同步的。例如:源時鐘是400MHz,數據位寬為4;目的時鐘為200MHz,數據位寬為8,這樣源時鐘域和目的時鐘域的吞吐率是一致的。這種位寬轉換可直接通過寄存器采樣實現,時序關系如下圖所示。

圖中Source為源時鐘域(400MHz)4位數據,L0代碼0號數據的低4位,H0代表0號數據的高4位,L1代表1號數據的低4位,H1代表1號數據的高4位,依此類推。Delay1為源時鐘域經一級流水寄存器的輸出結果。Destination為目的時鐘域(200MHz)8位數據。

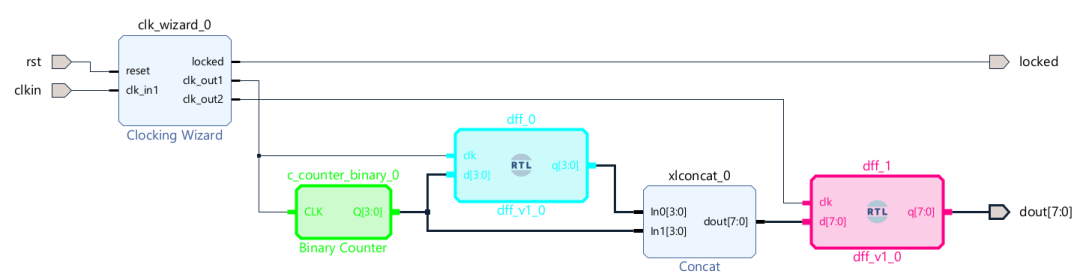

我們很容易搭建此電路,如下圖所示。圖中綠色計數器為400MHz時鐘域計數器,產生源端4位數據,藍色模塊為源端流水寄存器,紅色模塊為目的端采樣寄存器。

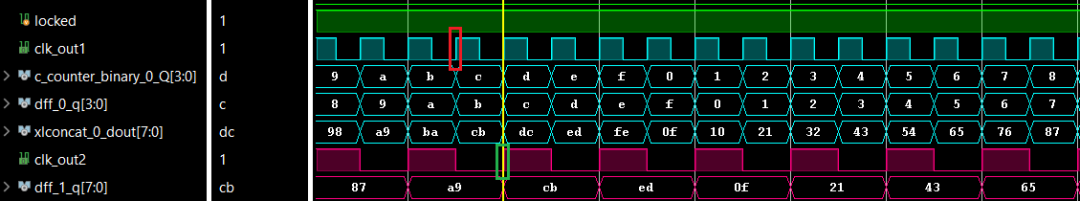

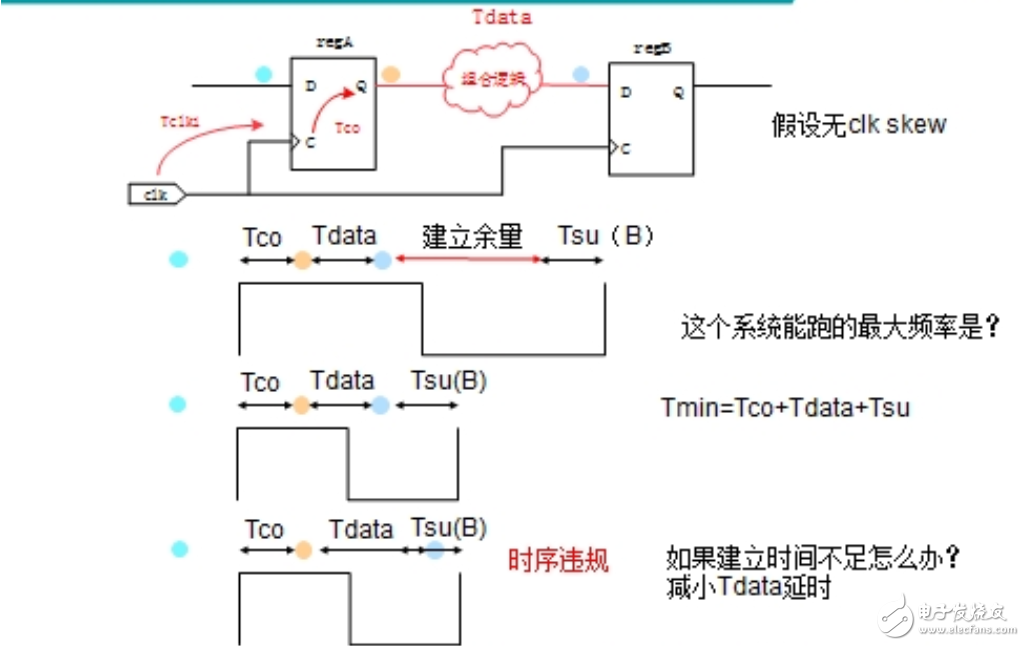

在這種情況下,能否使用多周期路徑約束呢?這里我們看一下數據的發起沿和捕獲沿的位置,如下圖所示。圖中紅色方框為數據發起沿(400MHz),綠色方框(黃色標記線所在位置)為捕獲沿,兩者相差一個400MHz時鐘對應的時鐘周期。因此,并不滿足多周期規則。這時,我們只用做常規的時鐘周期約束即可,工具會自動將這里的跨時鐘域按400MHz進行約束。

那么快時鐘域到慢時鐘域在什么情況下可以用多周期路徑進行約束呢?本質上,多周期路徑是指數據的采樣率(SampleRate)是按慢時鐘域的速率進行變化,其變化周期在慢時鐘域是單周期(一個時鐘周期變化一次),而在快時鐘域是多周期(多個時鐘周期變化一次)。滿足這種情形就可以判斷為多周期路徑。

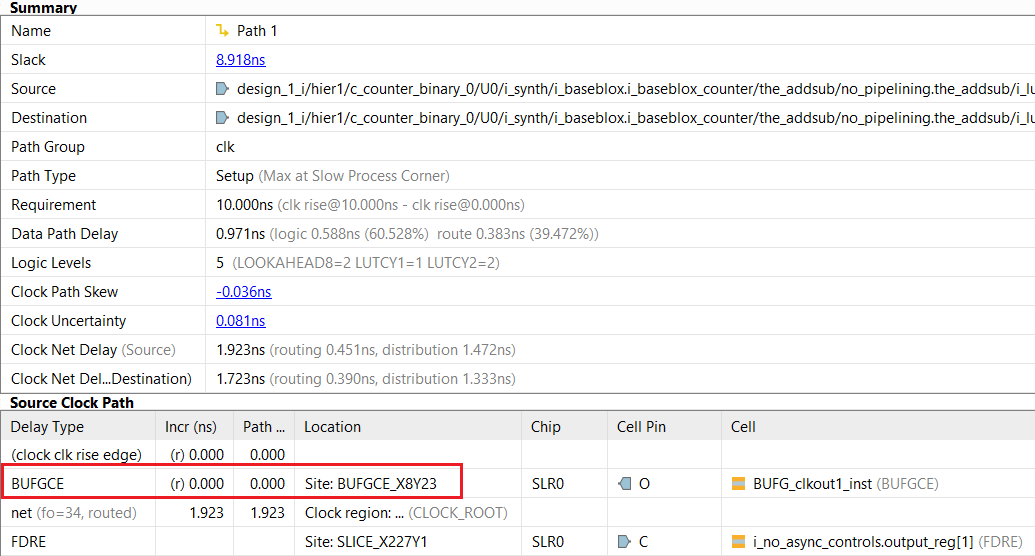

有時在設計中會有測試模塊,或者出現這樣的狀況:模塊1和模塊2都工作在相同的時鐘下,該時鐘會根據設計的需要頻率會發生變化,但無論怎么變化模塊2只要滿足最低時鐘頻率的要求即可。因此,這時可對模塊2放松時序要求。只按照最低時鐘頻率約束即可。問題是只要定義了全局時鐘(通過create_clock創建),該時鐘就會在模塊2中發生作用。如何覆蓋這個約束呢?如果仍通過create_clock創建時鐘,選項-period的值為時鐘周期最大值(對應最低頻率),但以模塊2作為頂層,指定該約束針對的對象為模塊2是否可行呢?答案是否定的,因為這時時序分析工具會把BUFG作為時鐘的起點,而不是把全局時鐘管腳作為起點。

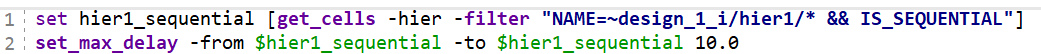

一種可行的方法是用set_max_delay,其對象是模塊2內的所有時序單元(模塊2內只有一個時鐘),采用如下方式約束。第一條Tcl命令用于獲取模塊2內所有的時序單元。

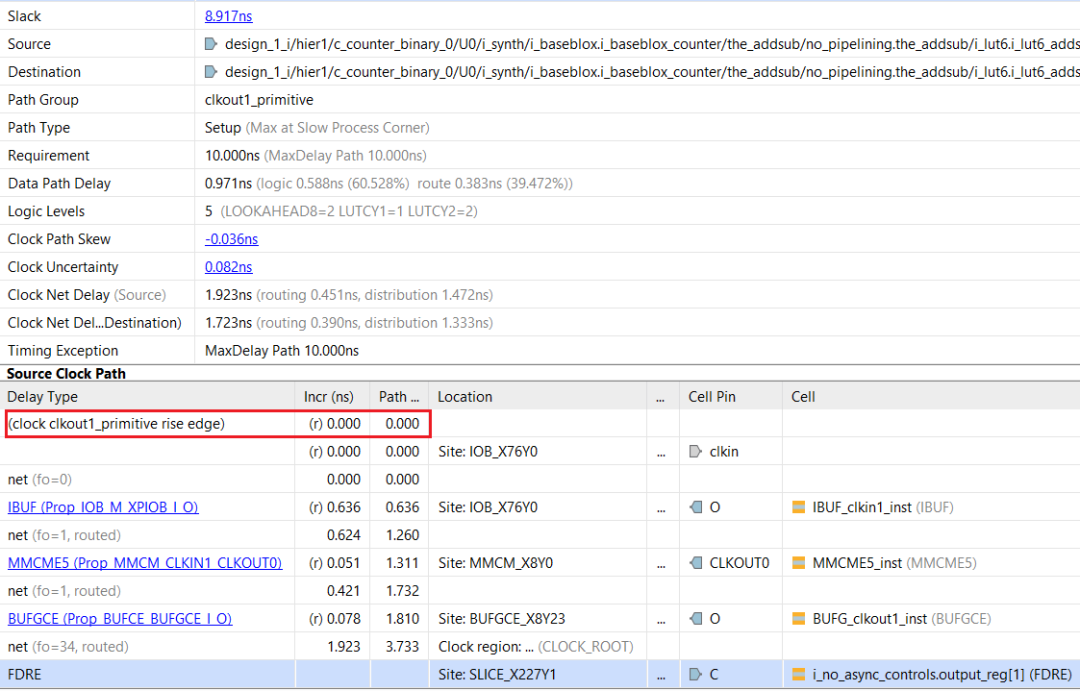

這時就可以看到時鐘的起點是期望的位置了。這里可以看到set_max_delay的一個用法就是覆蓋create_clock創建的約束。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1638文章

21861瀏覽量

609966 -

FPGA設計

+關注

關注

9文章

428瀏覽量

26889 -

寄存器

+關注

關注

31文章

5394瀏覽量

122254 -

時鐘

+關注

關注

11文章

1765瀏覽量

132391

原文標題:這兩種情形該怎么約束

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

請問TPS74201和TPS74301這兩種LDO的主要區別是什么?

多路電子負載在這兩種電源測試中的優勢是什么

常見的ARM架構分為兩種一種是M系列另外一種是A系列,這兩種有什么區別啊?

終于看懂了iic與spi這兩種通訊協議了

FPGA時序約束分析余量

評論