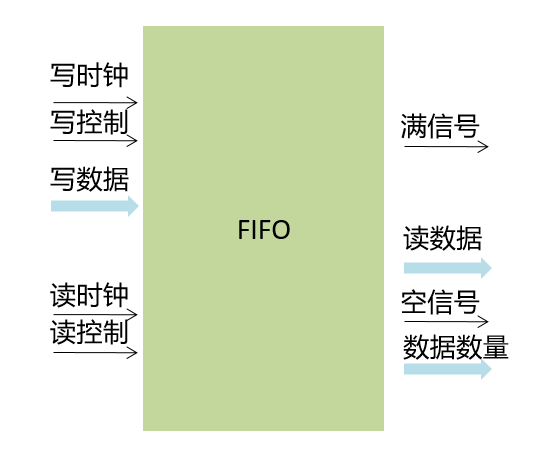

上文XILINX FPGA IP之FIFO對XILINX FIFO Generator IP的特性和內部處理流程進行了簡要的說明,本文通過實際例子對該IP的使用進行進一步的說明。本例子例化一個讀數據位寬是寫數據位寬兩倍的FIFO,然后使用讀時鐘頻率:寫時鐘頻率=2:3,進行簡單的FIFO跨時鐘域操作。

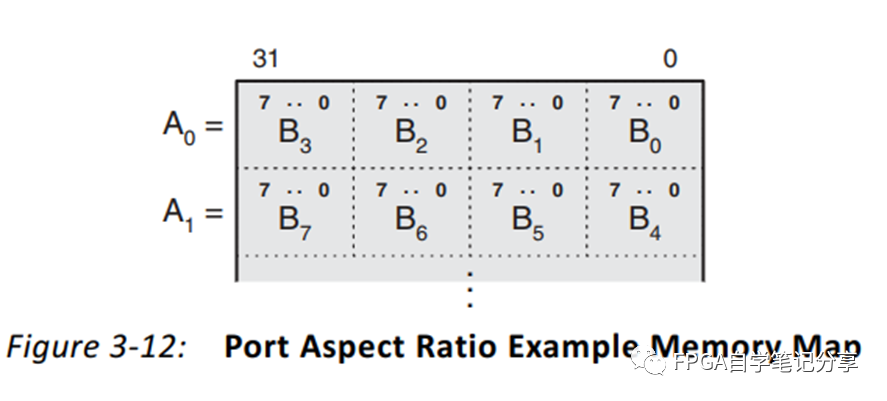

首先了解一下FIFO讀寫位寬不一致時數據的擺放方式:

讀數據位寬是寫數據位寬的4倍的情況下的寫如何讀出數據擺放方式如下:

寫數據位寬是讀數據位寬的4倍的情況下的寫如何讀出數據擺放方式如下:

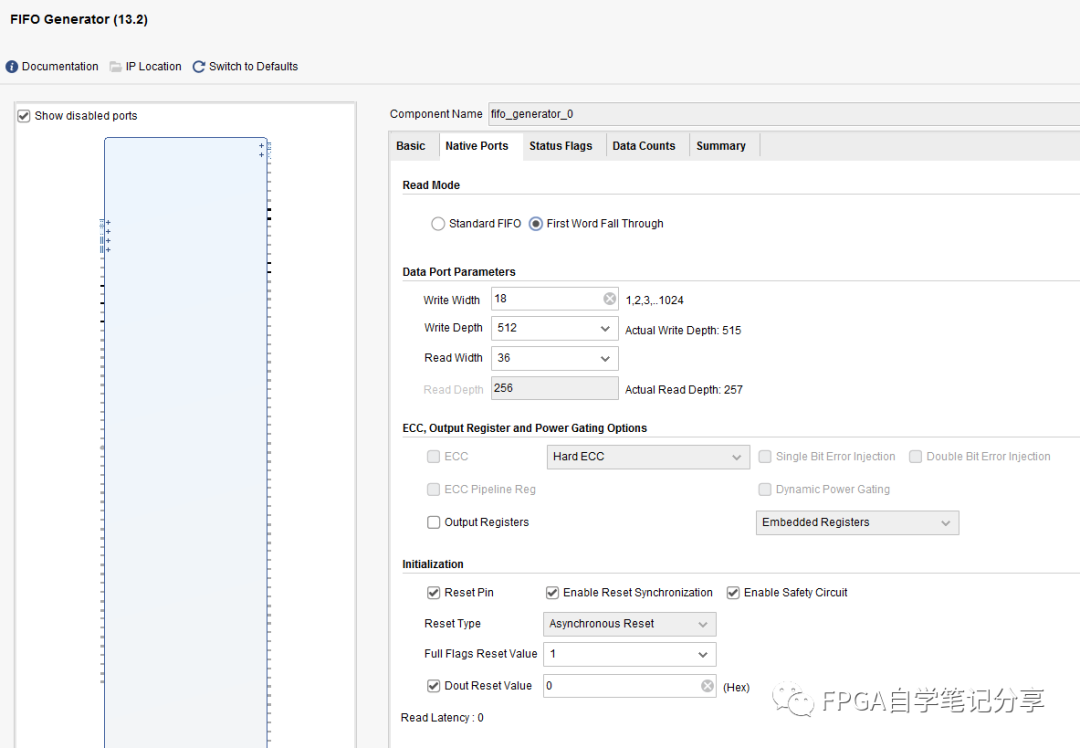

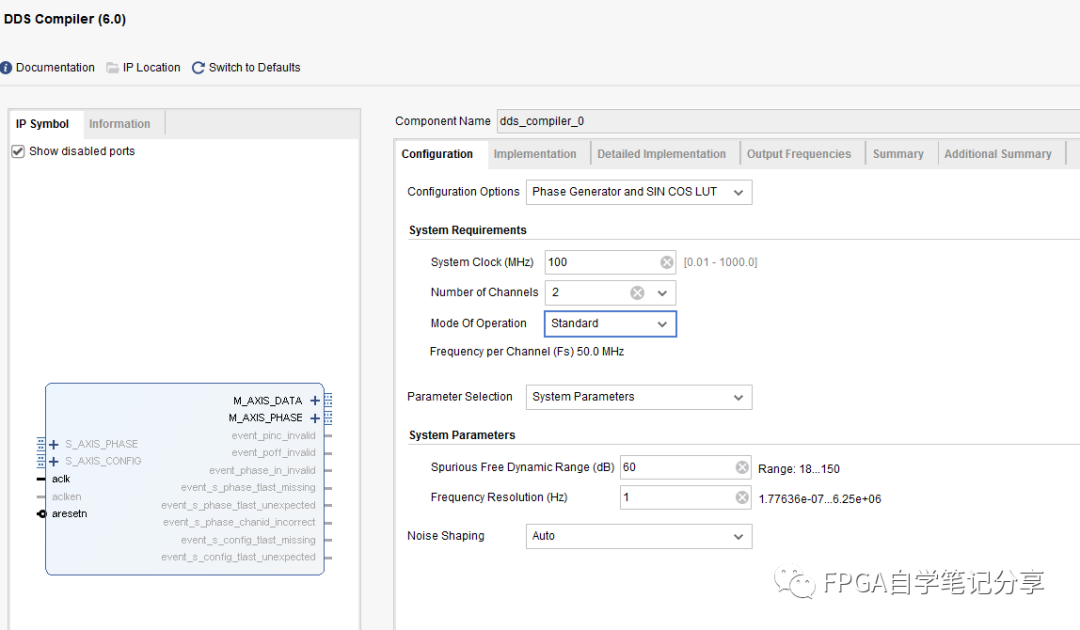

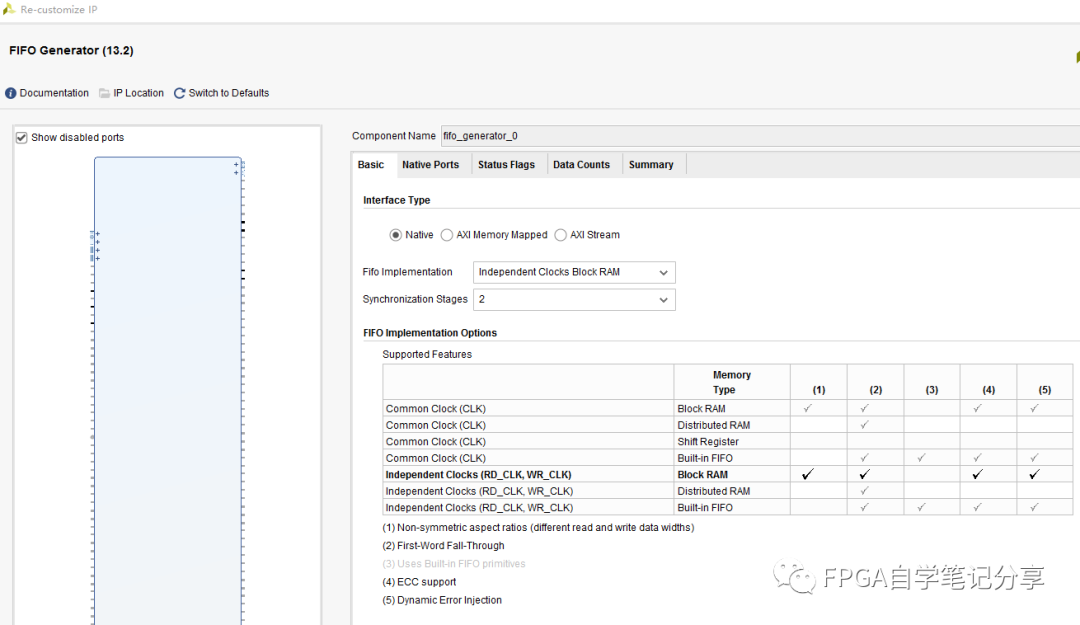

然后,開始例化IP,生成一個FIFO,使用BRAM搭建,兩個獨立時鐘:

寫位寬18bit,讀位寬36bit,讀寫數據位寬比為1:2.

例化的總結為:

例化的端口為:

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

fifo_generator_0 your_instance_name (

.rst(rst), // input wire rst

.wr_clk(wr_clk), // input wire wr_clk

.rd_clk(rd_clk), // input wire rd_clk

.din(din), // input wire [17 : 0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [35 : 0] dout

.full(full), // output wire full

.almost_full(almost_full), // output wire almost_full

.empty(empty), // output wire empty

.almost_empty(almost_empty), // output wire almost_empty

.rd_data_count(rd_data_count), // output wire [7 : 0] rd_data_count

.wr_data_count(wr_data_count), // output wire [8 : 0] wr_data_count

.wr_rst_busy(wr_rst_busy), // output wire wr_rst_busy

.rd_rst_busy(rd_rst_busy) // output wire rd_rst_busy

);

根據這個端口,編寫tb,如下。設置讀寫時鐘頻率比為2:3。寫側:復位釋放后,即拉高寫使能,寫入自加數,直到1000后停止寫入。讀側:只要非空就開始一直讀取數據。

// ============================================================

// File Name: tb_fifo_generator

// VERSION : V1.0

// DATA : 2023/7/23

// Author : FPGA干貨分享

// ============================================================

// 功能:xilinx fifo_generator ip 代碼仿真

// delay :

// ============================================================

`timescale 1ns/100ps

module tb_fifo_generator ;

reg rst ='d1 ;

reg wr_clk ='d1 ;

reg rd_clk ='d1 ;

reg [17 : 0] din ='d1 ;

reg wr_en ='d0 ;

reg rd_en ='d0 ;

wire [35 : 0] dout ;

wire full ;

wire almost_full ;

wire empty ;

wire almost_empty ;

wire [7 : 0] rd_data_count ;

wire [8 : 0] wr_data_count ;

wire wr_rst_busy ;

wire rd_rst_busy ;

initial

begin

rst = 1'b1;

#1000;

rst = 1'b0;

end

always #2 wr_clk = ~wr_clk;

always #3 rd_clk = ~rd_clk;

// ==================wr_clk======================//

always @(posedge wr_clk )

if(din >= 'd1000)

wr_en <= 1'b0;

else if(~wr_rst_busy&&~rst)

wr_en <= 1'b1;

else

wr_en <= 1'b0;

always @(posedge wr_clk)

if(wr_en)

din <= din + 1'b1;

else

din <= din;

// ==================rd_clk======================//

always @(posedge rd_clk)

rd_en <= (!empty)&&(!rd_rst_busy);

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

fifo_generator_0 fifo_generator_0 (

.rst (rst ), // input wire rst

.wr_clk (wr_clk ), // input wire wr_clk

.rd_clk (rd_clk ), // input wire rd_clk

.din (din ), // input wire [17 : 0] din

.wr_en (wr_en ), // input wire wr_en

.rd_en (rd_en ), // input wire rd_en

.dout (dout ), // output wire [35 : 0] dout

.full (full ), // output wire full

.almost_full (almost_full ), // output wire almost_full

.empty (empty ), // output wire empty

.almost_empty (almost_empty ), // output wire almost_empty

.rd_data_count (rd_data_count ), // output wire [7 : 0] rd_data_count

.wr_data_count (wr_data_count ), // output wire [8 : 0] wr_data_count

.wr_rst_busy (wr_rst_busy ), // output wire wr_rst_busy

.rd_rst_busy (rd_rst_busy ) // output wire rd_rst_busy

);

endmodule

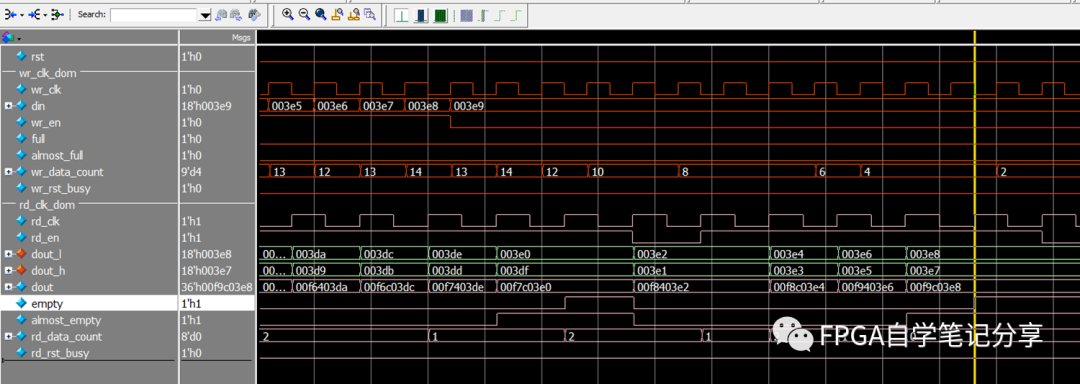

仿真結果如下:

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603420 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121429 -

仿真

+關注

關注

50文章

4082瀏覽量

133613 -

fifo

+關注

關注

3文章

388瀏覽量

43682 -

時鐘域

+關注

關注

0文章

52瀏覽量

9536

發布評論請先 登錄

相關推薦

Xilinx FPGA IP之Block Memory Generator功能概述

Xilinx Block Memory Generator(BMG)是一個先進的內存構造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優化的內存。

XILINX FPGA IP之AXI Traffic Generator

AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統外設上生成特定序列(流量)。它根據IP的編程和選擇的操作模式生成各種類型的AXI事務。是一個比較好用的AXI4協議測

Xilinx FPGA入門連載51:FPGA片內FIFO實例之功能概述

實例內部系統功能框圖如圖所示。我們通過IP核例化一個FIFO,定時寫入數據,然后再讀出所有數據。通過ISE集成的在線邏輯分析儀chipscope,我們可以觀察

發表于 02-26 10:26

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置特權同學,版權所有配套

發表于 02-29 13:35

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置特權同學,版權所有配套

發表于 02-29 13:35

Xilinx FPGA入門連載56:FPGA片內異步FIFO實例之FIFO配置

`Xilinx FPGA入門連載56:FPGA片內異步FIFO實例之FIFO配置特權同學,版權所

發表于 03-09 10:49

【正點原子FPGA連載】第十三章IP核之FIFO實驗-領航者ZYNQ之FPGA開發指南

圖所示。圖 13.4.12 “fifo_generator _0_synth_1”run在其Out-of-Context綜合的過程中,我們就可以進行RTL編碼了。首先打開IP核的例化模

發表于 09-23 17:27

XILINX FPGA IP之FIFO Generator例化仿真

XILINX FPGA IP之FIFO Generator例化仿真

評論