布局前的準備:

1 查看捕捉點設置是否正確

2 Cell名稱不能以數字開頭。否則無法做DRACULA檢查

3 布局前考慮好出PIN的方向和位置

4 布局前分析電路,完成同一功能的MOS管畫在一起

5 對兩層金屬走向預先訂好。一個圖中柵的走向盡量一致,不要有橫有豎

6 對pin分類,vdd,vddx注意不要混淆,不同電位(襯底接不同電壓)的n井分開,混合信號的電路尤其注意這點

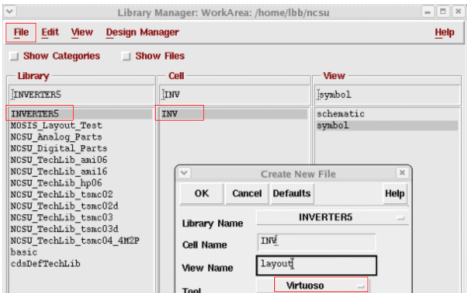

7 在正確的路徑下(一般是進到~/opus)打開icfb

8 更改cell時查看路徑,一定要在正確的library下更改,以防copy過來的cell是在其他的library下,被改錯

9 將不同電位的N井找出來

布局時注意:

10 更改原理圖后一定記得check and save

11 完成每個cell后要歸原點

12 DEVICE的 個數 是否和原理圖一至(有并聯的管子時注意);各DEVICE的尺寸是否和原理圖一至。一般在拿到原理圖之后,會對布局有大概的規劃,先畫DEVICE,(DIVECE之間不必用最小間距,根據經驗考慮連線空間留出空隙)再連線。畫DEVICE后從EXTRACTED中看參數檢驗對錯。對每個device器件的各端從什么方向,什么位置與其他物體連線 必須 先有考慮(與經驗及floorplan的水平有關)

13 如果一個cell調用其它cell,被調用的cell的vssx,vddx,vssb,vddb如果沒有和外層cell連起來,要打上PIN,否則通不過diva檢查。盡量在布局低層cell時就連起來

14 盡量用最上層金屬接出PIN

15 接出去的線拉到cell邊緣,布局時記得留出走線空間

16 金屬連線不宜過長

17 電容一般最后畫,在空檔處拼湊

18 小尺寸的mos管孔可以少打一點

19 LABEL標識元件時不要用y0層,mapfile不認

20 管子的溝道上盡量不要走線;M2的影響比M1小

21 電容上下級板的電壓注意要均勻分布;電容的長寬不宜相差過大。可以多個電阻并聯

22 多晶硅柵不能兩端都打孔連接金屬

23 柵上的孔最好打在柵的中間位置

24 U形的mos管用整片方形的柵覆蓋diff層,不要用layer generation的方法生成U形柵

25 一般打孔最少打兩個

26 Contact面積允許的情況下,能打越多越好,尤其是input/output部分,因為電流較大。但如果contact阻值遠大于diffusion則不適用。傳導線越寬越好,因為可以減少電阻值,但也增加了電容值

27 薄氧化層是否有對應的植入層

28 金屬連接孔可以嵌在diffusion的孔中間

29 兩段金屬連接處重疊的地方注意金屬線最小寬度

30 連線接頭處一定要重疊,畫的時候將該區域放大可避免此錯誤

31 擺放各個小CELL時注意不要擠得太近,沒有留出走線空間。最后線只能從DEVICE上跨過去

32 Text2,y0層只是用來做檢查或標志用,不用于光刻制造

33 芯片內部的電源線/地線和ESD上的電源線/地線分開接;數模信號的電源線/地線分開

34 Pad的pass窗口的尺寸畫成整數90um

35 連接Esd電路的線不能斷,如果改變走向不要換金屬層

36 Esd電路中無VDDX,VSSX,是VDDB,VSSB

37 PAD和ESD最好使用M1連接,寬度不小于20um;使用M2連接時,pad上不用打VIA孔,在ESD電路上打

38 PAD與芯片內部cell的連線要從ESD電路上接過去

39 Esd電路的SOURCE放兩邊,DRAIN放中間

40 ESD的D端的孔到poly的間距為4,S端到poly的間距為^+0.2.防止大電流從D端進來時影響poly

41 ESD的pmos管與其他ESD或POWER的nmos管至少相距70um以上

42 大尺寸的pmos/nmos與其他nmos/pmos(非powermos和ESD)的間距不夠70um時,但最好不要小于50um,中間加NWELL,打上NTAP

43 NWELL和PTAP的隔離效果有什么不同?NWELL較深,效果較好

44 只有esd電路中的管子才可以用2*2um的孔。怎么判斷ESD電路?上拉P管的D/G均接VDD,S接PAD;下拉N管的G/S接VSS,D接PAD.P/N管起二極管的作用

45 擺放ESD時nmos擺在最外緣,pmos在內

46 關于匹配電路,放大電路不需要和下面的電流源匹配。什么是匹配?使需要匹配的管子所處的光刻環境一樣。匹配分為橫向,縱向,和中心匹配。1221為縱向匹配,12為中心匹配(把上方1轉到下方1時,上方2也達到下方2位置)21中心匹配最佳

47 尺寸非常小的匹配管子對匹配畫法要求不嚴格.4個以上的匹配管子,局部和整體都匹配的匹配方式最佳

48 在匹配電路的mos管左右畫上dummy,用poly,poly的尺寸與管子尺寸一樣,dummy與相鄰的第一個poly gate的間距等于poly gate之間的間距

49 電阻的匹配,例如1,2兩電阻需要匹配,仍是1221等方法。電阻dummy兩頭接地vssx

50 Via不要打在電阻體,電容(poly)邊緣上面

51 05工藝中resistor層只是做檢查用

52 電阻連線處孔越多,各個VIA孔的電阻是并聯關系,孔形成的電阻變小

53 電阻的dummy是保證處于邊緣的電阻與其他電阻蝕刻環境一樣

54 電容的匹配,值,接線,位置的匹配

55 電阻連接fuse的pad的連線要稍寬,因為通過的電流較大.fuse的容絲用最上層金屬

56 關于powermos

① powermos一般接pin,要用足夠寬的金屬線接

② 幾種縮小面積的畫法

③ 柵的間距?無要求。柵的長度不能超過100um

57 Power mos要考慮瞬時大電流通過的情況,保證電流到達各處的路徑的電阻相差不大。(適應所有存在大電流通過的情況)

58 金屬層dummy要和金屬走向一致,即如果M2橫走,M2的dummy也是橫走向

59 低層cell的pin,label等要整齊,and不要刪掉以備后用

60 匹配電路的柵如果橫走,之間連接用的金屬線會是豎走,用金屬一層,和規定的金屬走向一致

61 不同寬度金屬連接的影響?整個layout面積較大時影響可忽略

62 輸出端節電容要小。多個管子并聯,有一端是輸出時注意做到這點

63 做DRACULA檢查時,如果先運行drc,drc檢查沒有完畢時做了lvs檢查,那么drc檢查的每一步會比lvs檢查的每一步快;反之,lvs會比 drc快

64 最終DRACULA通過之后在layout圖中空隙處加上ptap,先用thin-oxid將空隙處填滿,再打上孔,金屬寬度不要超過10,即一行最多8 個孔(06工藝)

65 為防止信號串擾,在兩電路間加上PTAP,此PTAP單獨連接VSS PAD

66 金屬上走過的電壓很大時,為避免尖角放電,拐角處用斜角,不能走90度度的直角

67 如果w=20,可畫成兩個w=10mos管并聯

68 并聯的管子共用端為S端,或D端;串聯的管子共用端為s/d端

出錯檢查:

69 DEVICE的各端是否都有連線;連線是否正確

70 完成布局檢查時要查看每個接線的地方是否都有連線,特別注意VSSX,VDDX

71 查線時用SHOTS將線高亮顯示,便于找出可以合并或是縮短距離的金屬線

72 多個電阻(大于兩根)打上DUMMY。保證每根電阻在光刻時所處的環境一樣,最外面的電阻的NPIM層要超出EPOLY2 0.55 um,即兩根電阻間距的一半

73 無關的MOS管的THIN要斷開,不要連在一起

74 并聯的管子注意漏源合并,不要連錯線。一個管子的源端也是另一個管子的源端

75 做DRAC檢查時最上層的pin的名稱用text2標識。Text2的名稱要和該pin的名稱一樣

76 大CELL不要做DIVA檢查,用DRACULE

77 Text2層要打在最頂層cell里。如果打在pad上,于最頂層調用此PAD,Dracula無法認出此pin

78 消除電阻dummy的lvs報錯,把nimp和RPdummy層移出最邊緣的電阻,不要覆蓋dummy

79 06工藝中M1最小寬度0.8,如果用0.8的M1拐線,雖然diva的drc不報錯,但DRACULE的drc會在拐角處報錯。要在拐角處加寬金屬線

80 最后DRACULA的lvs通過,但是drc沒有過,每次改正drc錯誤前可把layout圖存成layout1,再改正。以免改錯影響lvs不通過,舊 版圖也被保存下來了

81 Cell中間的連線盡量在低層cell中連完,不要放在高層cell中連,特別不要在最高層cell中連,因為最高層cell的布局經常會改動,走線容易 因為cell的移動變得混亂

82 DRACULA的drc無法檢查出pad必須滿足pad到與pad無關的物體間距為10這一規則

83 做DRACULA檢查時開兩個窗口,一個用于lvs,一個用于drc.可同時進行,節省時間

容易犯的錯誤:

84 電阻忘記加dummy

85 使用NS功能后沒有復原(選取AS),之后又進行整圖移動操作,結果被NS的元件沒有移動,圖形被破壞

86 使用strech功能時錯選。每次操作時注意看圖左下角提示

87 Op電路中輸入放大端的管子的襯底不接vddb/vddx

88 是否按下capslock鍵后沒有還原就操作

節省面積的途徑:

89 電源線下面可以畫有器件節省面積

90 電阻上面可以走線,畫電阻的區域可以充分利用

91 電阻的長度畫越長越省面積

92 走線時金屬線寬走最小可以節省面積,并不需要走孔的寬度

93 做新版本的layout圖時,舊圖保存,不要改動或刪除。減小面積時如果低層CELL的線有與外層CELL相連,可以從更改連線入手,減小走線面積

94 版圖中面積被device,device的間隔和走線空間分割,減小面積一般從走線空間入手,更改FLOORPLAN。

-

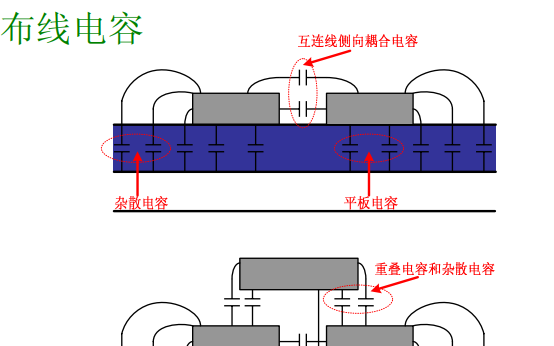

電容

+關注

關注

100文章

6045瀏覽量

150342 -

IC

+關注

關注

36文章

5950瀏覽量

175613 -

MOS管

+關注

關注

108文章

2418瀏覽量

66837 -

PIN

+關注

關注

1文章

304瀏覽量

24308

原文標題:IC版圖設計布局經驗90條!

文章出處:【微信號:芯司機,微信公眾號:芯司機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

江蘇招IC版圖設計項目經理

硬件、IC版圖工程師招聘

版圖設計工程師-上海

版圖設計工程師-上海

版圖設計工程師-上海

版圖設計-上海

【招聘】職位包括數字IC設計/驗證/后端物理設計、模擬IC設計/版圖工程師

西安急招:模擬IC設計 數字IC設計 版圖設計

IC工藝和版圖設計的電容版圖設計的詳細中文資料概述

IC版圖設計和PCB版圖設計有什么區別詳細資料說明

IC版圖設計布局經驗90條!

IC版圖設計布局經驗90條!

評論