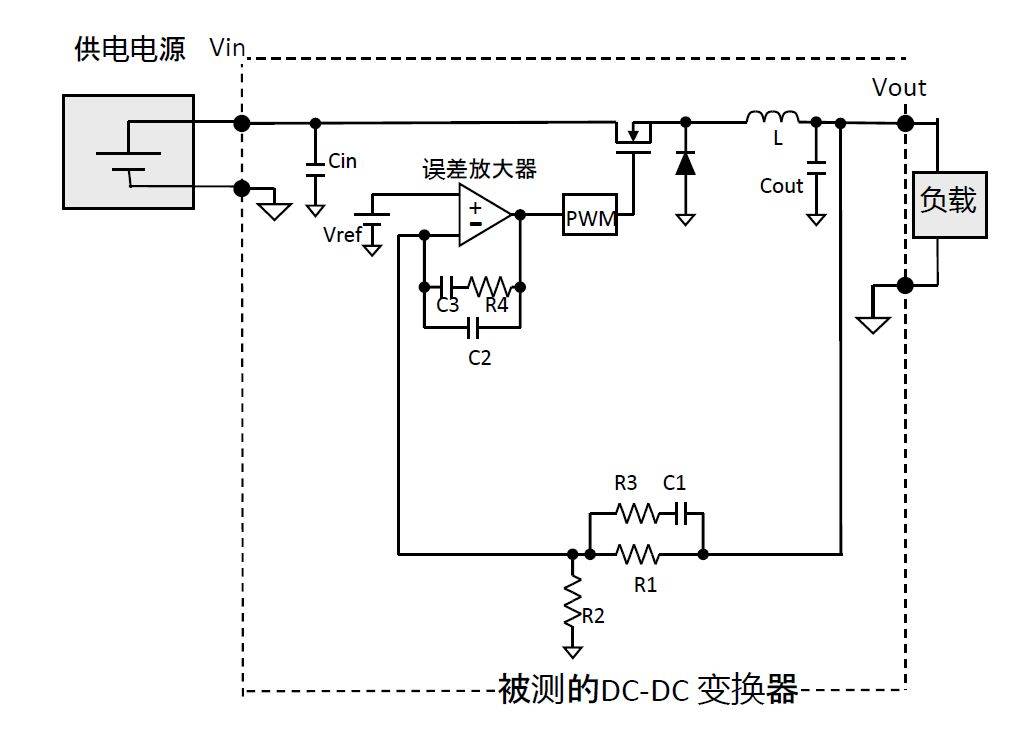

DC-DC 變換器原理示意圖:

DC-DC可以降壓也可以升壓。

脈沖經過濾波電路變換回DC輸出。

通過在輸出端電壓采樣,進行負反饋調整脈沖占空比,可以控制整個能量輸出,達到穩壓目的。

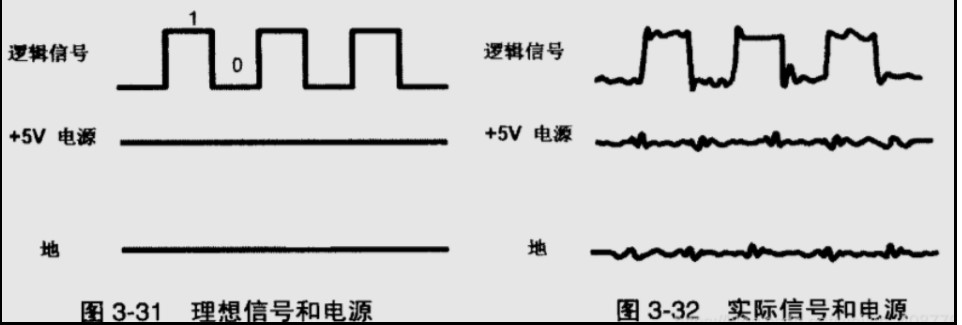

造成輸出DC不穩的原因主要是負載電流變化,當然還有其他因素比如輸入不穩,環境變化等。

改善電源完整性方法

1、優化反饋環路設計

瞬變響應速度

環路穩定性

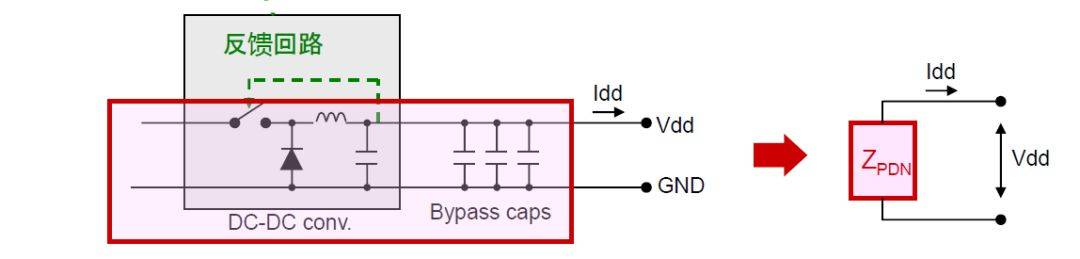

2、將|ZPDN| 壓到一個小數值

可以使得Vdd波動最小化,因為Delta-Vdd= ZPDNx Delta-Idd(較小的ZPDN ?較小的Delta-Vdd)

DC-DC電源模塊反饋環路的特征測試

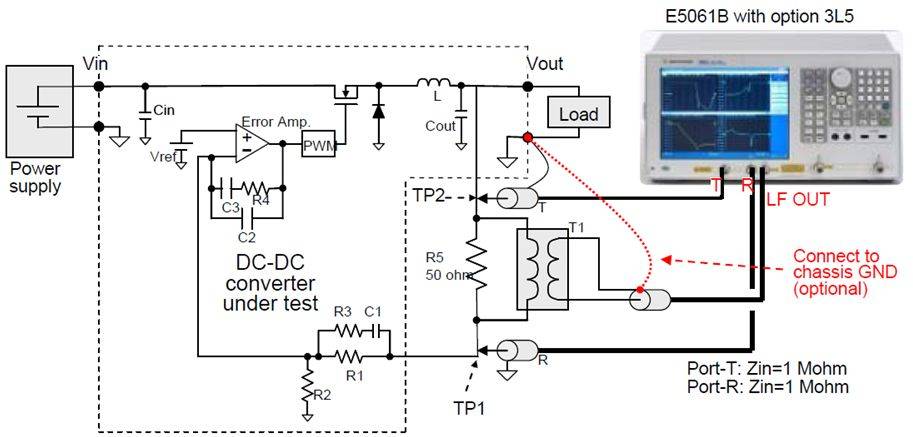

Keysight E5061B 低頻-射頻網絡分析儀的選件3L5,可以提供±40Vdc 的直流偏置電壓疊加到從端口 1 或 LF OUT端口上輸出的交流信號上。此外,如果在儀表的 S 參數測試端口上對被測器件進行測量時,它還可以從 LF OUT端口輸出直流電壓。可以在5Hz~3GHz 的率范圍內提供常用的網絡測量和分析功能。功能全面的低頻網絡測量能力(包括內置的 1MΩ 輸入) 都被完美地集成到這個高性能的射頻網絡分析儀之中。

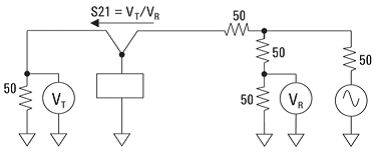

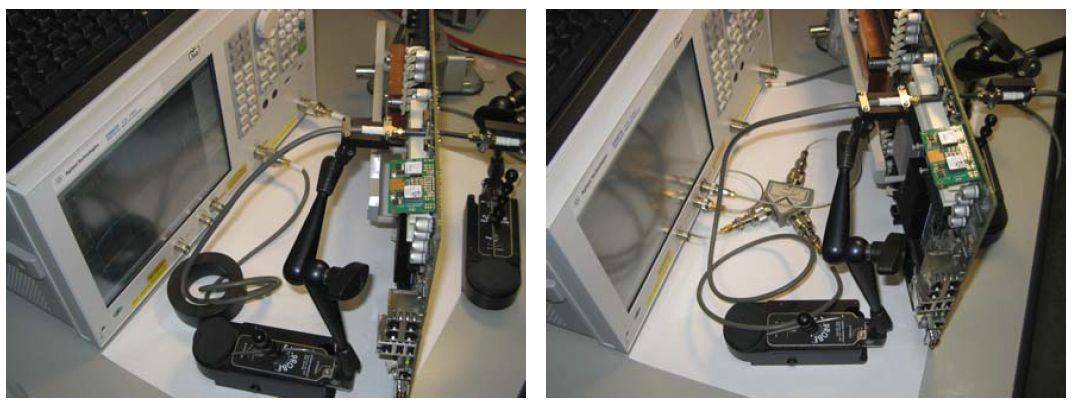

使用 E5061B-3L5可以測試DC-DC電源的環路增益、相位裕量、增益裕量等反饋環路特性。比如環路增益測試測試配置如下圖:在E5061B-3L5的高輸入阻抗測量接收機的R和T端口上測量激勵施加電路兩側的交流電壓,隨后把這兩個測量結果進行比值計算得到環路增益最終的測量結果。

把激勵信號加在滿足Zin >> Zout 的點上,并讓電阻R滿足Zin >> R >> Zout的條件,可以通過T/R 比值的測量結果得到循環傳遞函數-GH 的特性,這里選擇R=R5=50歐姆;

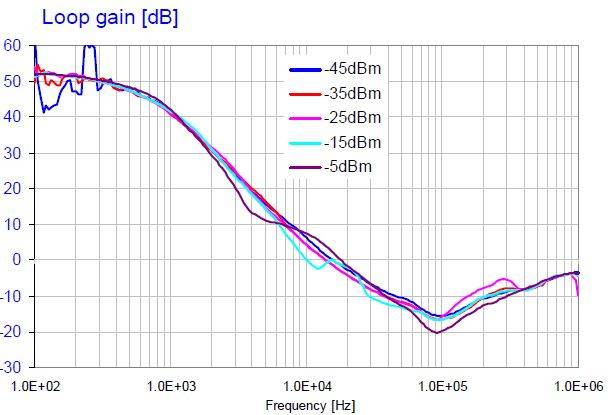

如下圖所示,當測試得到環路增益|GH|后,通過游標找到|GH|=1的交叉頻率。同樣的,在相位測量曲線即可得到相位裕量,進而可以測量增益裕量。

DC-DC電源模塊輸出阻抗測試

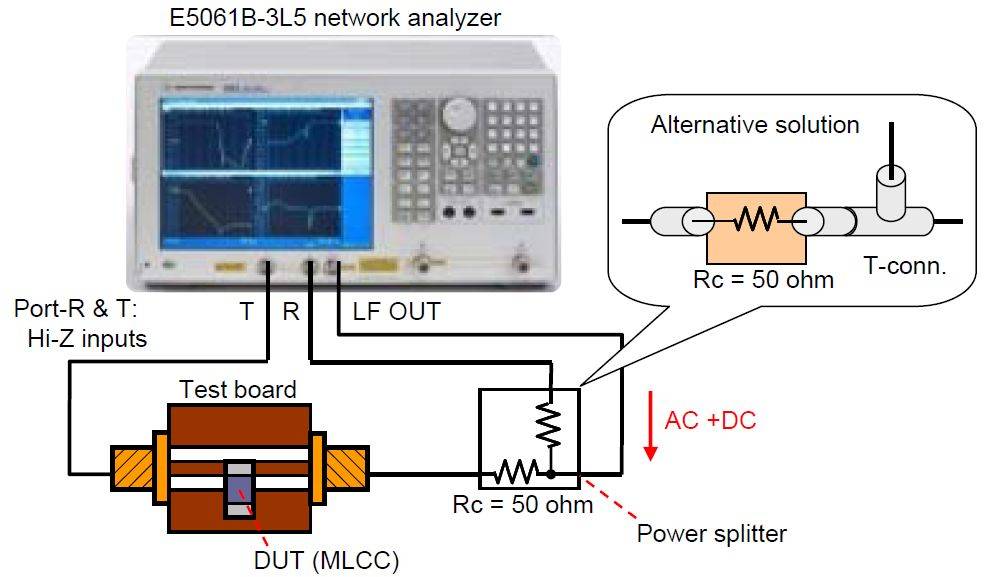

電源的輸出阻抗會影響到在電流變化時輸出電壓的變化,其輸出阻抗越小,瞬態電流變化對輸出電壓的影響越小。DC-DC電源輸出阻抗的測試有電流-電壓檢測法和并聯-直通法測試。電流-電壓方法使儀表激勵信號源和被測件直流輸出電壓之間很好的隔離,接收機使用高阻輸入端口,適用于測試輸出電壓較大的DC-DC變換器的輸出阻抗。但是,這種方法不適用測試毫歐級的輸出阻抗。

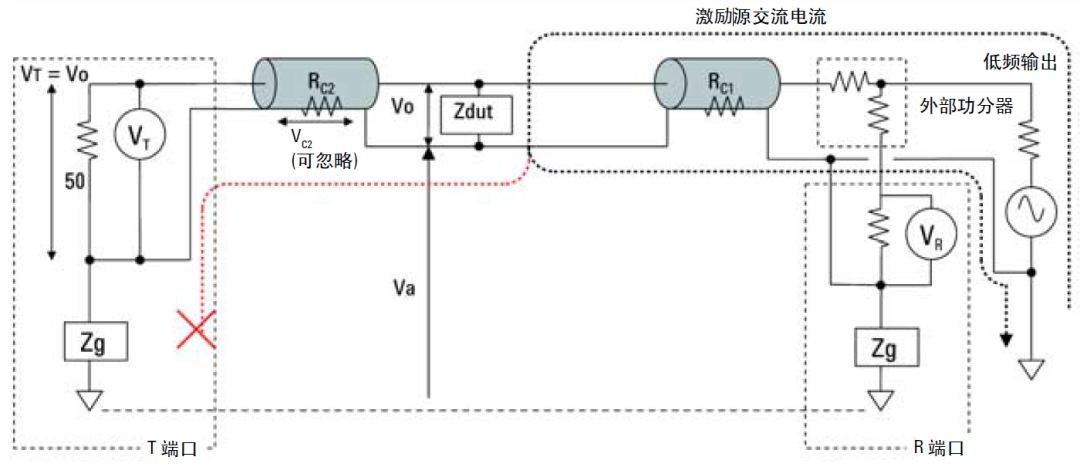

并聯-直通方法能夠對毫歐級的微小阻抗進行精確測量,通過測量T,R端口傳輸系數S21推導出輸出阻抗。Zdut 和S21 之間的關系為: Zdut = 25 x S21/ (1-S21),其原理如下。

由于激勵信號源和接收機之間測試電纜的接地環路的電壓下降會引入誤差,傳統的低頻網絡分析儀對于非常小的毫歐級阻抗的測試非常困難。雖然可以在激勵源、接收機一側加入磁環抑制電流,或者使用變壓器隔離接地環路,然而合適的磁環非常難以選擇,變壓器剩余響應的影響也無法完全消除。

Keysight網絡分析儀E5061B-3L5 的增益-相位測試端口使用在低頻大約30?半浮置的接地方法,可以阻止屏蔽電流,不需要外部磁環或變壓器就可以輕松測試毫歐級的輸出阻抗。下圖是使用E5061B-3L5 增益-相位端口精確測試DC-DC變換器輸出阻抗的原理。

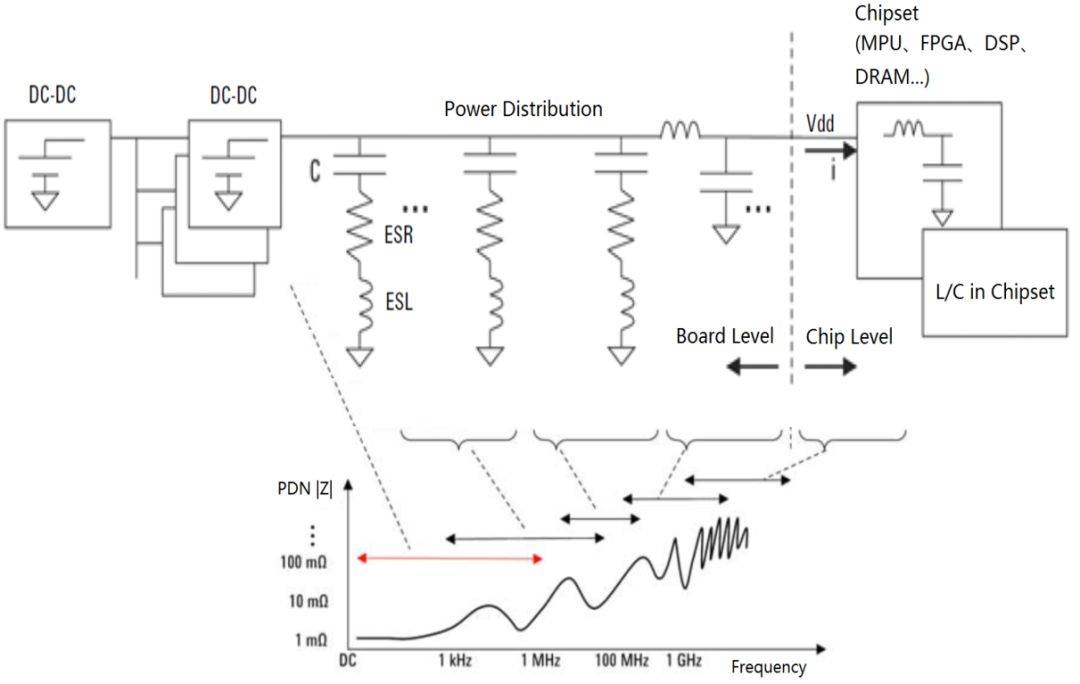

電源分配網絡PDN阻抗測試

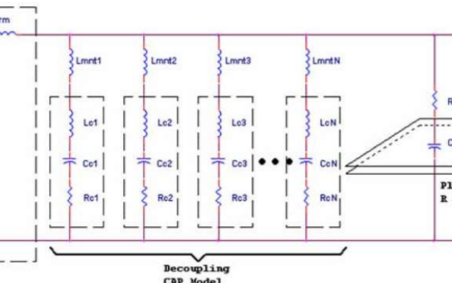

數字電路系統中,電路供電通常使用DC-DC Buck-Boost單元或LDO模塊。由DC-DC單元、電路板的電源布線層、無源器件(整形LC、旁路電容、去耦電容)組成了電源分布網絡(Power Distribution Network)。

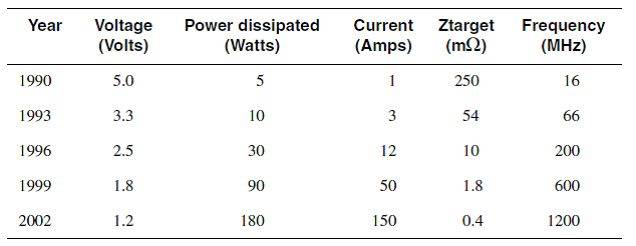

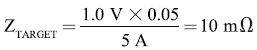

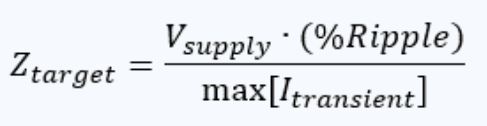

為了評估電源系統對紋波噪聲的要求,以及方便在頻域和時域評估電源系統,引入了目標阻抗Ztarget。目標阻抗同樣遵循歐姆定律,假設電源電壓為5V,紋波范圍要求為5%,負載電流微1A,電路工作時電流變化在50%以內,那么對目標阻抗的要求為 Ztarget ≤ (5*0.05)/(1*50%)。隨著數字系統頻率的增加以及集成規模增大,為了減小功耗電源電壓越來低,電源紋波要求越小,對PDN阻抗的精確測試變的異常重要。下圖顯示了數字電路電源功耗、工作頻率、PDN目標阻抗的變化趨勢。

如前面提到的,假設Zpdn 是從負載器件一端看到的Vdd 和接地層之間的阻抗,Delta-I 就是由負載器件的工作所引起的電流變化,在電源層面上會產生電壓降Delta-V = Delta-i x Zpdn。更嚴格地講,電壓降應該是: Delta-V =IFFT (FFT(delta-I) x Zpdn)。對于MPU 之類的高性能LSI的應用情況,Delta-I可能是幾安培或幾十安培,對于包含大量大規模集成芯片的高速數字電路中,低電壓大電流工作時,電源分布網絡(PDN)極小的輸出阻抗會引起電壓的較大波動,超出電壓幅度的要求范圍,導致信號完整性和電磁干擾問題。比如供電電壓為1V,允許的紋波噪聲或者電壓偏移為5%,電流變化范圍為5A,則PDN的阻抗要求為:

因此,在從DC到GHz的廣闊頻率范圍內,必須將電源層的阻抗Zpdn 抑制在一個極小的值上。下圖顯示了PDN網絡阻抗的影響因素及的頻率和阻抗范圍。

在裝配好的電路板上,安裝有DC-DC變換器,濾波LC電路,旁路電容、磁珠等無源器件,以及電源層的網絡布線共同構成PDN阻抗。同樣,可以使用增益相位端口或者S端口測試系統級的PDN阻抗。使用S端口測試時,頻率范圍可以在5Hz-3GHz,需要使用磁環抑制線纜接地環路引入的AC電流。也可以在系統上電或者斷電條件小測試系統電路板的PDN阻抗。下圖是用E5061B進行PDN網絡阻抗測試的例子。

無源器件如電感,電容也是PDN的重要部分,電容器作為旁路電容,選擇不同容值,可以在相應頻率范圍抑制PDN的阻抗,減小電源噪聲。

并聯-直通測量在小阻抗范圍內具有良好的靈敏度,通常用于測量旁路電容。對于鐵氧體磁珠等去耦器件,阻抗較高,使用反射測量方法進行測試。由于測試電纜接地環路的影響,會在低頻段導致阻抗測量結果的較大誤差。如前所述,E5061B-3L5 的增益相位測試端口的半浮置接地結構可以消除這一影響,頻率范圍5Hz-30MHz。還可以使用S參數端口測量更高頻率范圍的阻抗特性,5Hz-3GHz,需要使用磁環抑制流過接地屏蔽層的交流電流。下圖顯示了E5061B-3L5 用增益相位端口進行電容阻抗測試方法。

審核編輯:湯梓紅

-

高速電路

+關注

關注

8文章

158瀏覽量

24253 -

阻抗分析儀

+關注

關注

2文章

110瀏覽量

10928 -

電源完整性

+關注

關注

9文章

210瀏覽量

20745 -

輸出阻抗

+關注

關注

1文章

103瀏覽量

12338

發布評論請先 登錄

相關推薦

信號完整性與電源完整性的仿真分析與設計

什么是電源和信號完整性?

電源和信號完整性的分析與測試

電源和信號完整性的分析與測試

高速電路電源完整性測試之電源輸出阻抗和環路測試

高速電路電源完整性測試之電源輸出阻抗和環路測試

評論