1、常量

整數(shù):整數(shù)可以用二進(jìn)制數(shù)b或B,八進(jìn)制o或O,十進(jìn)制d或D,十六進(jìn)制h或H表示,例如:8‘b10101010表示8位位寬的二進(jìn)制數(shù);

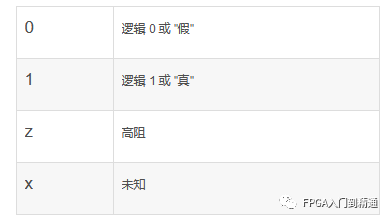

x和z:x代表不定值,z代表高阻值,例如,5’b0x111,第四位不定值,3‘bz00表示最高位為高阻值;

下劃線:在位數(shù)過長時可以用來分割位數(shù),提高程序可讀性,如8’b0101_0101;

參數(shù) parameter:可以用標(biāo)識符定義常量,運用時只使用標(biāo)識符即可,提高可讀性及維護性,如可以定義parameter width = 8 ;定義寄存器 reg [width - 1 : 0] a;即定義了八位寬度的寄存器;

參數(shù)的傳遞:在一個模塊中如果有定義參數(shù),在其它模塊調(diào)用此模塊時可以傳遞參數(shù),并可以修改參數(shù);

注意:parameter可以用于模塊間的參數(shù)傳遞,而localparam僅用于本模塊內(nèi)使用,不能用于參數(shù)傳遞。localparam多用于狀態(tài)機狀態(tài)的定義;

2、變量

變量是指在程序運行過程中可以改變其中的值,常見的變量類型主要有wire型和reg型

wire型

wire類型變量,也叫網(wǎng)絡(luò)類型變量,用于結(jié)構(gòu)實體之間的物理連接,如門與門之間,不能儲存值,用連續(xù)賦值語句assign賦值,定義為wire[n-1 : 0] x ;其中n代表位寬,如定義wire x; assign x = y ;是將y的結(jié)點連接到連線x上;

reg 型

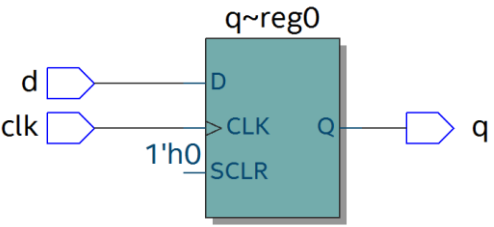

reg類型變量,也稱為寄存器變量,可用來儲存值,必須在always語句內(nèi)使用。通常可以定義為:reg [n-1 : 0] a ;表示n位位寬的寄存器, 如reg[7 : 0] a ; 表示定義8位位寬的寄存器a。

module cs (d, clk, q) ;

input d ;

input clk ;

output reg q ;

always @ (posedge clk)

begin

q <= d ;

end

endmodule

?

寄存器的結(jié)構(gòu)圖

?

以上便是關(guān)于verilog的常見數(shù)據(jù)類型的相關(guān)知識,希望對你有所幫助。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21759瀏覽量

604297 -

寄存器

+關(guān)注

關(guān)注

31文章

5357瀏覽量

120668 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110158 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1608瀏覽量

80689

發(fā)布評論請先 登錄

相關(guān)推薦

[4.2.1]--4.2verilog數(shù)據(jù)類型

Verilog 變量聲明與數(shù)據(jù)類型二

Verilog 變量聲明與數(shù)據(jù)類型一

vhdl數(shù)據(jù)類型

verilog的數(shù)據(jù)類型

Struct結(jié)構(gòu)數(shù)據(jù)類型

結(jié)構(gòu)數(shù)據(jù)類型(Struct)及應(yīng)用案例

什么是數(shù)據(jù)類型轉(zhuǎn)換

定義數(shù)據(jù)類型

Verilog中的基本數(shù)據(jù)類型

Verilog最常用的2種數(shù)據(jù)類型

verilog的數(shù)據(jù)類型

verilog的數(shù)據(jù)類型

評論