異常和中斷會暫停程序以響應硬件或軟件中的意外事件。中斷是異步事件,異常是同步事件,但是中斷和異常之間的區別也取決于具體情況。例如,x86 機器和 ARM 處理器之間以及 CISC 和 RISC 處理器之間的定義不同。

本常見問題解答首先概述了中斷的一般定義和各種類型的異常,然后比較了幾種計算環境中定義的差異以及如何優先處理中斷。

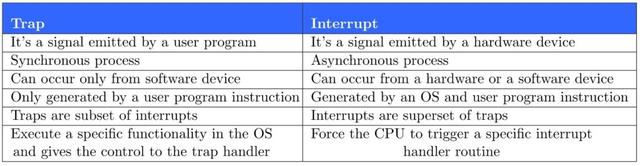

異常有時被稱為“陷阱”,可以由執行函數時進程中的異常或錯誤觸發。除零、斷點或無效內存訪問等情況與程序的執行同步發生。它們可能會導致異常,從而改變處理器的操作。一旦異常原因得到處理,處理器就會返回到之前的活動。另一方面,中斷是異步發出的并且可以隨時到達。例如,用戶擊鍵的產生會啟動中斷。

異常是軟件驅動中斷的子集,而中斷可以源自軟件或硬件源。當異常發生時,異常處理程序執行異常類型定義的特定功能。同樣,中斷會觸發處理器的特定例程,例如在擊鍵到達時及時處理它們。

在基本層面上,異常(陷阱)被定義為源自軟件的同步事件,而中斷是由外部硬件引起的異步事件。

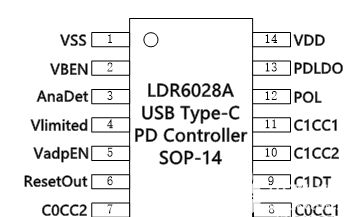

在 MCU 中,中斷可以指示硬件設備中需要及時關注的電子或物理變化。中斷用于實時計算以支持多任務處理。大多數 MCU 都是中斷驅動設備。MCU 中的特定總線控制線通過 INT 引腳處理中斷的接收。

INT引腳連接多個外部設備,例如鍵盤;網絡互連卡、USB 接口等。中斷控制器通知處理器哪個設備發出中斷,使處理器能夠執行必要的中斷處理程序。在某些情況下,中斷會導致 CPU 開始執行中斷向量表中具有特定指令的代碼。中斷可能源自硬件、軟件或其他處理器 (圖 1) 。另一種對中斷進行分類的方法是按來源分類:

- CPU內部觸發異常

- 由外部硬件設備觸發的中斷

- 由軟件源觸發的中斷。

- 處理器間中斷由多任務或實時計算環境中的不同CPU 觸發。

中斷可能源自外部硬件、處理器或另一個處理器(在多核環境中)或軟件。

有時根據情況的嚴重程度將異常分為兩類:

中止會停止代碼執行,直到條件得到處理為止,并且中止是由硬件故障、被零除錯誤等重大問題引起的。

陷阱需要被處理,但不會阻止代碼執行,并且用于虛擬內存管理、程序調試和類似功能。

處理中斷

異常或中斷處理通常分為三個階段:

- 當處理器識別出異常的來源時,就會發生“識別”。

- 當處理程序控制指令執行、保存上下文并且處理程序例程開始在管理員模式(有時稱為特權狀態)下運行時,將“發生”異常或中斷。

- 異常或中斷“處理”發生在管理程序模式下,并持續到處理器恢復執行程序代碼為止。

定義不同

中斷可以分為異常、陷阱、故障和中止,但事情并沒有那么簡單。這取決于上下文和所考慮的特定平臺。在各種環境中,“陷阱”可以指任何中斷、軟件中斷或同步軟件中斷。此外,該術語僅適用于由名稱中帶有“trap”的指令產生的中斷或啟動監視程序或調試器的斷點。中斷在 x86 和 ARM 環境中具有不同的分類。

在x86環境中,存在硬件中斷和軟件異常,分為三種不同類型:故障、陷阱和中止。x86 環境中的中斷由任何 I/O 設備異步觸發。當程序被“中斷”時,它可以重新啟動而不會丟失功能。“故障”也會導致可重新啟動的情況,但它是與軟件執行相關的同步事件。“陷阱”就像一個錯誤,但具有不同的返回地址。在陷阱中,返回地址指向陷阱指令之后要執行的指令,而在故障中,返回地址指向出錯的指令。陷阱通常用于系統調用。“中止”是由嚴重錯誤引起的,并且通常不允許程序重新啟動。

在 ARM 架構中,術語“異常”可用于指代所有類型的中斷。在這種情況下,異常被分類為硬件中斷、復位、異常生成指令和中止。ARM MCU 中的中止包括數據中止(數據訪問失敗)或指令中止(指令讀取失敗),也稱為預取中止。雖然 x86 環境中的“異常”是同步事件,但它們在 ARM 環境中可以是同步或異步的。此外,ARM“異常”可以是精確的,也可以是不精確的(如下一節中定義)。

RISC差異

與 CISC 架構相比,RISC MCU 采用不同的方法來處理中斷或異常。對于設計人員來說,這些差異最初可能比 x86 和 ARM 架構之間的差異更具挑戰性。RISC 機器識別四種類型的異常:

- 異步精確和不精確

- 同步精確、非精確

與其他情況一樣,異步異常可以隨時發生,而同步異常則與指令流同步。精確例外和不精確例外概念的引入是一個重要的區別:

- 精確異常具有精確定義的原因,并且通常是可恢復的。

- 不精確的異常是不可恢復的,意味著處理器無法繼續執行程序,通常會導致災難性的故障。

同步精確是指令異常的結果。根據具體原因,保留出錯指令或下一條指令的地址,以供異常處理后使用。異常處理程序確定錯誤指令是否部分或全部完成,并確定應如何處理它。

同步不精確異常用于 RISC-V 處理器,但在 PowerPC 設備中并不完全支持。同步不精確異常處理是針對 PowerPC 架構中的特定浮點異常定義的。同步不精確異常的一般概念將來可能會得到更全面的實現。

異步精確有時稱為“可屏蔽”,可能由外部中斷、遞減器故障、系統管理中斷、熱管理中斷等引起。在異步精確異常期間,異常之前正在處理的指令在異常處理之前完成。當異常被清除時,下一條指令被存儲并執行。由于這些異常是由外部設備引起的,因此在處理任何給定異常之前,可能會同時或快速連續發生多個異常。如果異常處理程序中的存儲空間不足,則可能會錯過某些異常。解決這個潛在問題的一種方法是在異常處理程序和外部設備之間包含某種形式的握手,以確保所有異常都已被接收和確認。

異步不精確,有時稱為“不可屏蔽”,例外情況僅包括系統重置和機器檢查。當系統復位發生時,CPU停止,所有內部存儲器和寄存器復位,然后處理器重新啟動。機器檢查異常是當CPU檢測到處理器本身、內存、I/O設備或系統總線中的硬件錯誤時發生的計算機硬件錯誤。對于 PowerPC 設備,軟件錯誤(例如某些無效的內存訪問)也可能導致機器檢查異常。大多數機器檢查異常都會停止操作系統并需要重新啟動才能恢復操作。

識別 RISC 異常

當指令不按程序順序執行時,異常識別尤其具有挑戰性。例如,PowerPC 按照嚴格的程序順序處理同步異常,即使程序流中后續的指令可能已生成了附加異常。第一個異常的處理就像前面的指令已全部執行而后面的指令尚未執行一樣。

當然,多個異常可以同時發生。在這種情況下,將根據特定優先級處理異常。異步不精確異常具有最高優先級,在此類別中,系統重置異常的優先級高于機器檢查異常。接下來是按程序順序處理的同步精確異常,然后是同步不精確異常。異步精確異常的優先級最低,外部中斷的優先級高于內部中斷(例如遞減器和系統管理中斷)。

當多個異常同時發生時,RISC 器件具有嚴格的異常處理優先級。

概括

在基本層面上,異常被分類為中斷的子集。更具體地說,異常是源自軟件的同步事件,而中斷被定義為由外部硬件引起的異步事件。中斷和異常的定義因 x86、ARM 和 RISC 等計算架構而異。異常和中斷的各種原因在中斷系統操作方面具有不同的嚴重程度。因此,要根據具體情況制定嚴格的優先順序。

-

USB接口

+關注

關注

9文章

701瀏覽量

55651 -

ARM處理器

+關注

關注

6文章

360瀏覽量

41742 -

調試器

+關注

關注

1文章

305瀏覽量

23741 -

中斷控制器

+關注

關注

0文章

59瀏覽量

9456 -

異常中斷

+關注

關注

0文章

9瀏覽量

1224

發布評論請先 登錄

相關推薦

異常、陷阱和中斷有什么區別呢?

異常、陷阱和中斷有什么區別呢?

評論