按鍵是數字系統最基本的輸入接口設備,本文主要介紹機械彈性按鍵的原理和編程方法。

0****1

按鍵原理

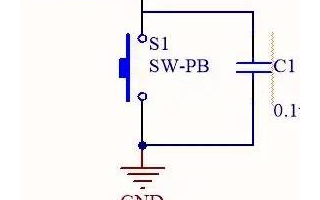

以EGO1開放板按鍵為例,用戶可用的板載按鍵主要包括S6(低有效按鍵),S0~S4(高有效按鍵)。

由原理圖可以看到,按鍵S6在未按下時,FPGA引腳通過電阻連接3.3V高電平;當按鍵按下,與地連通,引腳電平被拉低。S0~S4則相反,按鍵未按下時,引腳為低電平;按鍵按下時,接通3.3V電源,引腳電平由低變高。

因此,我們通過檢測高低電平的變化,就可以檢測按鍵是否被按下。

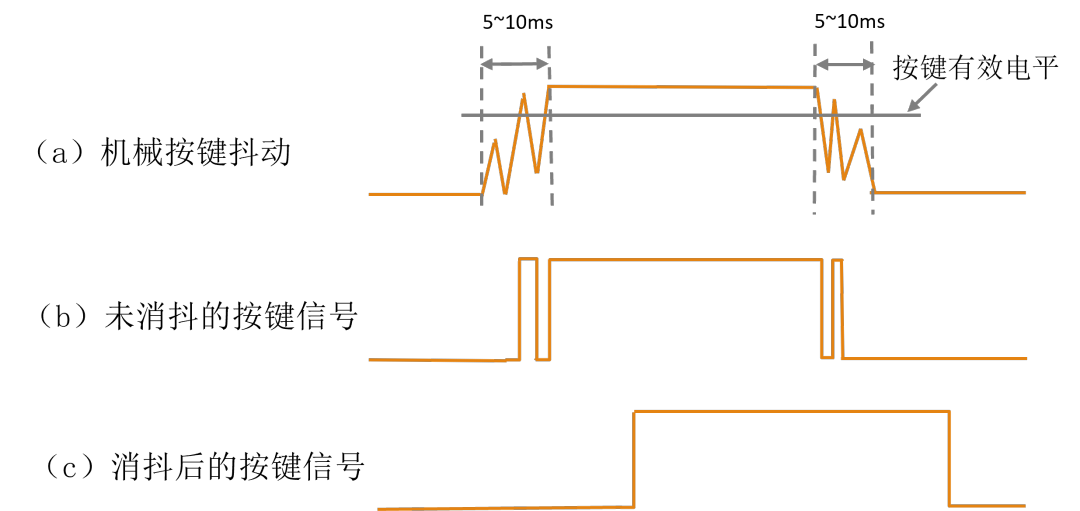

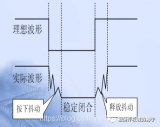

但是實際情況是,我們使用的是機械彈性按鍵,在按鍵按下和彈起過程中會存在抖動,如圖(a)。

一般抖動會在5~10ms左右,按鍵持續時間在幾百ms,而FPGA時鐘是ns級的,檢測頻率很高,如果僅僅通過高低電平的變化去判斷按鍵是否被按下,則在一次按鍵按下時,就會被檢測為多次有效按鍵,如圖(b),從而造成誤觸發。

我們需要對按鍵信號進行消抖處理,得出圖(c)的穩定的按鍵信號。

0****2

按鍵消抖方法

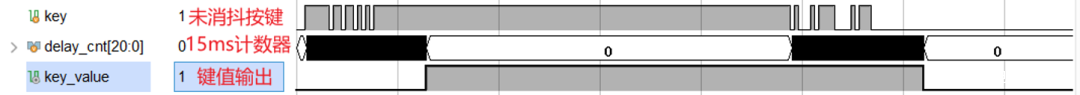

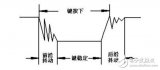

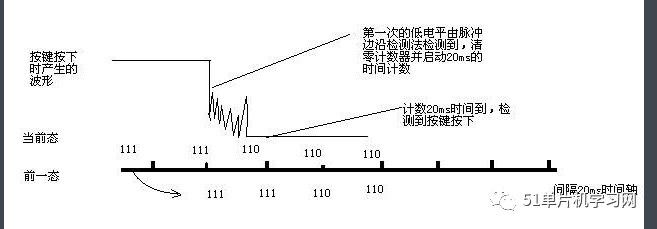

由于抖動大約5-10ms,可以使用一個15ms的計數器。

每當檢測到輸入有變化就復位計數器,然后進行15ms的延時,如果在15ms之內有抖動,計數器就會復位重新計數,直到能夠連續計數15ms,說明按鍵鍵值在15ms內沒有發生改變,按鍵進入穩定狀態,此時,可以輸出穩定的鍵值。

同樣,當按鍵彈起時出現鍵值的改變,就復位計數器,只有當按鍵穩定,計數器能夠連續計數15ms時,才輸出穩定的鍵值。這樣我們就得到一個穩定的沒有抖動的采樣鍵值。

03

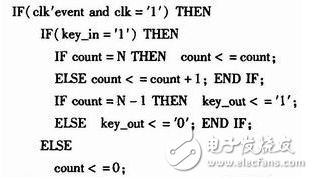

按鍵消抖的Verilog描述

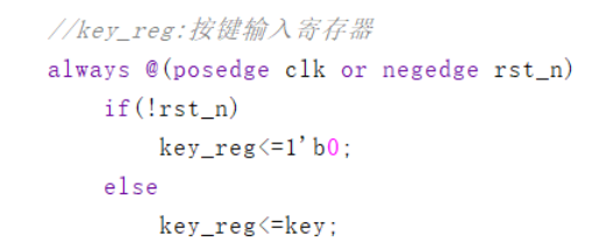

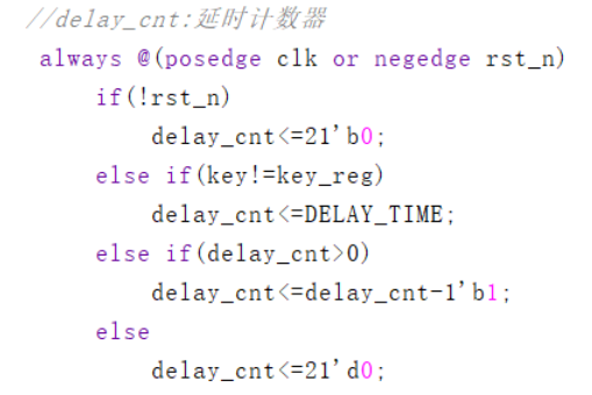

遵循一個always描述一個信號的原則,下面分別對各個信號進行描述。

按鍵寄存器key_reg描述:

延時計數器delay_cnt描述:

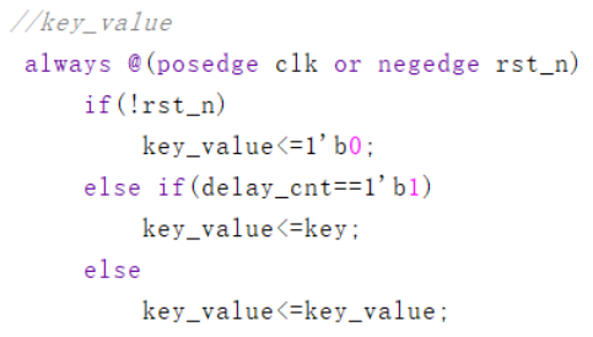

鍵值key_value描述:

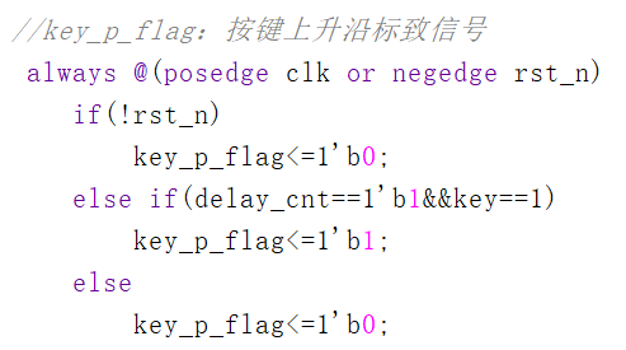

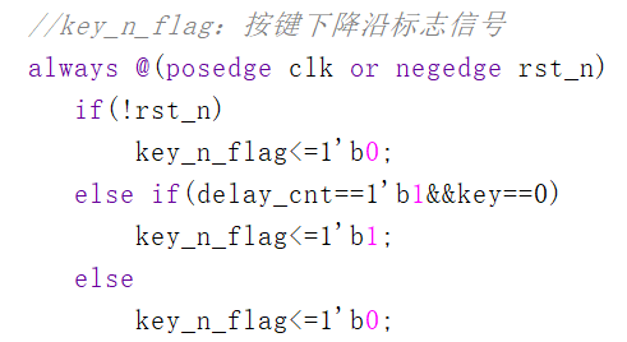

按鍵的標志信號key_p_flag和key_n_flag描述:

按鍵標志信號是一個指示按鍵有效的只持續1個時鐘周期的標志信號,一般作為后級模塊的控制信號。

當計數值為1并且鍵值為一是則為上升沿標志,當計數值為1,且鍵值為0,就輸出下降沿標志信號。

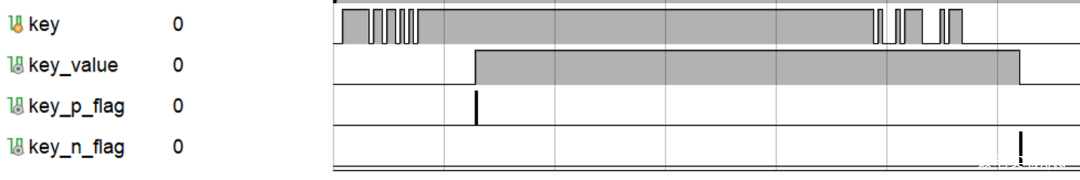

仿真波形如下圖。

-

控制器

+關注

關注

112文章

16361瀏覽量

178030 -

寄存器

+關注

關注

31文章

5343瀏覽量

120348 -

計數器

+關注

關注

32文章

2256瀏覽量

94562 -

FPGA芯片

+關注

關注

3文章

246瀏覽量

39797 -

按鍵電路

+關注

關注

1文章

35瀏覽量

21774

發布評論請先 登錄

相關推薦

機械彈性按鍵的原理和編程方法介紹

機械彈性按鍵的原理和編程方法介紹

評論