最近碰到一個客戶,他們在 i.MX RT500 上使能了 FlexSPI->MCR0[RXCLKSRC] = 2(即 loopbackFromSckPad),這個選項字面上的意思是設置讀選通采樣時鐘源為 SCK 引腳,這個選項在恩智浦官方的代碼包里未曾使能過。

客戶在使用過程中遇到高頻時 SCK 引腳被降壓的問題(從正常的 1.8V 降至 1.2V),那么這個 loopbackFromSckPad 選項到底是什么作用,以及有什么使用限制呢?

注1: 參考手冊里顯示支持loopbackFromSckPad選項的型號有 i.MX RT1040/1050/1060/1064/1180/500

注2: 參考手冊里沒有提及支持loopbackFromSckPad選項的型號有 i.MX RT1010/1015/1020/1024/1160/1170/600

一、為什么存在Read Strobe?

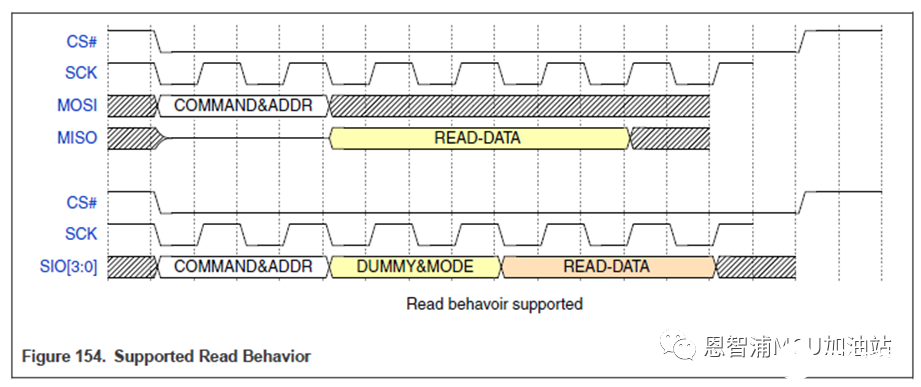

對于串行 SPI 接口存儲器,FlexSPI 外設主要支持如下兩種讀數據時序:一是所謂的經典 SPI 模式,IO0 (MOSI) 專用于發送命令和地址,IO1 (MISO) 專用于接收數據(圖中上面的時序)。二是 Multi-I/O SPI 模式,SIO[n:0] 一起用于發送命令地址以及接收數據(圖中下面的時序)。

顯然經典 SPI 模式下 IO[1:0] 是單向的,而 Multi-I/O SPI 模式下,SIO[n:0] 是雙向的。當 SIO 用于雙向傳輸時,過程中必然存在引腳方向切換,而 FlexSPI 外設在處理 SIO 方向切換時,無法做到零等待周期讀取數據,這就是為什么 Multi-I/O SPI 讀時序中總是會存在 Dummy 周期。

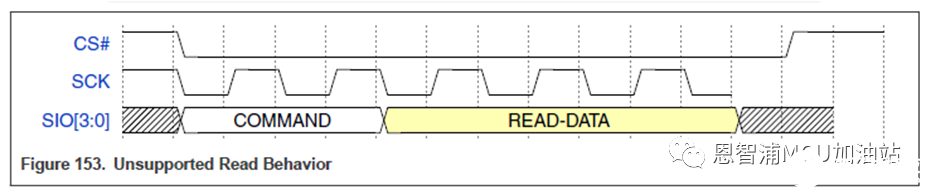

因為 Dummy 周期的存在,FlexSPI 外設內部實際上有一個 Read Strobe 信號(即 DQS)來控制數據的選通性(即什么時候開始數據有效,將數據存入內部 FIFO)。更直白點說,Read Strobe 信號的存在就是由于 FlexSPI 外設無法支持如下這種情況的讀時序(下圖中 COMMAND 實際應為 COMMAND ADDR)。

二、FlexSPI內部Read Strobe設計

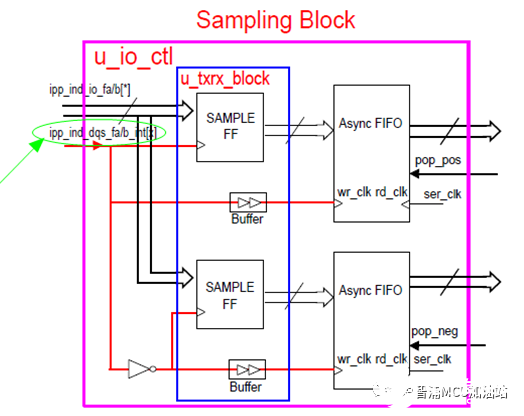

在i.MX RT參考手冊里有如下 FlexSPI 前端采樣單元框圖,其中 ipp_ind_dqs_fa/b_int[x] 即是 Read Strobe 信號,它控制著 FIFO 中實際數據的存儲。

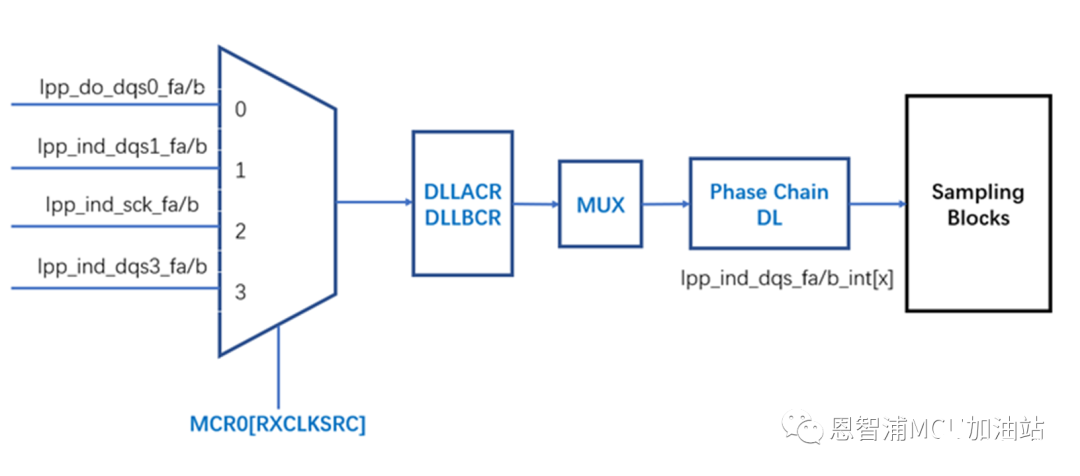

ipp_ind_dqs_fa/b_int[x] 信號共有四種來源,最原始的信號源由 FlexSPI->MCR0[RXCLKSRC] 選擇,中間可能還會經過 DLLxCR 單元(這部分以后會另寫文章單獨介紹)、Phase Chain 單元做處理,然后送到采樣單元里。

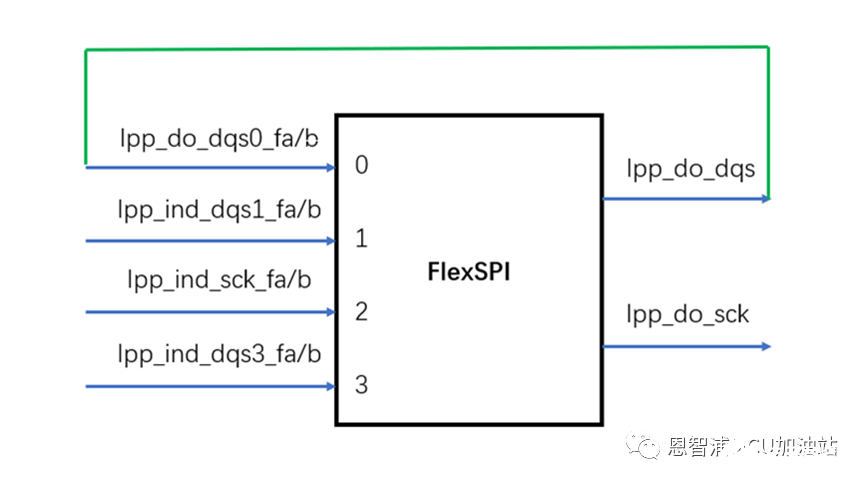

下圖是 FlexSPI->MCR0[RXCLKSRC] = 0 的情況,此時 Read Strobe 經由 ipp_do_dqs0_fa/b 純內部 loopback 回來,沒有經過任何延遲單元。這種配置一般僅用于經典 SPI 傳輸模式(低速 60MHz SDR 場合),適用低容量 SPI NOR / EEPROM,這時候 FlexSPI DQS Pad 可用作其它功能或者 GPIO。

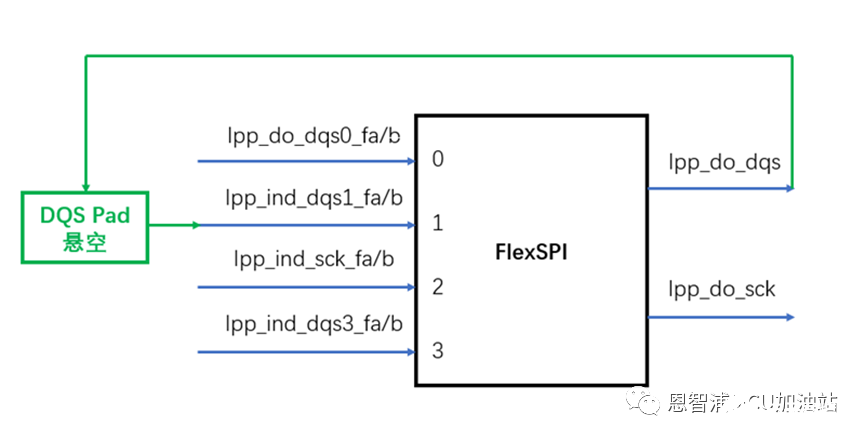

下圖是 FlexSPI->MCR0[RXCLKSRC] = 1 的情況,此時 Read Strobe 經由懸空的 DQS 引腳 ipp_do_dqs1_fa/b 再 loopback 回來,此時有了 DQS 引腳繞一圈的延遲。這種配置可用于 Multi-I/O SPI 傳輸模式(較高速 133MHz SDR 場合),適用不含 DQS 引腳的大容量 QuadSPI NOR Flash,但是 FlexSPI DQS Pad 需要懸空。

注: 有一篇舊文《使能串行NOR Flash的DTR模式》跟這種配置相關,這時候 dummy cycle 數的設置很關鍵。

下圖是 FlexSPI->MCR0[RXCLKSRC] = 3 的情況,此時 Read Strobe 完全由外部存儲器的 DQS 引腳輸出 ipp_ind_dqs3_fa/b 直通進來。這種配置可用于 Multi-I/O SPI 傳輸模式(最高速 166MHz/200MHz DDR 場合),適用于包含 DQS 引腳的 OctalSPI NOR Flash,這時 FlexSPI DQS Pad 與外部存儲器相連。

注: 我有兩篇舊文《串行NOR Flash的DQS信號功能》、《啟動含DQS的Octal Flash可不嚴格設Dummy Cycle》跟這種配置相關。

三、loopbackFromSckPad選項意義

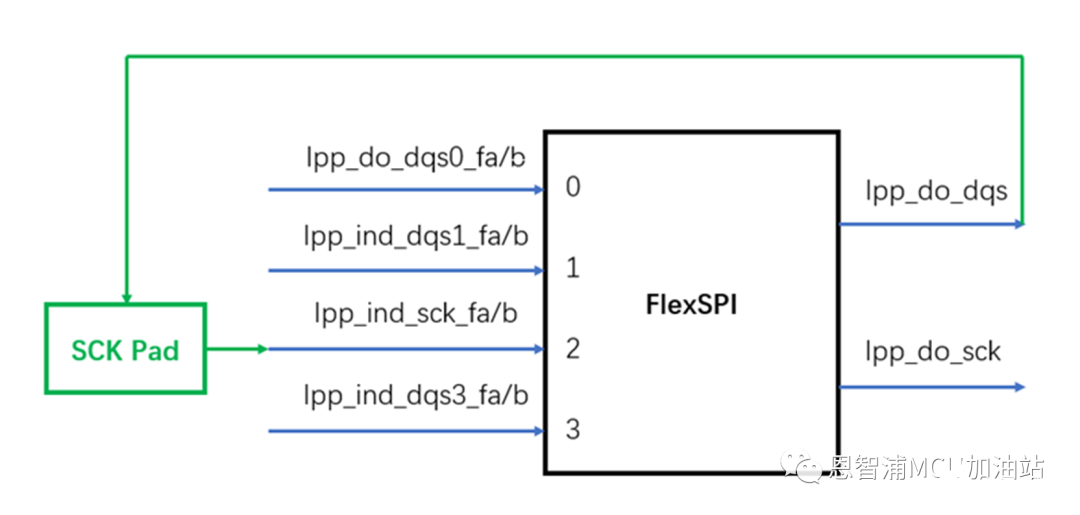

前面鋪墊了那么多,終于來到本文的主題了,即下圖 FlexSPI->MCR0[RXCLKSRC] = 2 的情況,此時 Read Strobe 經由 SCK 引腳 ipp_ind_sck_fa/b 再 loopback 回來,此時有了 SCK 引腳繞一圈的延遲。

這種配置從應用角度與 FlexSPI->MCR0[RXCLKSRC] = 1(即 loopbackFromDqsPad) 差不多,也可用于 Multi-I/O SPI 傳輸模式(較高速 133MHz SDR 場合),適用不含 DQS 引腳的大容量 QuadSPI NOR Flash,但是這時候 FlexSPI DQS Pad 被解放出來了,這也是它的最主要意義。

別小看只是省了一個 DQS 引腳,也許你認為 i.MX RT 有那么多I/O,省一個引腳意義不大,但是如果某些 FlexSPI 引腳組不帶 DQS 信號,你又想配置 FlexSPI 以 60MHz 以上頻率去訪問 Flash,這時候 FlexSPI->MCR0[RXCLKSRC] = 2 選項就會幫上大忙了,見舊文《不支持DQS的FlexSPI引腳組連接串行NOR Flash注意事項》。

四、loopbackFromSckPad使用限制

FlexSPI->MCR0[RXCLKSRC] = 2 選項雖好,但有如下兩個實際使用限制:

存在信號完整性問題:主要出現在 SCK 頻率過高或者板級 PCB 上 SCK 信號走線過長時。

SCK自由運行模式下不可用:對于某些 FPGA 應用,有時需要設置 FlexSPI->MCR0[SCKFREERUNEN] = 1,即 SCK 需要持續給外部設備內部 PLL 提供參考時鐘。

來源:恩智浦MCU加油站

審核編輯:湯梓紅

-

存儲器

+關注

關注

38文章

7514瀏覽量

163994 -

引腳

+關注

關注

16文章

1202瀏覽量

50650 -

SCK

+關注

關注

0文章

7瀏覽量

16141 -

時鐘源

+關注

關注

0文章

93瀏覽量

16002

發布評論請先 登錄

相關推薦

FlexSPI外設如何支持行列混合尋址存儲器

I.MX RT1166 Flashdriver問題如何解決?

FlexSPI和FlexSPI2外設都可以使用BEE嗎?

01:i.MX RT的市場應用和參考解決方案

i.MX RT開發筆記-08 | i.MX RT1062嵌套中斷向量控制器NVIC(按鍵中斷檢測)

RT-Thread & NXP 發布 i.MX RT 系列 BSP 新框架

loopbackFromSckPad選項是什么作用及有什么使用限制

i.MXRT中FlexSPI外設不常用的讀選通采樣時鐘源

探討i.MX RT下FlexSPI driver實現Flash編程時對于中斷支持問題

在i.MX RT10xx使用FlexIO實現XY2-100振鏡控制協議

理解i.MX RT中FlexSPI外設lookupTable里配置訪問行列混合尋址Memory的參數值

i.MX RT中FlexSPI外設不常用的讀選通采樣時鐘源

i.MX RT中FlexSPI外設不常用的讀選通采樣時鐘源

評論