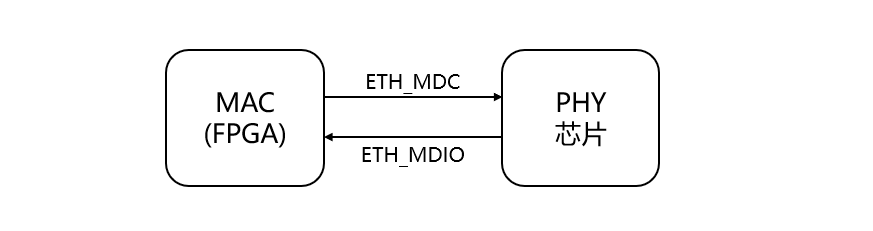

本文開源一個FPGA項目:MDIO接口讀寫測試。以太網(wǎng)通信模塊主要由 MAC (Media Access Control)控制器和物理層接口 PHY (Physical Layer)兩部分構成。其中,MAC控制器和PHY可以整合到同一芯片內,也可以分開,即MAC控制器由FPGA實現(xiàn),PHY由以太網(wǎng)芯片實現(xiàn)。PHY芯片內部寄存器數(shù)據(jù)讀寫是通過MDIO接口實現(xiàn)的,可以對PHY芯片工作模式進行配置并獲取PHY芯片工作狀態(tài)。

01PHY芯片

PHY芯片發(fā)送數(shù)據(jù)時,將MAC控制器發(fā)來的數(shù)據(jù)轉化為串行數(shù)據(jù)流,按照物理層編碼規(guī)則把數(shù)字信號轉化為模擬信號發(fā)出去,接收數(shù)據(jù)反之。

另外,PHY芯片具有自協(xié)商功能。當連接好網(wǎng)線時,PHY芯片會自動檢測對端設備,并通過協(xié)商確定連接速度、雙工模式等。最終確定兩個設備同時支持的最大數(shù)據(jù)傳輸速度和最佳雙工模式。

PHY地址

本文以YT8511 PHY芯片為例。其PHY地址由LED_ACT和RXD[1:0]決定。PHY地址一共有5位,高2位固定為0,LED_ACT和RXD[1:0]表示低3位,可以通過硬件電路進行配置。即地址范圍從00001到00111。

復位

PHY芯片支持軟硬件復位,硬件復位是通過將ETH_RST_N引腳拉低10ms實現(xiàn),軟件復位是通過向地址0x00寄存器的bit[15]寫入1進行復位,復位完成后,該位會自動清零。

寄存器

YT8511共有22位寄存器,常用的就只有控制寄存器、基本狀態(tài)寄存器、和PHY芯片特定狀態(tài)寄存器:

控制寄存器用于控制芯片復位、內部回環(huán)模式、選擇網(wǎng)速、自協(xié)商等功能;

基本狀態(tài)寄存器用于獲取PHY芯片自協(xié)商狀態(tài)、連接狀態(tài);

PHY芯片特定狀態(tài)寄存器用于獲取PHY芯片連接速度。

02MDIO接口

MAC和PHY芯片之間有一個配置接口,F(xiàn)PGA通過MDIO接口對PHY芯片內部寄存器進行配置,一般來講PHY芯片在默認寄存器配置下就可以正常工作。

MDIO接口也被成為SMI接口,即串行管理接口。具體包括時鐘(ETH_MDC)和數(shù)據(jù)輸入輸出(ETH_MDIO)信號接口。其中,時鐘信號頻率應低于12.5Mhz。

通信協(xié)議

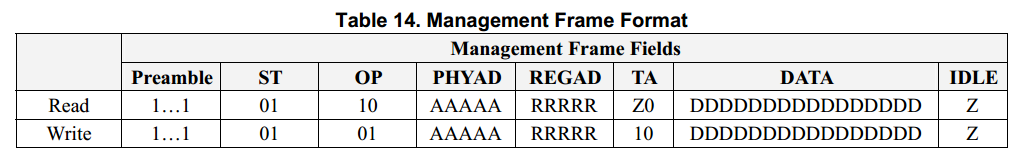

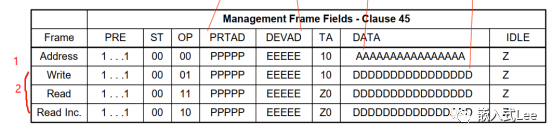

MDIO接口通信協(xié)議如上圖所示,其中:

Preamble :32位前導碼,用于同步PHY芯片;

ST :2位幀開始信號;

OP :2位操作碼,讀10,寫01;

PHYAD :5位PHY地址,用于確定與那個PHY芯片進行通信;

REGAD :5位寄存器地址;

TA (Turnaround):2位轉向。在讀命令中,MDIO在此時由MAC驅動改為PHY驅動,在第1位,MDIO引腳為高阻狀態(tài),第2位,PHY將MDIO引腳拉低,準備發(fā)送數(shù)據(jù);在寫命令中,不需要MDIO方向發(fā)生變化,MAC固定輸出10,隨后開始寫入數(shù)據(jù);

DATA :16位數(shù)據(jù);

IDLE :空閑狀態(tài),此時MDIO為無源驅動,處于高阻狀態(tài),但一般用上拉電阻使其上拉至高電平。

讀時序

MDIO接口讀時序如上圖所示,以讀取0x00地址下寄存器數(shù)據(jù)為例。整個讀操作過程的MDC時鐘由MAC驅動,同時MAC驅動MDIO引腳輸出前導碼+幀開始+操作碼+PHY地址+寄存器地址,隨后MDIO引腳切換至PHY驅動。在第一個TA位,MDIO引腳為高阻狀態(tài),第二個TA位為低電平,表示PHY芯片成功響應,并且接下來會輸出16位寄存器數(shù)據(jù);而如果第二個TA位處于高電平,則PHY芯片響應失敗,有可能PHY地址不正確或者其它時序的錯誤。

需要注意的是,PHY在MDC時鐘的上升沿采集數(shù)據(jù),為保證數(shù)據(jù)的穩(wěn)定傳輸,MAC在MDC的下降沿更新MDIO引腳的數(shù)據(jù)。當MDIO引腳切換至PHY驅動時,MDIO數(shù)據(jù)在MDC時鐘的下降沿更新,因此MAC在MDC時鐘的上升沿采集數(shù)據(jù)。在讀操作結束后,MAC將MDIO引腳輸出高阻,此時MDIO引腳的外部上拉電阻會將MDIO引腳拉高,此時MDIO接口處于空閑狀態(tài)。

寫時序

MDIO接口寫時序如上圖所示,以往0x00地址下寄存器寫入0x1340為例。在整個寫操作過程中,MDC時鐘和MDIO引腳一直由MAC端驅動,按照MDIO接口寫通信協(xié)議開始傳輸數(shù)據(jù)。需要注意的是,PHY在MDC時鐘的上升沿采集數(shù)據(jù),為保證數(shù)據(jù)的穩(wěn)定傳輸,MAC在MDC的下降沿將數(shù)據(jù)更新至MDIO引腳。在寫操作結束后,MAC將MDIO引腳輸出高阻,此時MDIO引腳的外部上拉電阻會將MDIO引腳拉高,此時MDIO接口處于空閑狀態(tài)。

03實現(xiàn)功能

本文開源的MDIO讀寫模塊實現(xiàn)的功能主要是:FPGA通過MDIO接口每隔一定時間循環(huán)讀取PHY芯片各個寄存器的值,并通過MDIO接口對PHY芯片進行軟復位。其中,mdio_dri實現(xiàn)了MDIO接口數(shù)據(jù)讀寫驅動,mdio_ctrl實現(xiàn)了MDIO讀寫控制功能。使用Vivado軟件仿真結果如下圖所示:

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603912 -

接口

+關注

關注

33文章

8614瀏覽量

151304 -

Mac

+關注

關注

0文章

1107瀏覽量

51520 -

PHY

+關注

關注

2文章

304瀏覽量

51770 -

MDIO

+關注

關注

0文章

13瀏覽量

11218

發(fā)布評論請先 登錄

相關推薦

通過MDIO接口管理PHY芯片的驗證設計方案

基于DWC_ether_qos的以太網(wǎng)驅動開發(fā)-MDIO驅動編寫與測試

請問C6748芯片中MDIO的讀寫速率分別最大是多少?

請教關于c6748的MDIO接口讀寫phy的問題

ADSP 21489使用ami接口與fpga連接如何編寫測試程序進行讀寫驗證

基于ARM和FPGA的環(huán)形緩沖區(qū)接口設計方案

【正點原子FPGA連載】 第二十四章MDIO接口讀寫測試實驗-領航者ZYNQ之FPGA開發(fā)指南

【正點原子FPGA連載】 第二十四章MDIO接口讀寫測試實驗-領航者ZYNQ之FPGA開發(fā)指南

基于FPGA的MDIO接口邏輯設計

應對多樣化數(shù)字接口測試挑戰(zhàn)的解決方案——基于可編程FPGA的測試

應對多樣化數(shù)字接口測試挑戰(zhàn)的解決方案——基于可編程FPGA的測試儀器

多樣化數(shù)字接口測試挑戰(zhàn)的解決方案——基于可編程FPGA的測試儀器

基于FPGA的MDIO接口讀寫測試方案

基于FPGA的MDIO接口讀寫測試方案

評論