DVFS 即動態電壓頻率調整,針對 SOC主頻的不同,需要動態調整 SOC 的 Core Power。通過調整內核供電電壓,實現SOC主頻的調整。

例如:

SSD210在Core Power=0.9V時,主頻為800MHz。

在Core Power=1.0V時,主頻為1GHz

但是無論主頻軟件設置 800MHz/1GHz,都需要 Core Power=1.0V 啟動(SSD210)。

那么硬件電路如何設計調整內核供電呢?

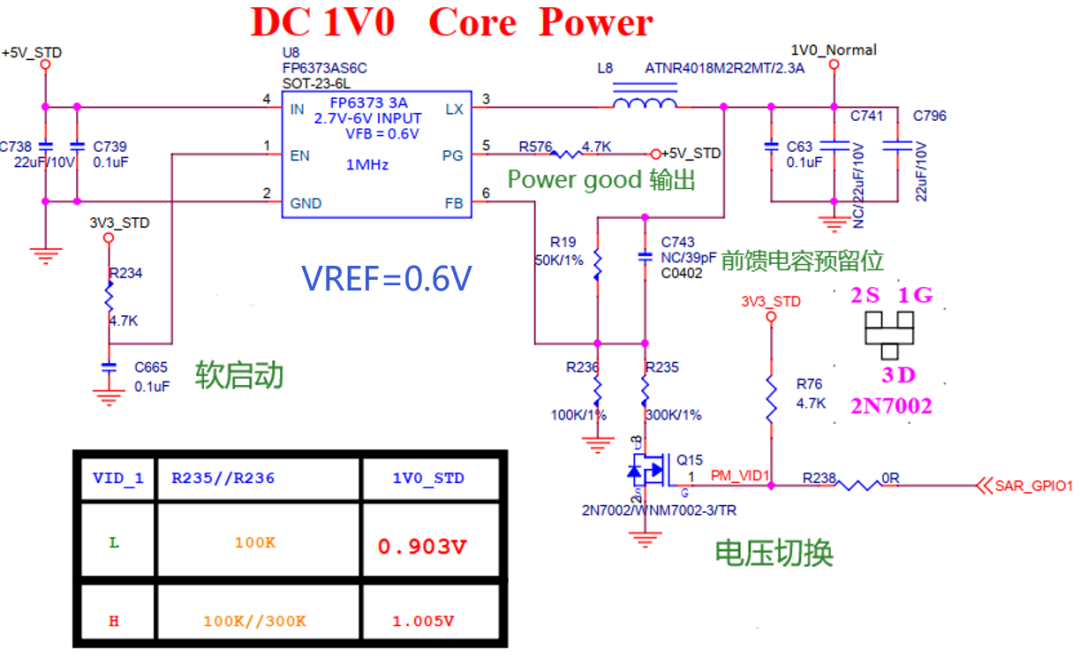

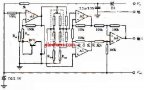

電路圖如下,采用Q15控制反饋電阻,上電時,Q15導通,此時反饋電壓等于輸出電壓在50KΩ和75KΩ( 100K并聯300K )分壓值,此時電路輸出1V即提供內核啟動電壓。

當系統工作后,比如系統想要 降低功耗 ,或者在 高溫情況下,需要動態調壓,降低芯片主頻以減少發熱。只需要通過使用IO輸出低電平,使Q15截止;那么,反饋電壓等于輸出電壓在50KΩ與100KΩ分壓值,便可調整Core的供電電壓為0.9V,從而將SOC的主頻降低為0.8MHz。

其中C665為緩啟動電容。PG管腳為Power_good管腳(管腳為開漏輸出,所以需要加上拉電阻),芯片正常輸出電壓后輸出高電平,上圖的PG管腳未連接到SOC的IO做檢測。C743為前饋電容(NC是不貼裝的意思),目的是為了 調整芯片輸出響應速度 ,預留出來 方便后續調試 。

-

電路圖

+關注

關注

10347文章

10721瀏覽量

531054 -

內核

+關注

關注

3文章

1373瀏覽量

40311 -

soc

+關注

關注

38文章

4173瀏覽量

218420 -

硬件電路

+關注

關注

39文章

243瀏覽量

29246

發布評論請先 登錄

相關推薦

請問對C6678內核供電,不采用支持SmartReflex技術類型的供電,比如只是簡單的進行1V內核電壓供電,會產生什么后果?

為聯網專用集成電路供電的高功率6+1穩壓器參考設計

基于硬件虛擬化的安全的內核監控模型

AD9510:1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,8路輸出

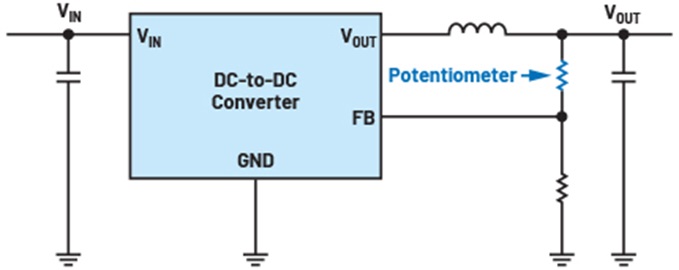

工程師指南:如何動態調整合適的輸出電壓

硬件電路如何設計調整內核供電

硬件電路如何設計調整內核供電

評論