CML即Current Mode Logic,也就是電流模式邏輯,CML電路主要靠電流驅動,可以說CML是所有高速數據接口形式中最簡單的一種,它的輸入與輸出是匹配好的,從而減少了外圍器件,使用時直接連接就可以,基本上不需要在IC外面做匹配,此特點使單板硬件設計更簡單,單板看起來更簡潔,CML的擺幅較小,功耗比較低。

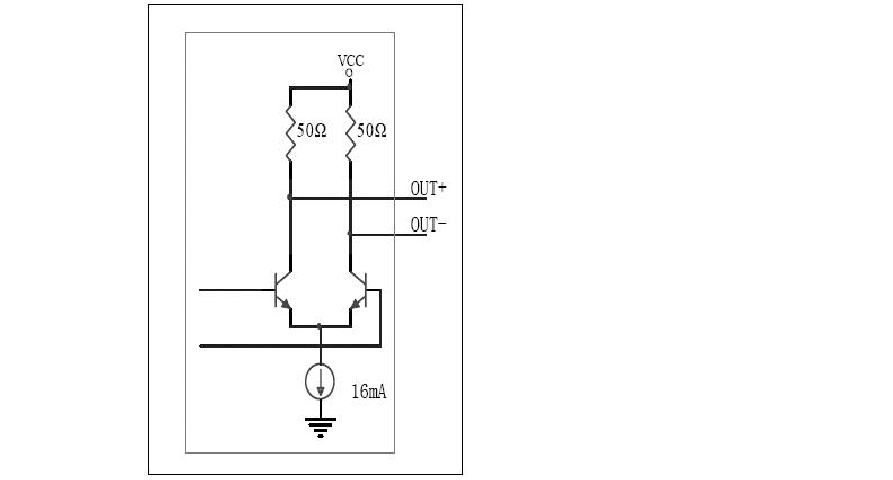

CML輸出結構:

如上圖所示,CML的輸出電路形式是一個差分對,該差分對的集電極電阻為50ohm,輸出信號的高低電平切換是靠共發射極差分對的開關控制的,差分對的發射極到地的恒流源典型值為16mA,假定CML的輸出負載為一50ohm上拉電阻,則單端CML輸出信號的擺幅為VCC~VCC-0.4V。

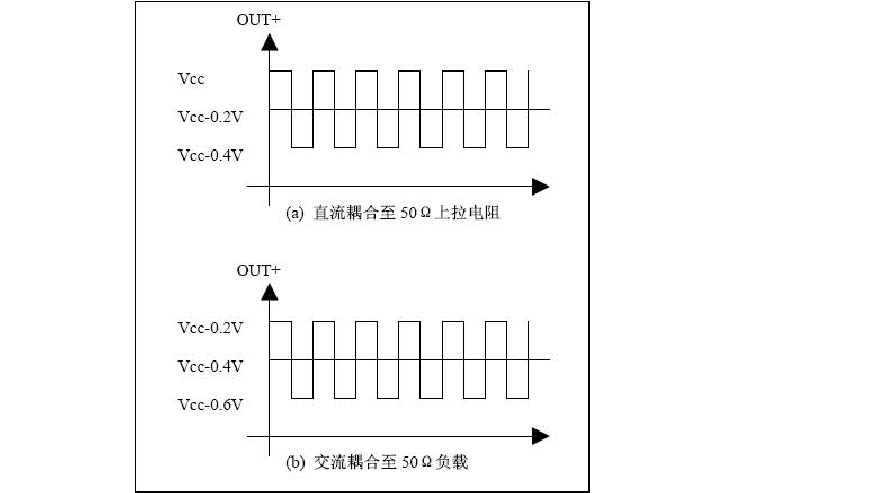

在這種情況下,差分輸出信號擺幅為800mV,共模電壓為VCC-0.2V。若CML輸出采用交流耦合至50ohm 負載,這時的直流阻抗由集電極電阻決定,為50ohm,CML輸出工模電壓變為VCC-0.4V,差分信號擺幅仍為800mV。

CML波形:

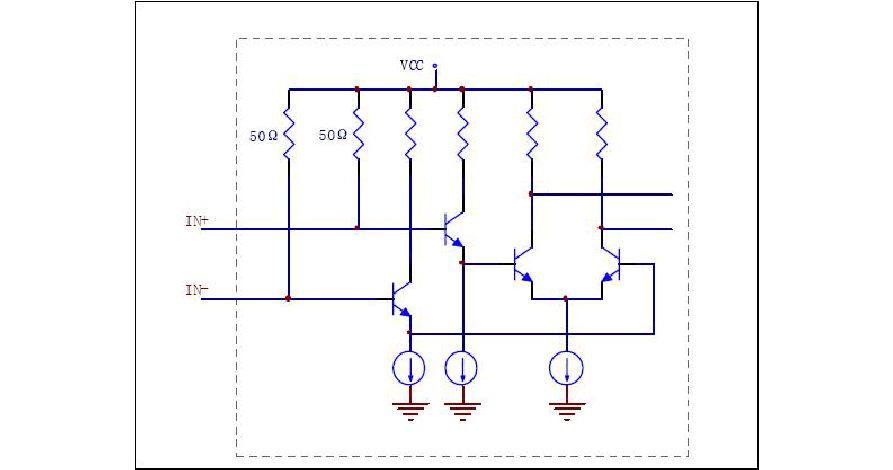

CML的輸入一般都是片內匹配好的,50ohm上拉到VCC,而且大部分是交流耦合。

CML的輸入結構:

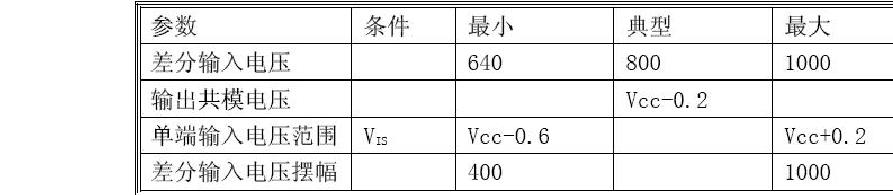

CML的擺幅一般在600mV-100mV之間,典型值為800mV。 CML邏輯參數:

CML的優點是功耗低,速度高,但是驅動能力不如LVPECL,傳輸距離也沒有ECL遠。

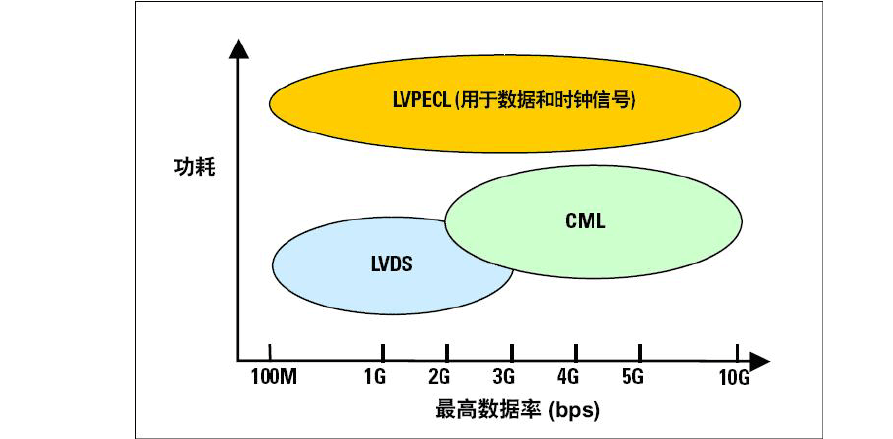

LVPECL/LVDS/CML三種邏輯比較:

-

驅動器

+關注

關注

53文章

8259瀏覽量

146629 -

上拉電阻

+關注

關注

5文章

360瀏覽量

30643 -

共模電壓

+關注

關注

2文章

101瀏覽量

12675 -

Vcc

+關注

關注

2文章

306瀏覽量

36119 -

CML

+關注

關注

0文章

32瀏覽量

19356

發布評論請先 登錄

相關推薦

信號完整性學習筆記

信號完整性設計中的5類典型問題(于博士信號完整性)

聽懂什么是信號完整性

信號完整性學習筆記之CML

信號完整性學習筆記之CML

評論